FPGA学习笔记——SDR SDRAM简介

目录

一、SDRAM基本概念

二、SDRAM存储结构及容量

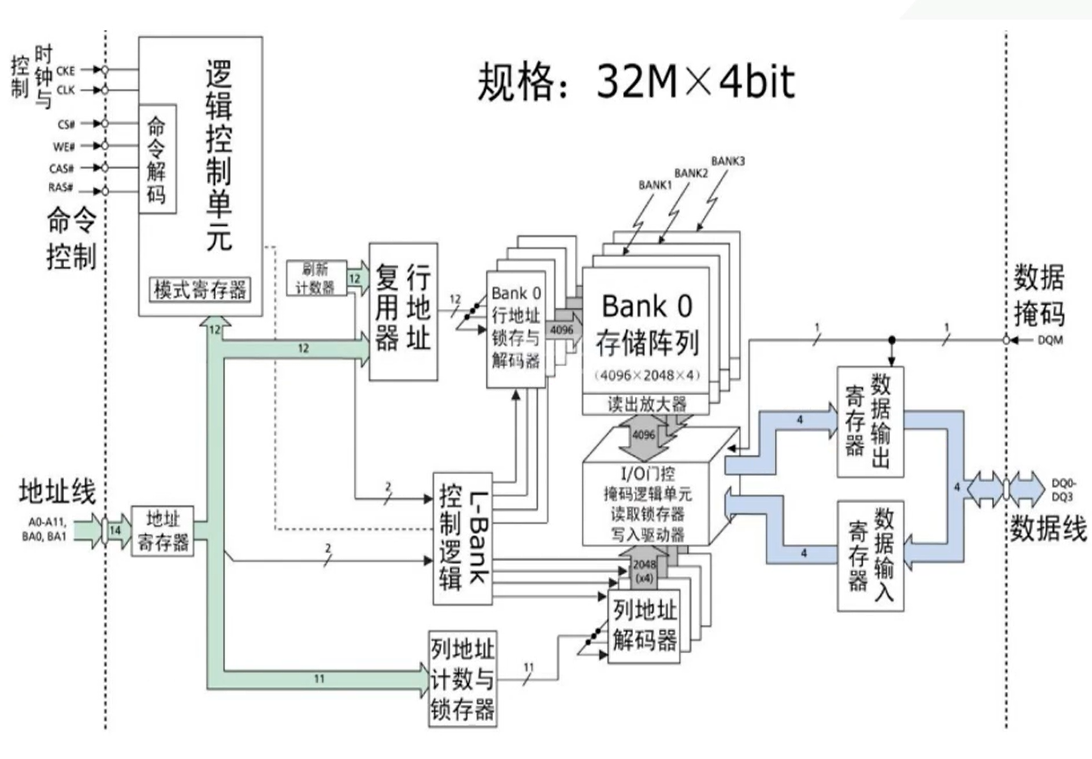

2.1 SDRAM存储结构示意图

2.2 SDRAM容量计算

三、SDRAM功能框图

四、SDRAM主要操作命令

1.Mode Register Set(模式寄存器设置):4'b0000

2.No Operation(空操作):4'b0111

3.Active(激活命令):4'b0011

4.Read(读):4'b0101

5.Write(写) :4’b0100

6.Precharge All Banks(预充电所有Bank):4'b0010

7.Auto Refresh(自动刷新):4'b0001

一、SDRAM基本概念

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。

同步(Synchronous):是指内存工作需要同步时钟,内部命令的发送与数据的传输都以它为基准;

动态(Dynamic):是指存储阵列需要不断的刷新来保证数据不丢失;

随机(Random):是指数据不是线性依次存储,而是自由指定地址进行行数据读写。

空间存储量大、读写速度快以及价格相对便宜等优点使SDRAM在存储界屹立不倒、经久不衰,广泛应用在计算机中。随着时代的不断发展、技术的不断更新。SDRAM使用至今已过数十载,产品更新历经六代,分别是:第一代 SDR SDRAM,第二代 DDR SDRAM,第三代 DDR2 SDRAM,第四代 DDR3 SDRAM,第五代 DDR4 SDRAM,以及最新的DDR5 SDRAM。

这里为什么要刷新,因为SDR SDRAM是用电容来存储数据的,由于电容的容量很小,所以电荷保存的时间有限。为了及时补充漏掉的电荷以避免存储的信号丢失,必须定时地给电容补充电荷,通常将这种操作称为刷新。

由于SDR SDRAM为DRAM,内部的存储都是靠电容进行保存数据,电容的保持数据的时间为64ms,SDR SDRAM每次只能够刷新一行,为了不丢失任何数据,所以要保证64ms内,将所有的行都要刷新一遍。

二、SDRAM存储结构及容量

2.1 SDRAM存储结构示意图

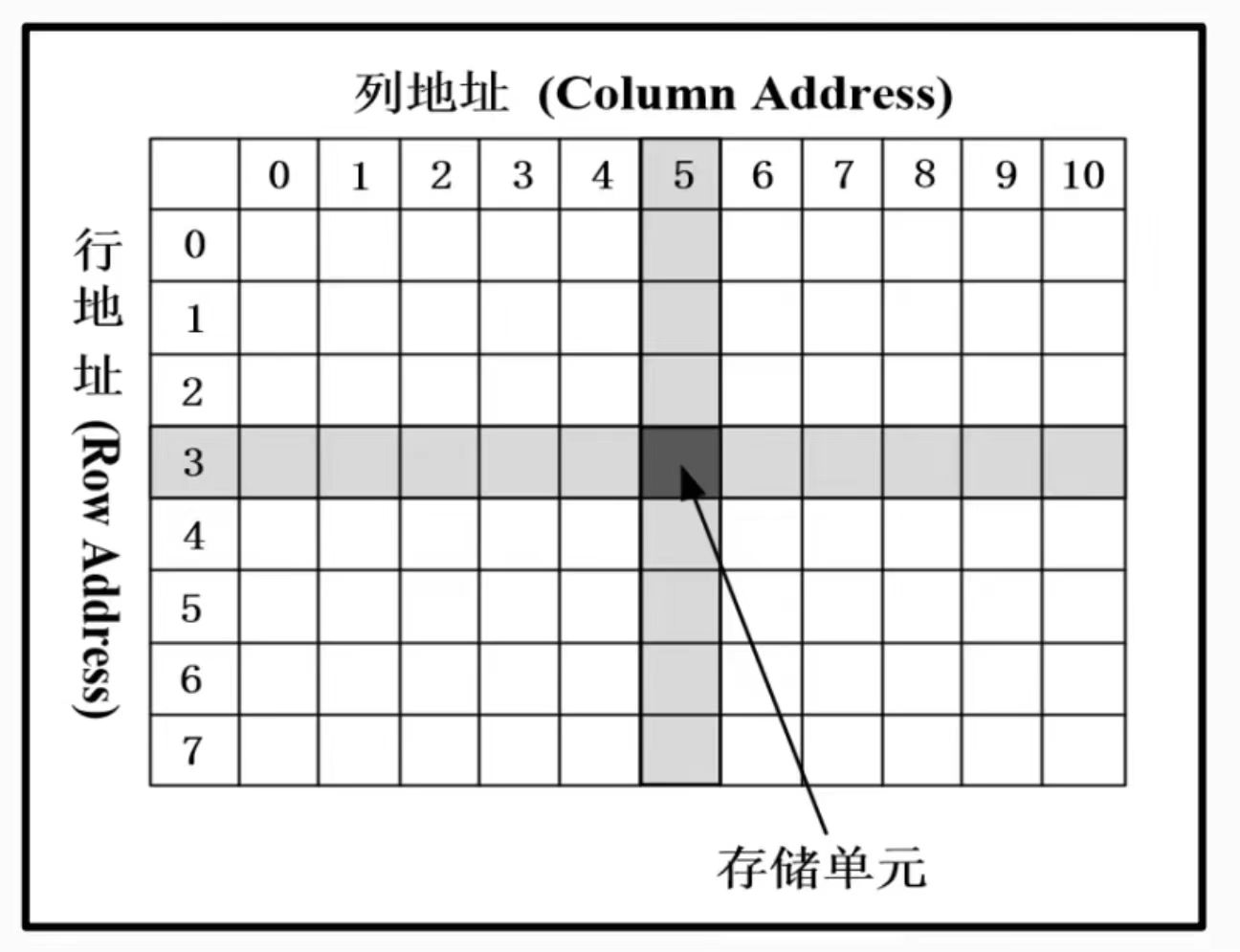

SDRAM的内部是一个存储阵列,我们可以把它想象成一张表格。我们在向这个表格中写入数据的时候,需要先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要地“单元格”,这就是SDRAM寻址的基本原理。(先行后列)

L-Bank:我们将类比于单元格的存储空间称之为存储单元,N(行列个数乘积=行x列)个存储单元构成一个存储阵列,这个存储阵列称之为一个逻辑Bank(Logical Bank,简称L-Bank、Bank)。

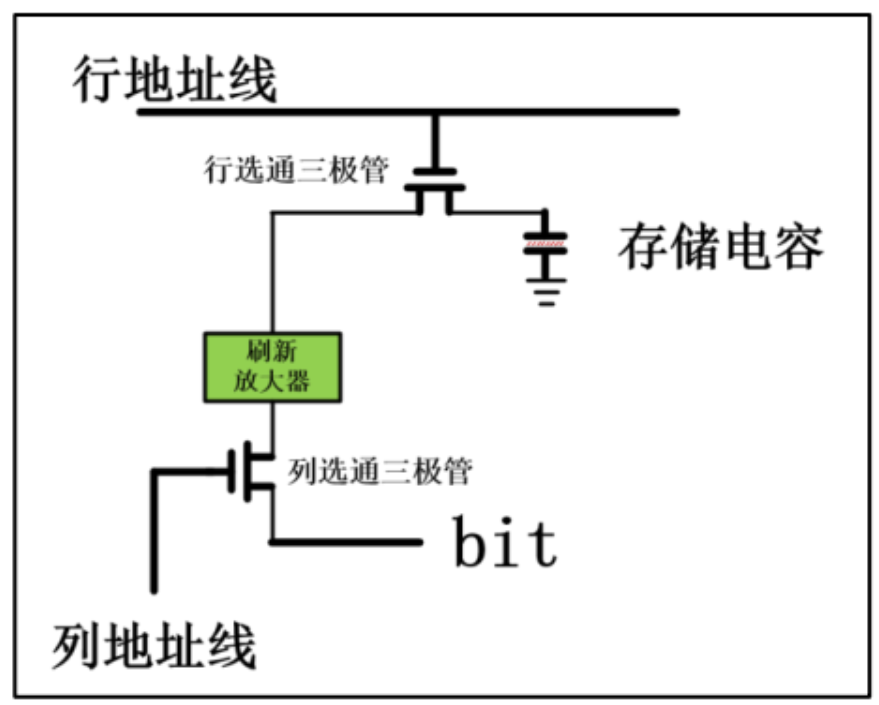

“表格”中的一个单元格是SDRAM的一个存储单元,一个存储单元里可以存放一个或者多个bit数据,其中存放一个bit的存储单元结构入下图所示:

行列地址线被选中后,数据线(bit)直接和电容相连接。当写入时,数据线给电容充放电;读取时,电容将数据线拉高或者置低。

在对SDRAM进行数据存取时,要先确定Bank地址,定位到指定Bank,再依次确定行地址和列地址,选中存储单元,进而进行数据的存取操作,而且一次只能对一个Bank的一个存储单元进行操作。

2.2 SDRAM容量计算

对SDRAM的读写是针对存储单元进行的,一个存储单元的容量等于数据总线的位宽,单位是bit。

那么SDRAM芯片的总存储容量可以用公式计算:

SDRAM总存储容量 = L-Bank 的数量 x 行数 x 列数 x 存储单元的容量(数据线的位宽)

举个例子:

一个SDRAM ,有四个Bank,一个Bank的行地址是A0~A12,列地址是A0~A8,数据线位宽是16bit。那么SDRAM总存储容量是?

SDRAM总存储容量 = 4 x 8192 x 512 x 16 = 4 x 4M x 16bit =16M x 16bit = 256Mbit

三、SDRAM功能框图

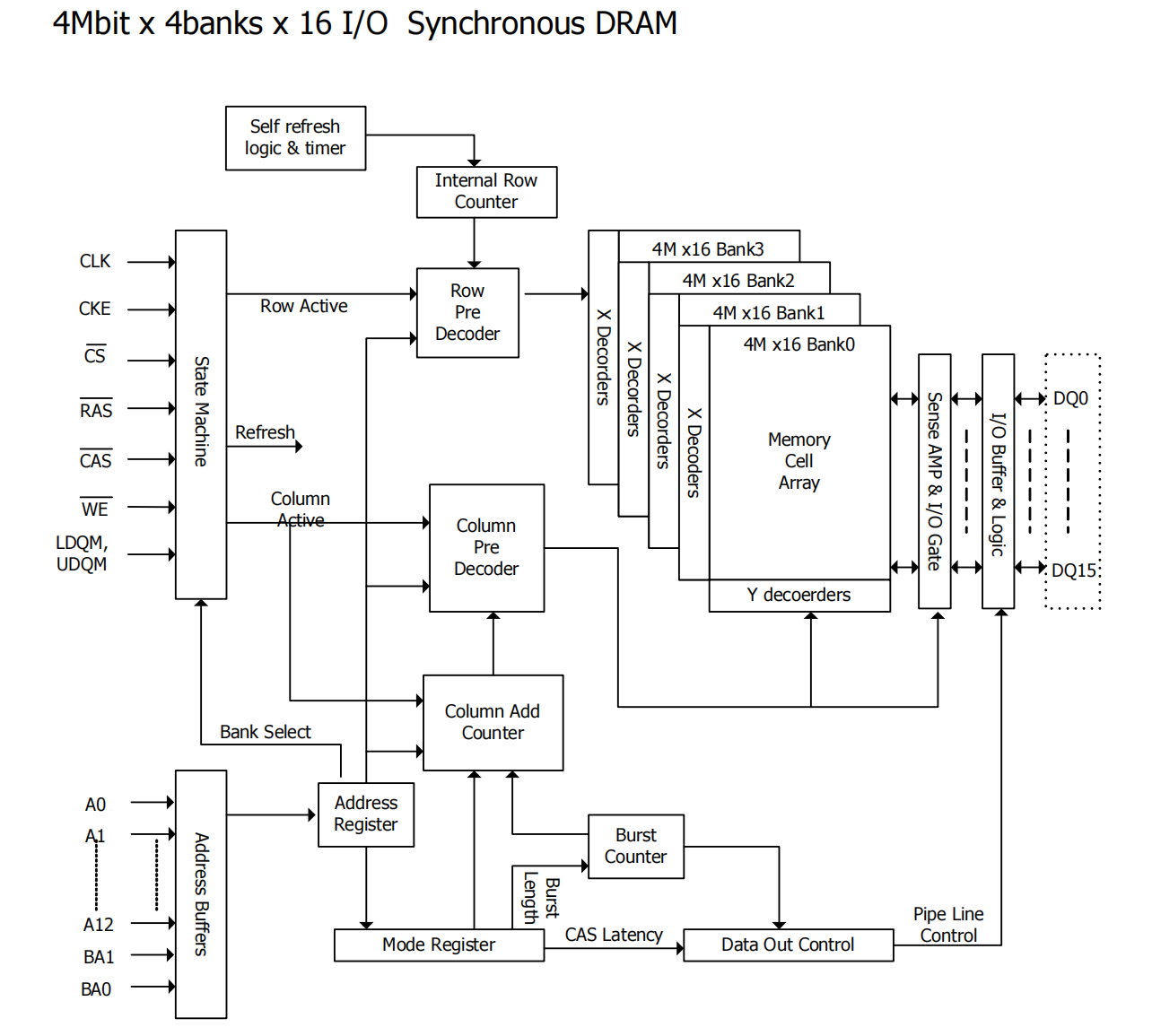

SDRAM内部包含一个逻辑控制单元,其中包含了模式寄存器和命令解码器。外部通过CS#、RAC#、CAS#、WE#以及地址总线向逻辑控制单元输入命令,命令经过命令解码器进行解码后,将控制参数保存到模式寄存器中,逻辑控制单元进而控制逻辑运行。

外部复用的地址总线主要负责传递寻址信息:其输入的行、列地址在逻辑控制单元的协调下,依次经由Bank控制逻辑、行地址复用器及列地址计数锁存器处理,最终通过列地址解码器精确定位目标存储单元,从而完成对指定行列地址的数据读写操作。

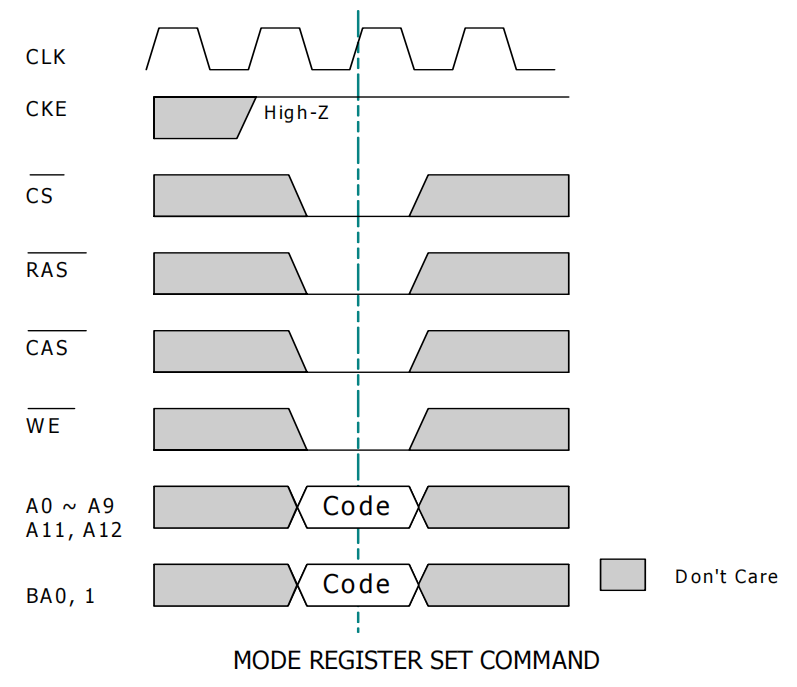

相应的引脚说明:

四、SDRAM主要操作命令

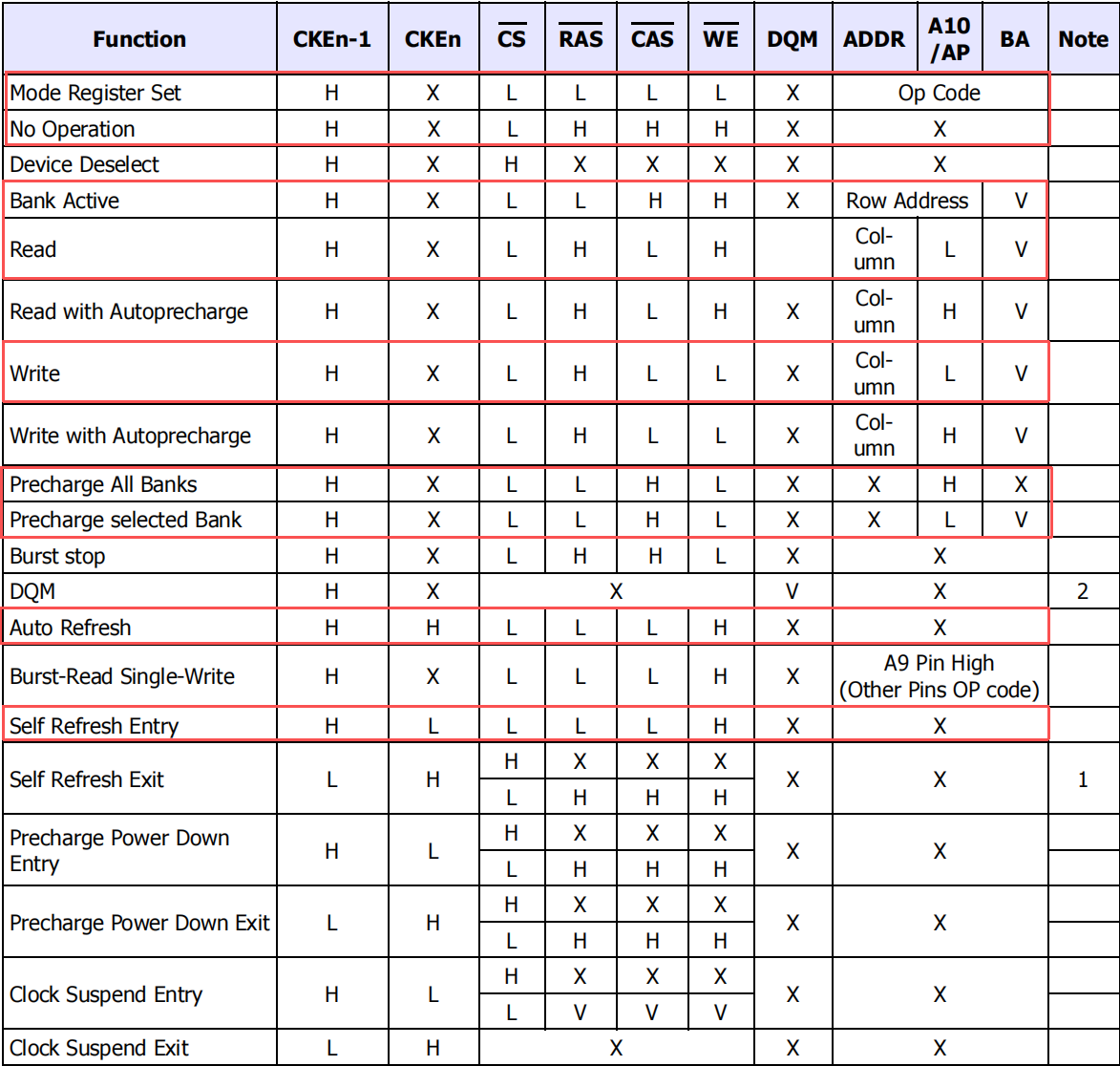

SDRAM的操作都是通过{CS#、RAS#、CAS#、WE#} 四路控制信号构成指令来的, 如图所示:

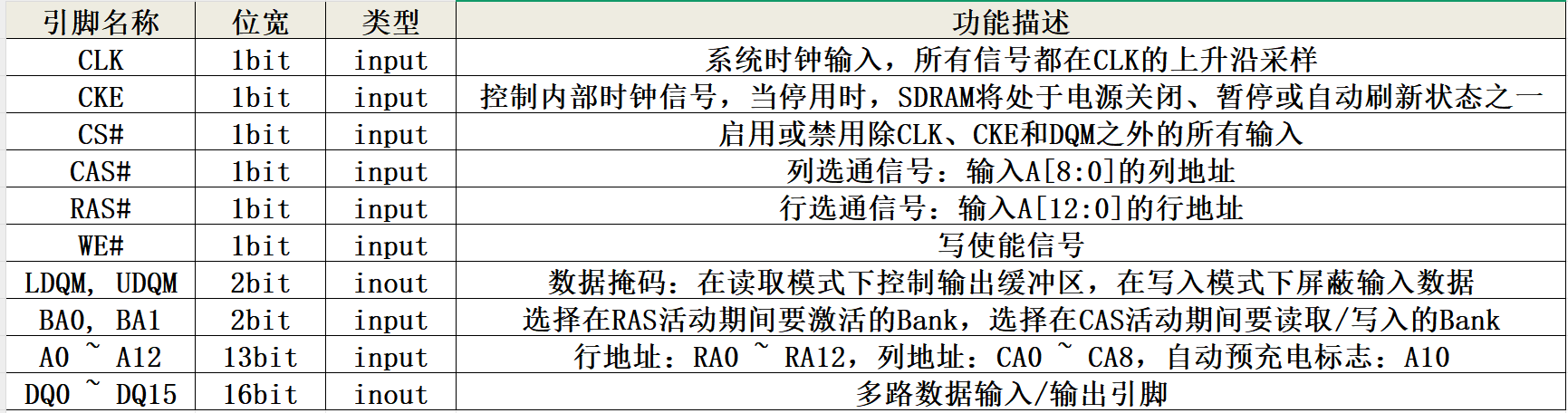

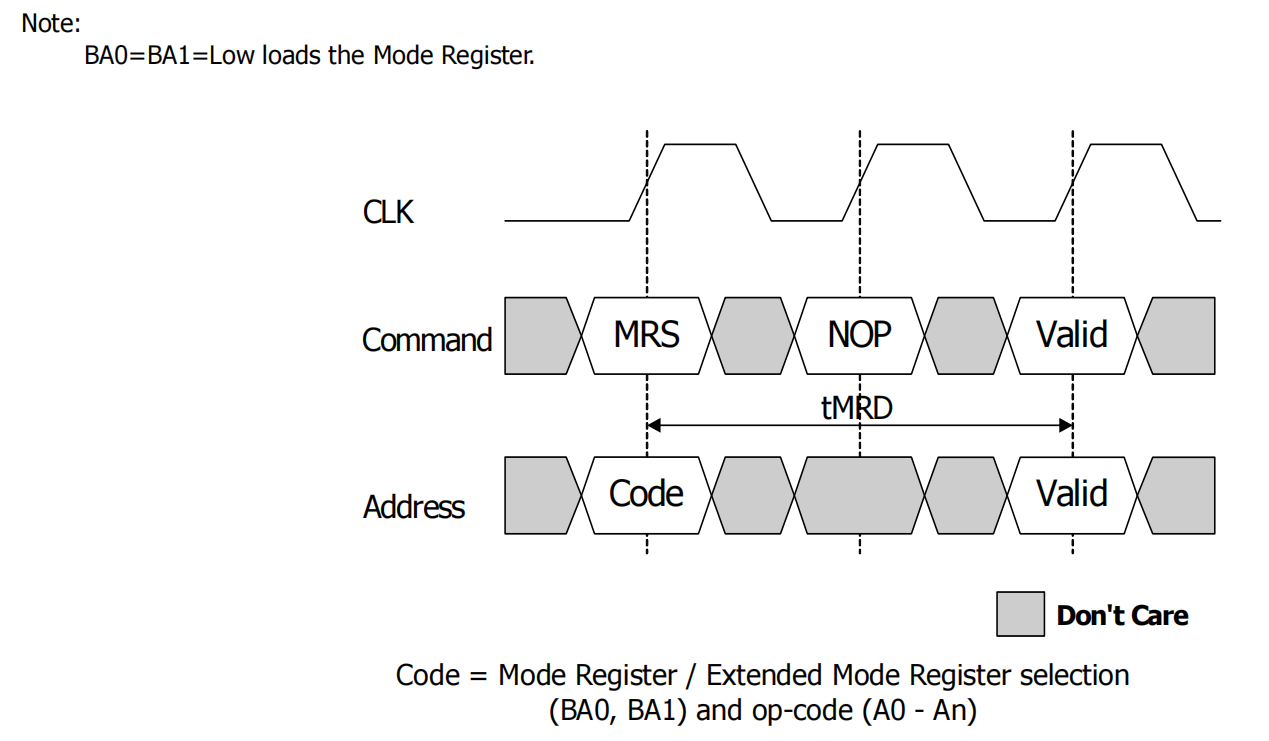

1.Mode Register Set(模式寄存器设置):4'b0000

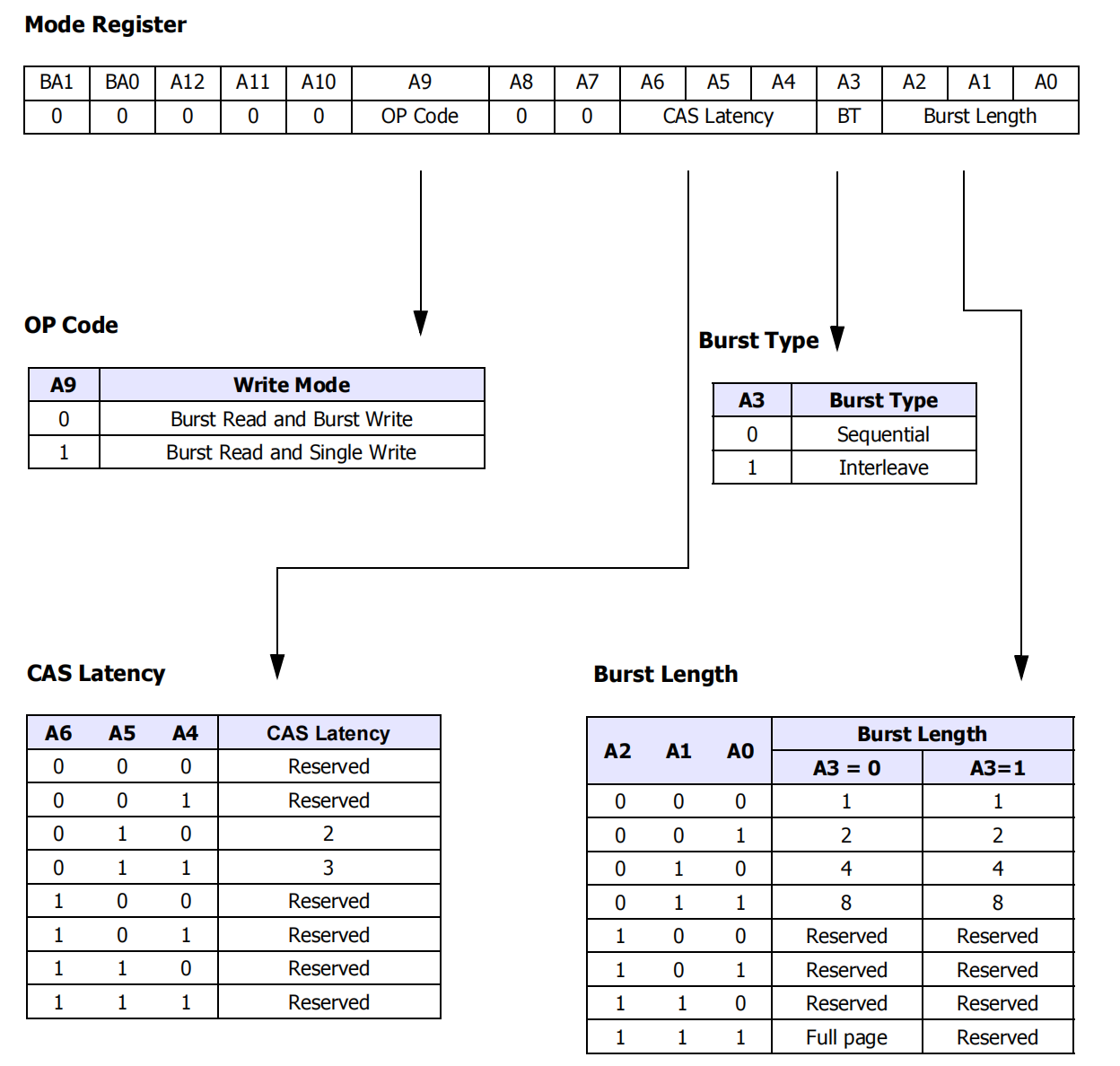

模式寄存器通过地址位进行加载。BA0和BA1用于选择模式寄存器。只有当所有存储库处于空闲状态且没有突发传输正在进行时,才能发出mode Register SET命令,并且在满足tMRD条件之前不能发出后续可执行命令。

时序图:在上升沿进行采样4'b0000

具体的模式配置:

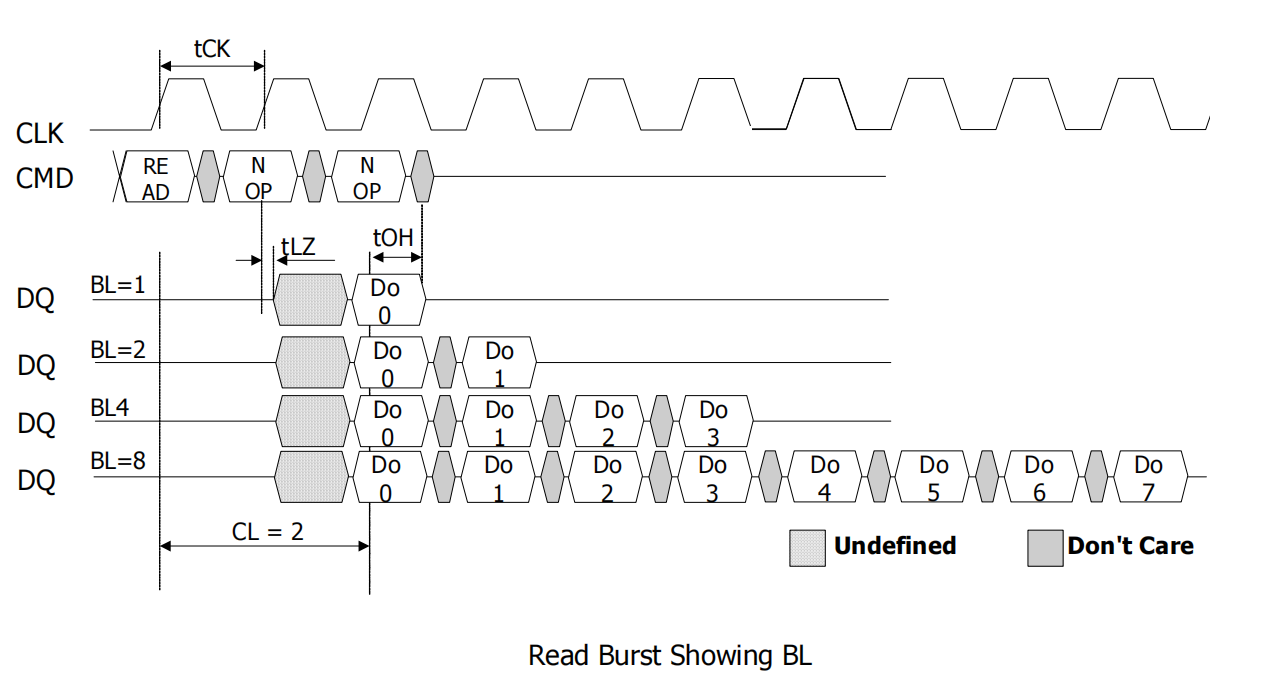

A3:突发类型(Burst Type),当A3=0时,是顺序模式;当A3=1时,是交错模式。(一般都是用顺序模式)

A0~A2:突发长度(Burst Length),根据A3(突发类型)的值,有不同的突发长度,当A3=0时,突发长度有:1、2、4、8、整页;当A3=1时,突发长度有1、2、4、8。(都是bit)

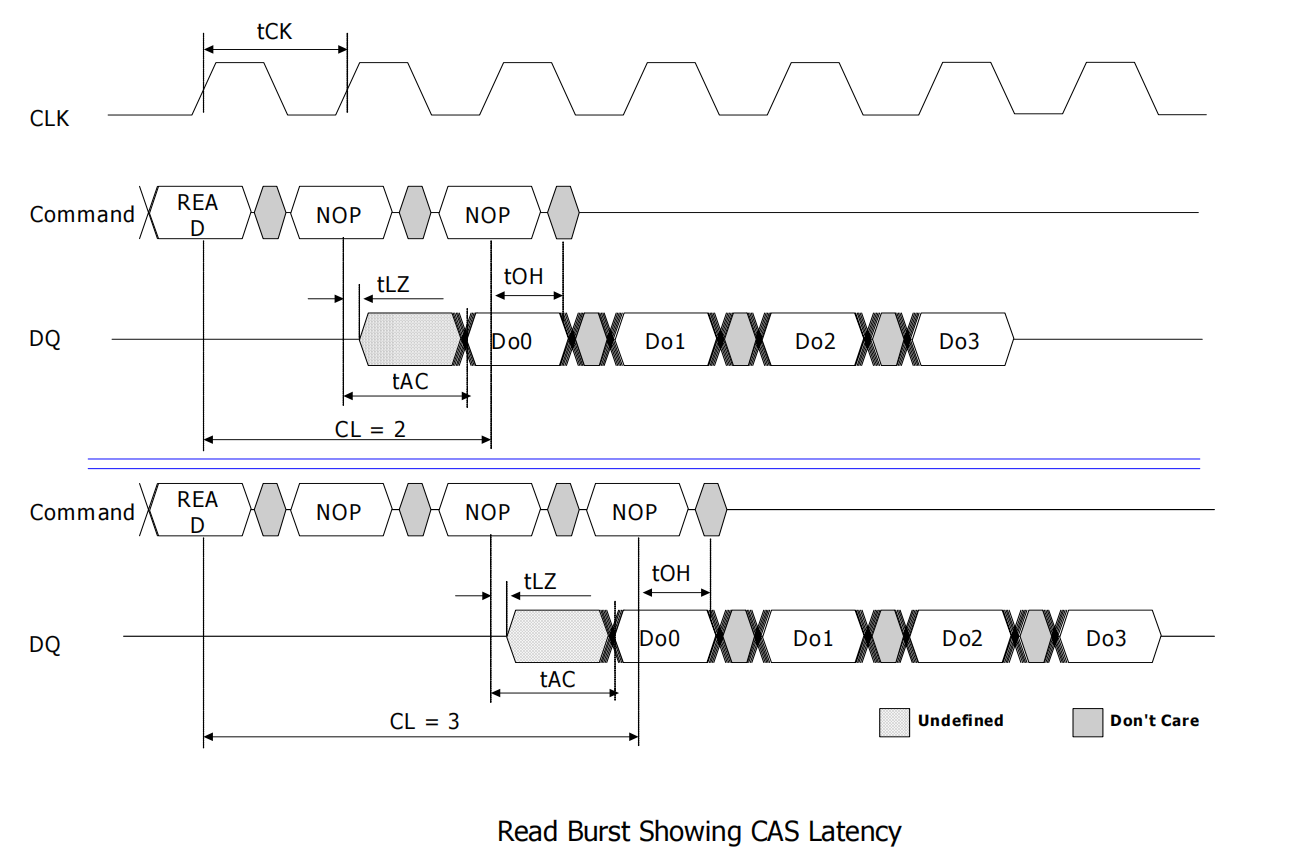

A4~A6:列选通潜伏周期(CAS Latency),这里可以配置有2个周期或者3个周期。

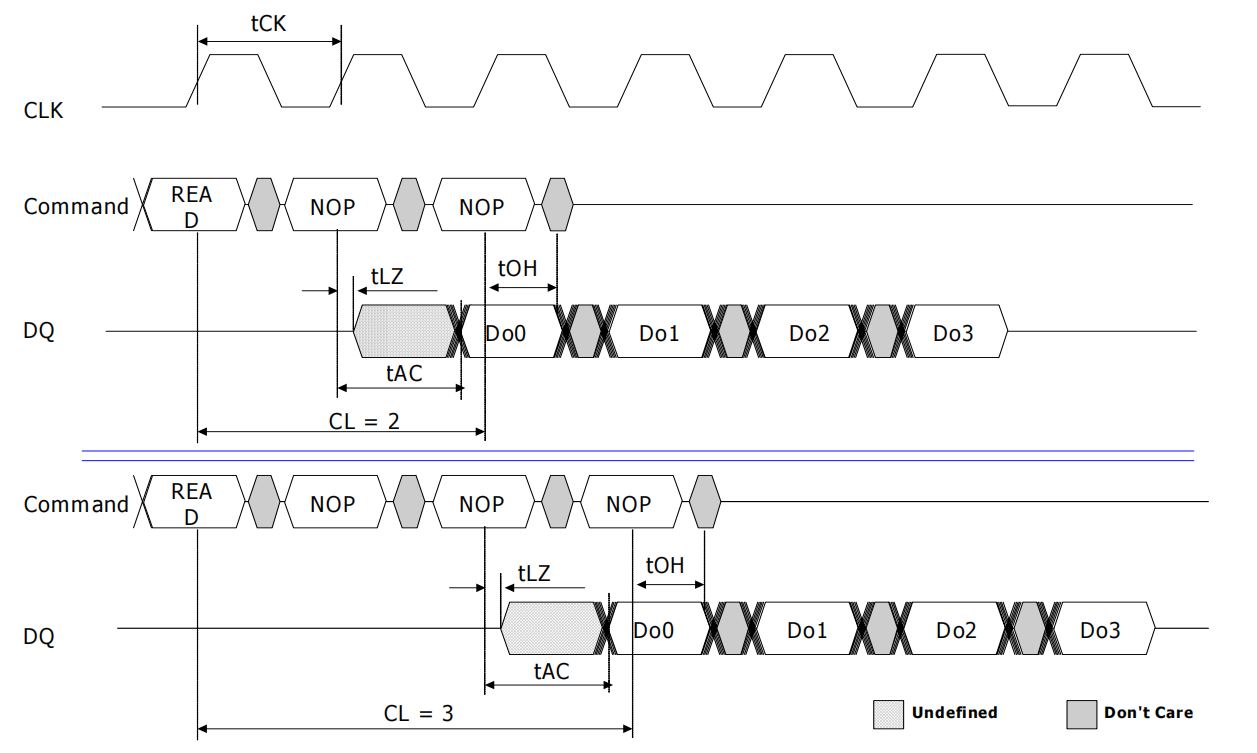

该图是突发长度为4,顺序读取,2个列选通潜伏周期和3个列选通潜伏周期

A9:设置写突发模式(Write Mode),当 A9 = 0 时,通过 A0~A2 (突发长度)配置适用于读和写突发;当A9 = 1时,编程的突发长度适用于读突发,但是写操作不是突发,一次只能写一个数据。

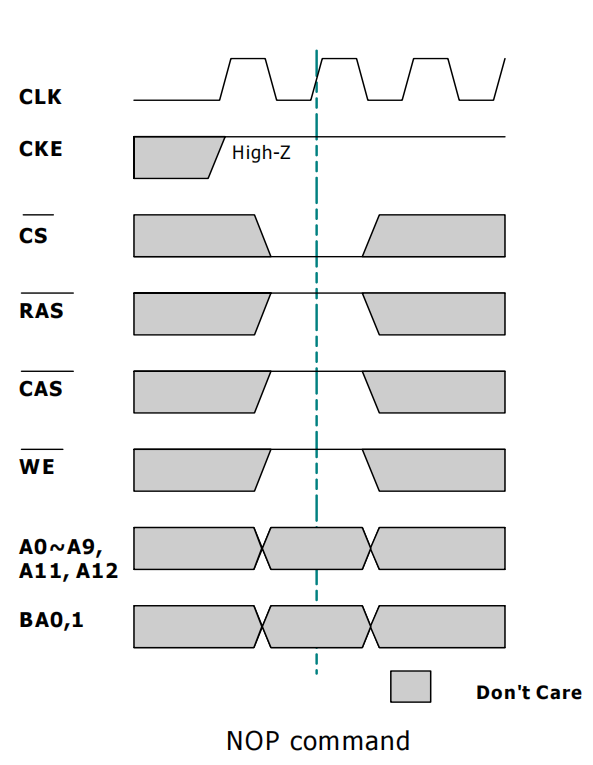

2.No Operation(空操作):4'b0111

NO OPERATION(NOP)命令用于对选定的SDRAM执行NOP操作(CS =低电平,RAS =选中,WE =高电平)。该命令并非执行指令,但内部操作仍会继续。这样可以防止在空闲或等待状态下注册到不必要的指令。正在进行的操作不受影响。

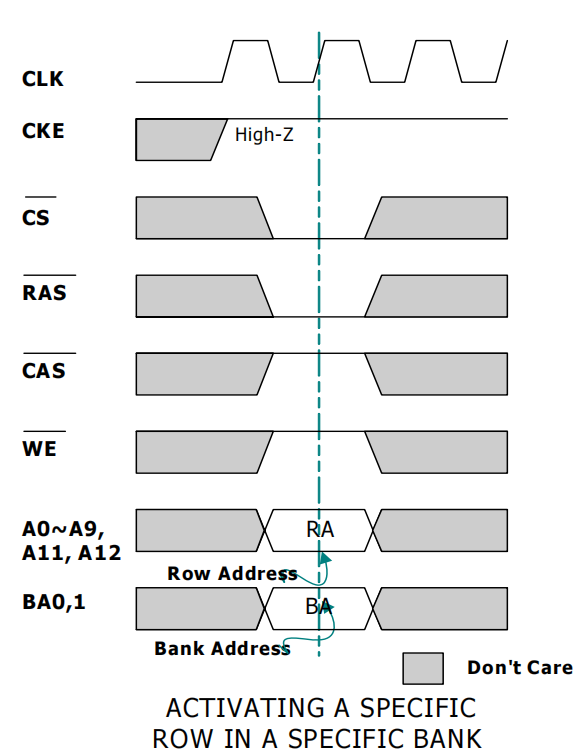

3.Active(激活命令):4'b0011

激活命令用于在后续读取或写入操作中,为特定存储库中的某一行启用访问权限。BA0和BA1输入端的数值用于选择存储库,而A0-A12(或最高地址位)提供的地址则用于选定具体行。该行在激活后将持续保持访问权限,直至对该存储库发出预充电命令为止。

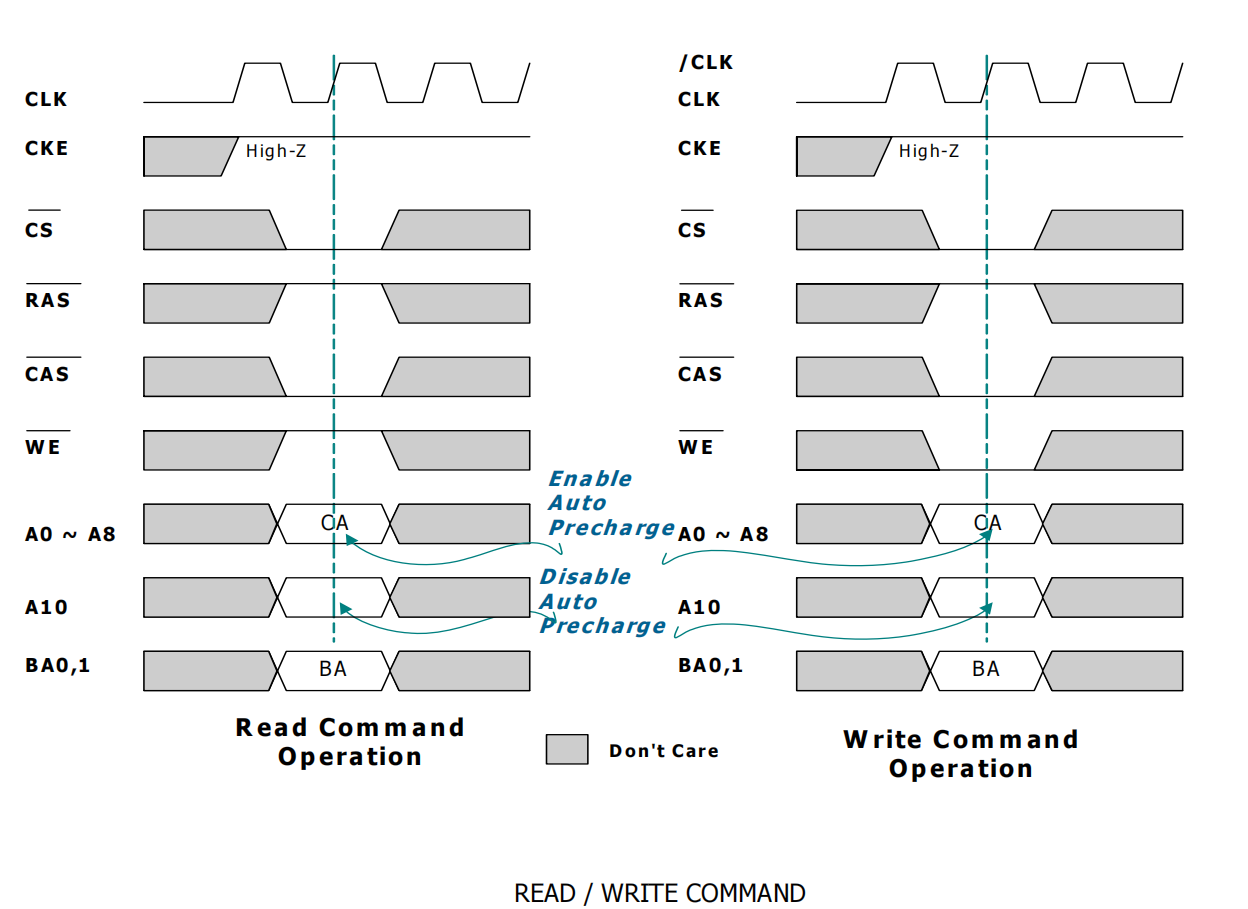

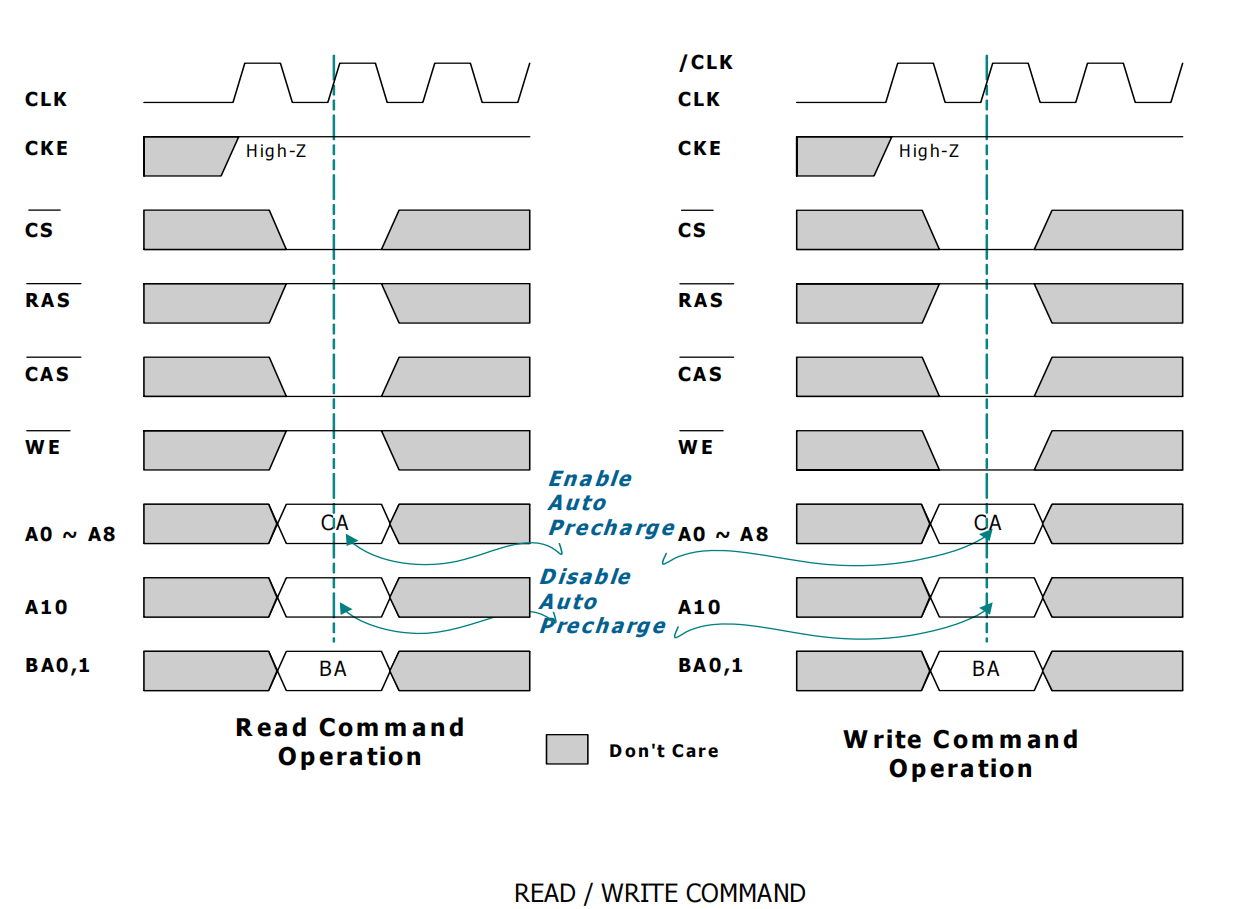

4.Read(读):4'b0101

READ指令用于向当前活动行发起突发读取操作。BA0和BA1的数值用于选择存储库,而地址输入则用于指定起始列位置。A10的数值决定了是否启用自动预充电功能:若选中该功能,被访问行将在读取突发操作结束时完成预充电;若未选中,则该行将保持开放状态以供后续访问。发出READ指令后,有效数据输出单元将在CAS延迟周期内可供读取。

当输入读取指令时,读操作随即启动。在读取指令设置后的周期(/CAS延迟- 1)内,输出缓冲器会切换为低电平有效状态。SDRAM支持突发读取操作,其突发长度可设置为1、2、4或8个时钟周期。突发读取的起始地址由列地址和银行选择地址共同决定,这两个地址均在读取指令设置周期内指定。数据输出将在/CAS延迟指定的时钟周期后开始,该延迟值可设置为2或3个时钟周期。当突发长度为1、2、4或8个时钟周期时,DOUT缓冲器会在连续输出对应长度的数据后,于下一个时钟周期自动切换为高电平有效状态。所有/CAS延迟和突发长度参数必须通过模式寄存器进行配置。

以上就是相对应的时序图。

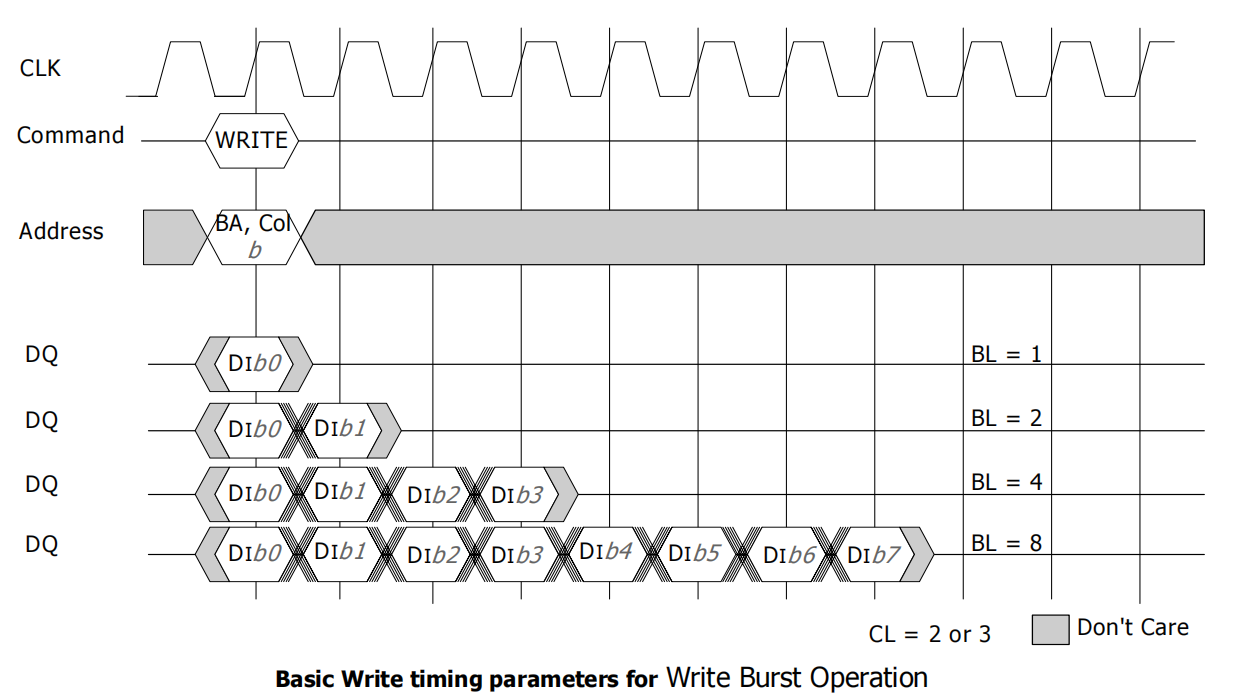

5.Write(写) :4’b0100

WRITE指令用于对当前活动行发起突发写入操作。BA0和BA1的数值用于选择存储库,而地址输入则用于指定起始列位置。A10的值决定了是否启用自动预充电功能:若选中该功能,则在写入突发操作结束时对当前行进行预充电;若未选中,则保持该行开放状态以供后续访问。

在写入突发期间,首个有效数据输入元素将在写入命令触发时同步完成寄存。后续数据元素将在每个连续的正时钟边沿进行寄存。当固定长度突发完成且未触发其他命令时,DQ端口将保持高阻态,此时所有新增输入数据将被忽略。整页突发将持续至终止。任何写入突发的数据均可通过后续写入命令进行截断,而固定长度写入突发的数据可紧接其后立即触发新的写入命令。新写入命令可在前次命令之后的任意时钟周期发出,且与新命令同步提供的数据将直接应用于该新命令。

其他相应的情况,可以在数据手册去查看。

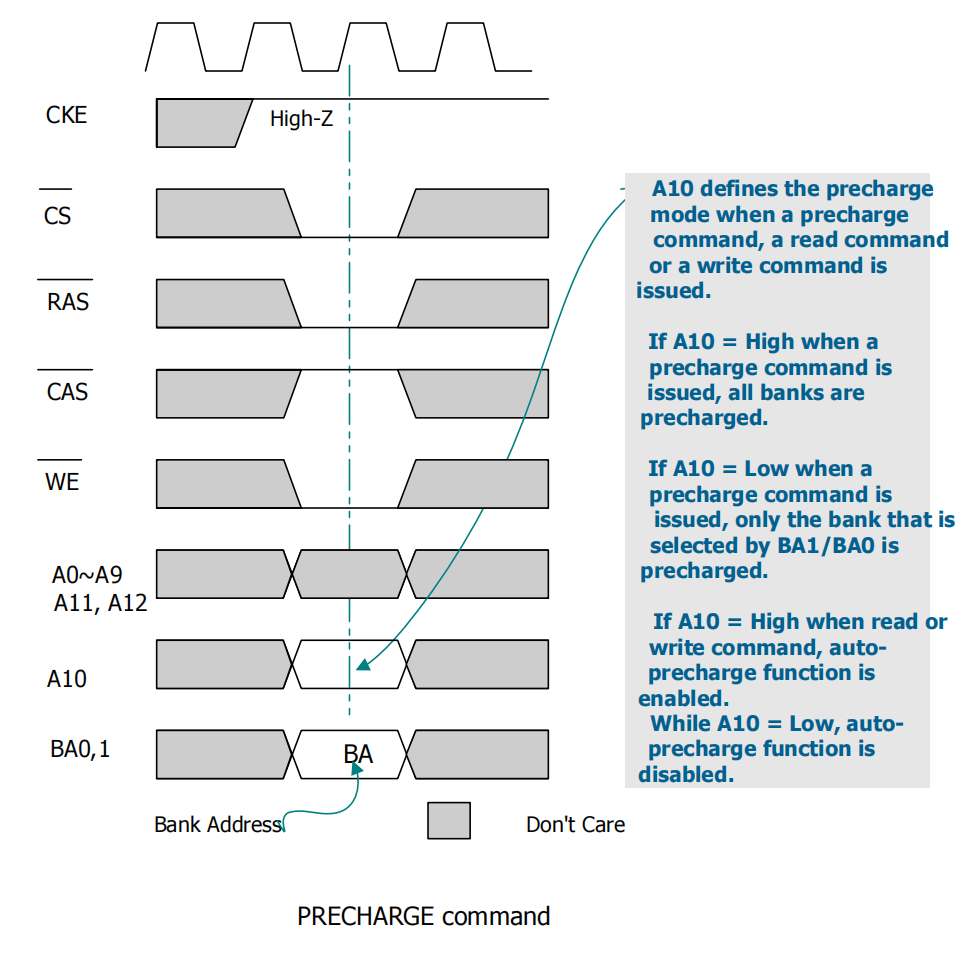

6.Precharge All Banks(预充电所有Bank):4'b0010

PRECHARGE指令用于停用特定存储库中的空闲行或所有存储库的空闲行。在完成预充电时间(tRP)前,不得向同一存储库(或多个存储库)发出其他预充电指令。若需对单个存储库进行预充电,必须指定该存储库地址;若需对所有存储库进行预充电,则需同时将A10置高并执行PRECHARGE指令。当A10处于高电平时,BA0和BA1将被忽略。若目标存储库中不存在空闲行,或先前已停用的行正在预充电过程中,则PRECHARGE指令将被视为无效指令。

7.Auto Refresh(自动刷新):4'b0001

由于是非持久性指令,每次需要刷新时都必须重新发出。刷新地址由内部刷新控制器生成。海力士SDR SDRAM要求以平均周期tREF发送自动刷新指令。为提高任务调度与切换效率,系统在绝对刷新间隔上提供了灵活调整空间。每个SDR SDRAM最多可接收八次自动刷新指令,且任意两次自动刷新指令之间的最大间隔时间不得超过8*tREF。

以上就是SDRAM简介。(如果有错误的地方,还请大家指出来,谢谢!)