gtxe2_channel内部参数和寄存器配置-CPLL超频设计,超过6.6Gbps的最高速率

参考:https://bbs.21ic.com/icview-461984-1-1.html

参考:https://chipdebug.com/forum-post/10297.html

参考:https://blog.csdn.net/qq_39731597/article/details/146184982

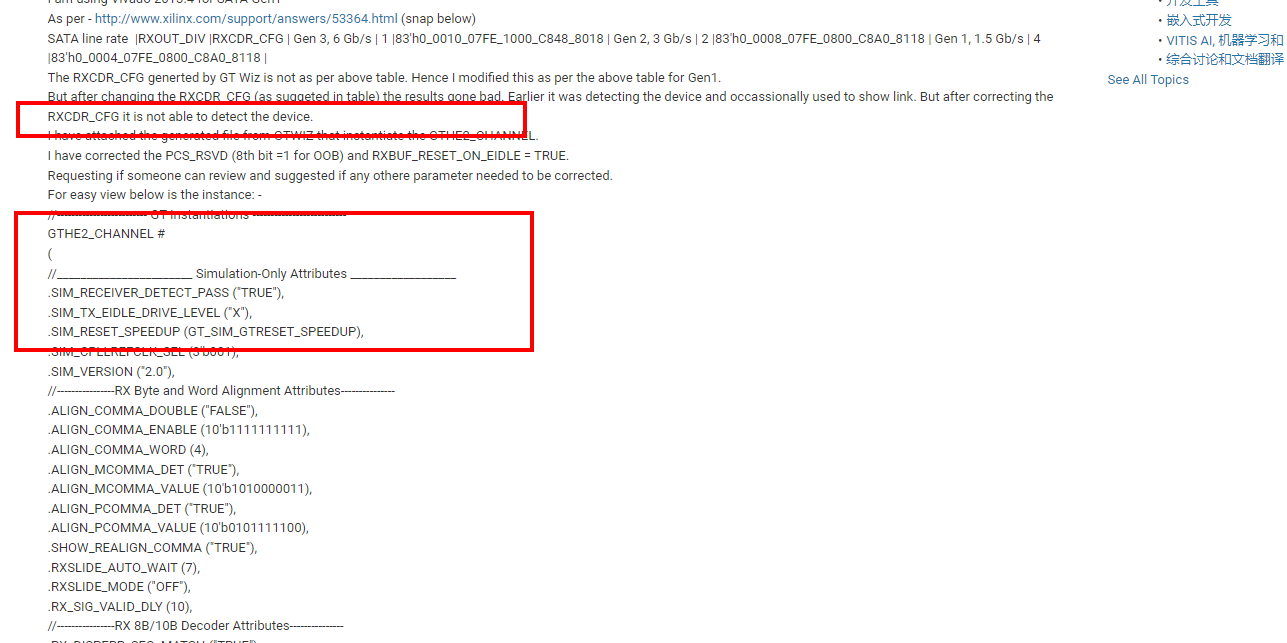

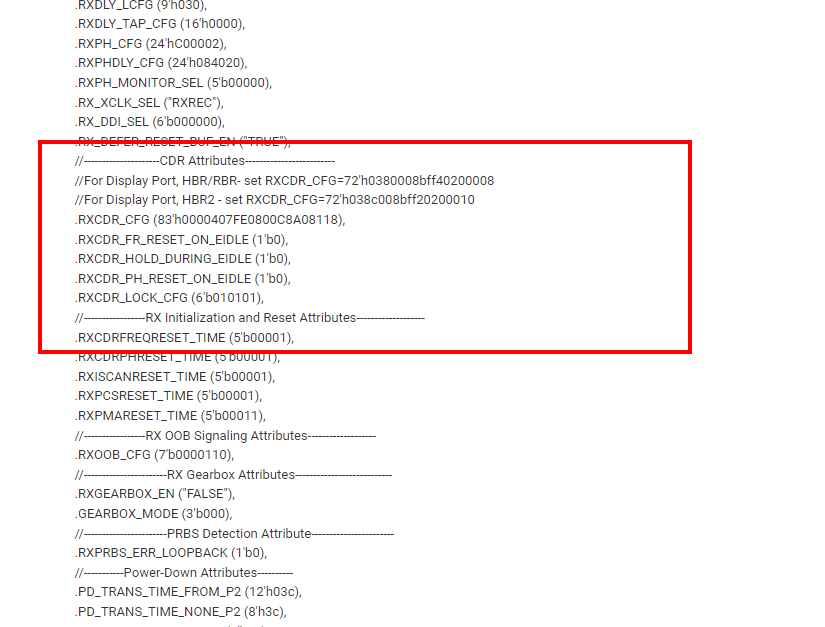

参考:https://adaptivesupport.amd.com/s/question/0D52E00006hpTxgSAE/v7-gth-sata-gen1?language=zh_CN

参考:httpshttps://adaptivesupport.amd.com/s/question/0D54U00008KLwsVSAT/virtex-7-gth-wizard-does-not-allow-certain-linerates-?language=zh_CN

https://adaptivesupport.amd.com/s/article/51369?language=zh_CN

https://adaptivesupport.amd.com/s/article/51625?language=zh_CN

关于xilinx的CPLL和QPLL所能够传输的速率频段不一样,有几个解决办法:

1.用CPLL超频,计算好各种分倍频参数,然后修改参考时钟,参考时钟最好使用频率可变的时钟芯片;

2.通过QPLL来实现,虽然QPLL在8G~9.8Gbps区间不支持,但是使用9.8Gbps配置,然后进行修改参数,估计是可以的吧,因为ibert是可以支持这个区间的,所以这里估计留有后门。