pcie 日常问答-20250528

问题均来自工作总结,面经问题;多为发散性问题;大多均会结合S IP rtl实现进行细致分析。

1. dllp包有哪些类型?dllp主要功能是干甚呢的?

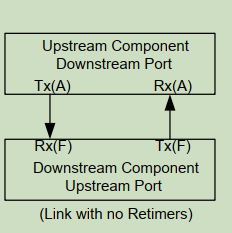

dllp是一个点到点的传输(传输过程中没有任何标识);并不是一个端到端的传输,tlp是端到端的传输。

dllp主要功能:

- flow control

- ack/nak 相应

- pme power 信号控制(不包含aspm)

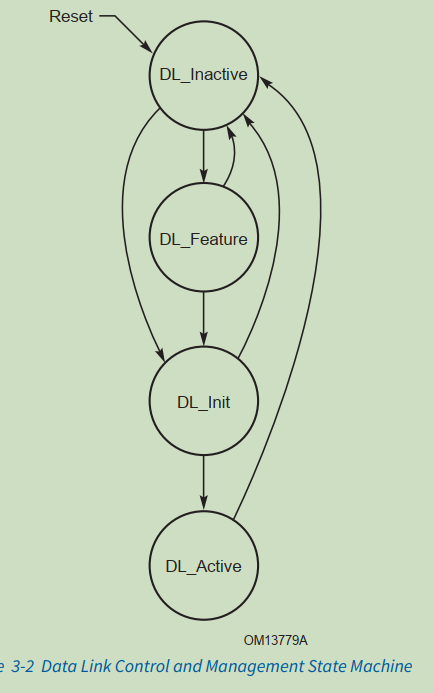

dllp 状态机,其中dl_feature和dllp_capability相关,当前只用来确定 credit scaled;

dllp状态机的训练是在lsttm之后,在ltssm到达L0之后才会开始训练。(从transaction log以及verdi波形中均能例证)

dllp包类型:

3.5.1 Data Link Layer Packet Rules

type类型:

- 0 :ack;

-

1: MRInit - See the MR-IOV Specification(没见过multiRoot virtualization)

-

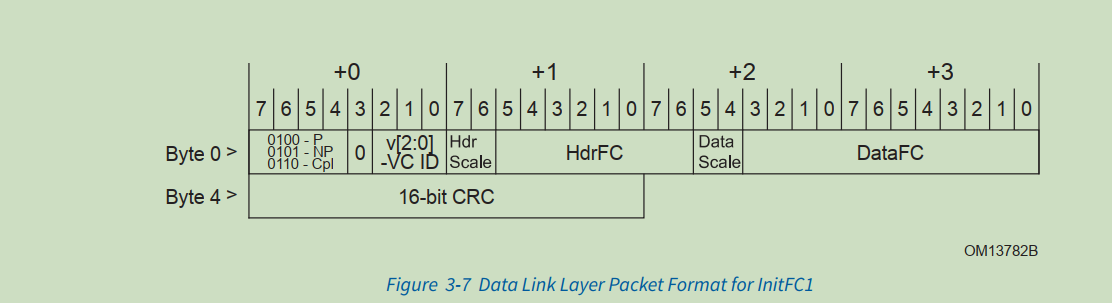

Encodings (b) DLLP Type 0000 0010 Data_Link_Feature ; 0001 0000 Nak 0010 0000 PM_Enter_L1 ;PME相关 0010 0001 PM_Enter_L23 0010 0011 PM_Active_State_Request_L1 0010 0100 PM_Request_Ack 0011 0000 Vendor-specific 0011 0001 NOP; no operation dllp;仅让链路保持活动状态; 0100 0v2v1v0 InitFC1-P (v[2:0] specifies Virtual Channel); v2v1v0为当前VC通道,当有多个vc通道时,在dllp进行初始化时可以看到会发送不同vc通道的initFC1相关的dllp包,transaction log可以看到 0101 0v2v1v0 InitFC1-NP 0110 0v2v1v0 InitFC1-Cpl 0111 0v2v1v0 MRInitFC1 (v[2:0] specifies Virtual Link) - See the MR-IOV Specification50 1100 0v2v1v0 InitFC2-P 1101 0v2v1v0 InitFC2-NP 1110 0v2v1v0 InitFC2-Cpl 1111 0v2v1v0 MRInitFC2 - See the MR-IOV Specification51 1000 0v2v1v0 UpdateFC-P;一般来说不会出现credit 用完的情况; 1001 0v2v1v0 UpdateFC-NP 1010 0v2v1v0 UpdateFC-Cpl 1011 0v2v1v0 MRUpdateFC - See the MR-IOV Specification52 - 关于PME dllp;在dllp层进行check之后被发送到power manager进行相关的操作;Checked for integrity on reception by the Data Link Layer, then passed to the component's power

management logic

1.1 当收到pme dllp包之后ep,rc是怎么处理的?

在进入D1,D2的前提条件是所有发出的request 的cpl均被收回,所以新收到的cpl被认为是unexpected completion。

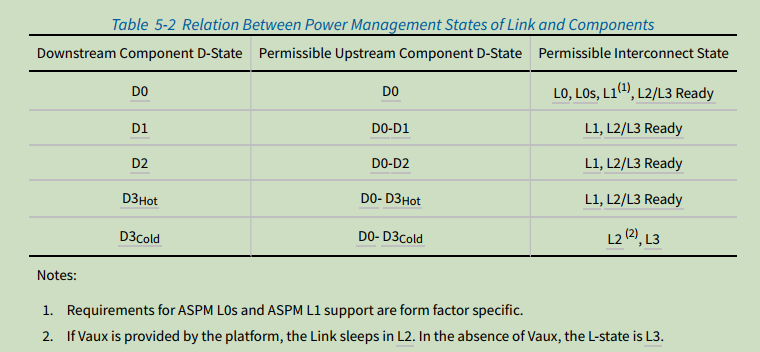

5.3.2 PM Software Control of the Link Power Management State(D state)

链路的电源管理状态由其下行组件(EP)的D状态决定。即下行端口来控制整个链路的电源状态切换。

以下规则与兼容pci-pm的电源管理相关:

- 在非D3cold状态下,设备接收到pme_tuen_off消息,必须发送pme_to_ack消息进行相应。

- 在任何D状态下,执行完pme_turn_off/pme_to_ack握手之后,下游组件必须使用pm_enter_l23 dllp请求链路状态转换到L2/L3_ready。完成L2/L3_ready之后,下游组件必须准备号主电源和参考时钟丢失。

- 单function usp,只有在D1,D2,D3hot时,链路才可以转换到L1状态。对于sw而言,上有端口的D状态不能设置为比最活跃的下游端口更不活跃的状态。下游为D2则上游不能为D3.

- 非ARI上游端口至少一个function为非D0状态,不得启动链路转换到L1.

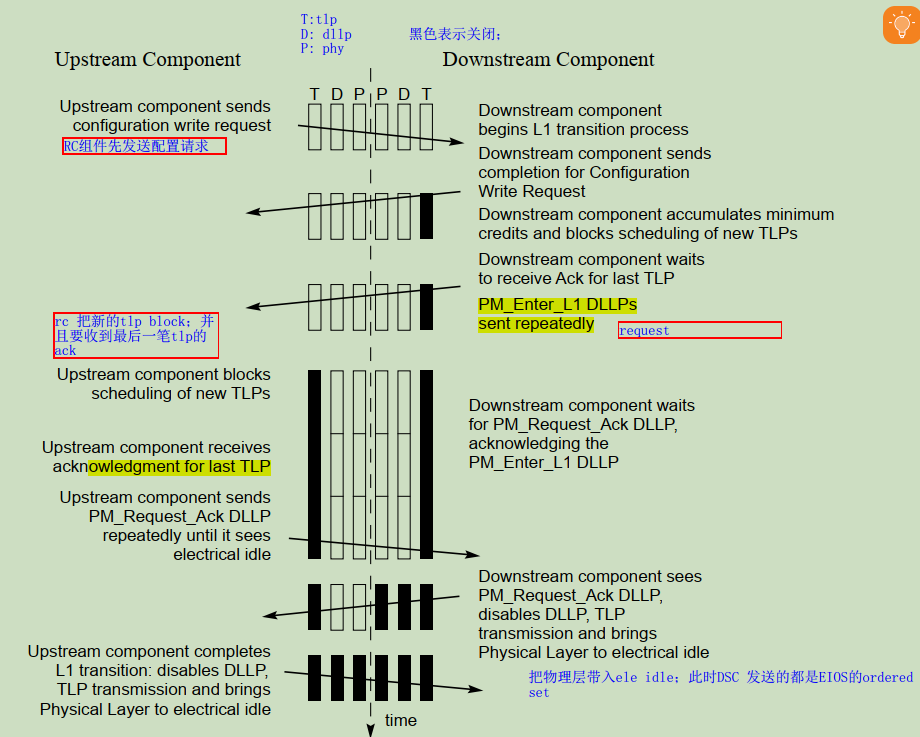

5.3.2.1 Entry into the L1 State

下游组件持续发送PM_Enter_L1 DLLP直至收到上游组件响应(PM_Request_Ack)。其间必须持续接收上游TLP/DLLP,并按需响应流控更新DLLP及确认/否认DLLP。

USP can trigger L1 entry; By: 软件控制PCI-PM capabilities,Use ASPM,use app requests the USP to enter L1.

其实有个疑问:在DSC TLP层变黑之后其实USC(up component)依旧可以继续发送tlp到DSC,那么此时DSC怎么处理这些收到的TLP包?

个人猜想:不会继续发送tlp了。

L1 exit can be initiated by the component on either end of a Link

且在D1,D2,D3hot状态下usp只能接受CFG和MEG TLP包。其余类型被认为unsupported requests。

L2/L3 ready

• L2/L3就绪进入过渡协议不会立即导致链路进入L2或L3状态。该过渡实质上是通过握手确认下游组件已准备好断电。只有当平台实际移除组件电源和参考时钟时,才会最终达成L2或L3状态。 • L2/L3就绪进入过渡的时机以完成PME_Turn_Off/PME_TO_Ack握手序列为标志。下游组件为应对断电所需的所有准备工作必须在启动过渡前完成。当所有断电和时钟丢失的准备工作就绪后,下游组件通过向上游发送PM_Enter_L23数据链路层包来启动L2/L3就绪进入流程。

ASPM通过什么条件(前提)使pcie设备进入L0s,L1状态?

通过设置DEFAULT_L0S_ENTR_LATENCY; 默认4us,最大7us;

DEFAULT_L1_ENTR_LATENCY; 默认8us,最大16us;

RTL PM相关signal 来源

共有三处:

1. app user signal;举例:app_ready_entr_l23;app_req_exit_l1;

2. 从pm-csr寄存器而来(capability);cdm_pm_reg中获取;

3. 从ltssm state获取;

a)sdlp(dllp state machine and logic):output:pm_prot_state,pm_l0s_state;

input:pm_aspm_l1_en;

b) smlh: smlh_in_l1,smlh_in_l23 等;

2. credit 每种类型的unit都是多大?

dllp包:initfc_p_vc0 ; 63 x4 480 x1 ; 解释:

initfc_p_vc0:vc0通道的initial flow control 1,发送包。data,hdr scale: 可以查看dl层capability,目前为1.

63: hdr FC; hdr scale设置为1,8bit宽度,共63个posted header credit unit;每个unit 如果不支持tlp prefix;就是最大的TLP header(4DW)+1 DW tlp digest(ECRC)= 5DW;

如果支持TLP prefix:1 DW tlp digest + 4DW header + x个TLP prefix 包。

x4: header scale factor;(2'b10)

480: data FC,对于data FC而言一个unit 表示4DW;

0x1: data scale factor;(2'b01)

ECRC:

经过switch 时是不重新计算,lcrc没过一级都要重新做校验。ECRC 1DW;

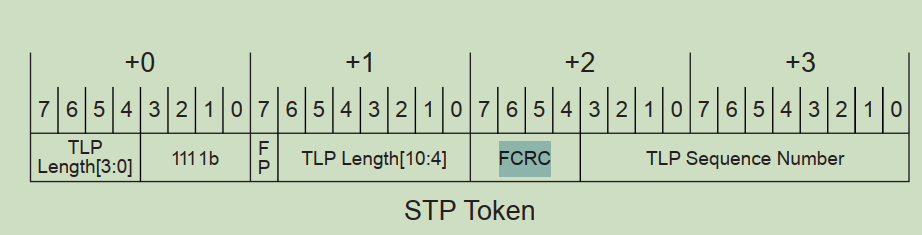

pcie上共有4中类型的CRC;FCRC,ECRC,LCRC;DCRC;

FCRC仅存在于stp token中(128/130b)编码,占用4bit。Lcrc为强制勾选,会带着sequence number 一起编码,占用32bit,在dllp上实现。

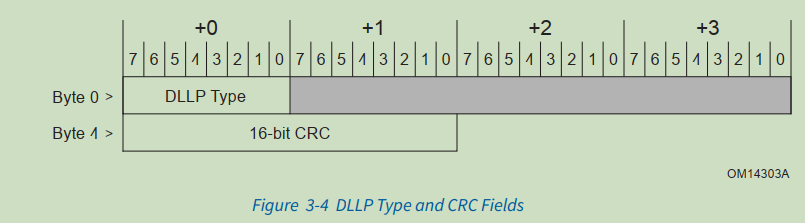

DCRC: dllp包最后的16bit crc校验。

2.6.1 Flow Control Rules

completion分为infinite和finite 两种flow control;S中默认使用infinite(无限credit),credit value always 0.当确认了infinite FC时不需要更新updatefc dlp包,rx收到对应的dlp包会被丢弃。

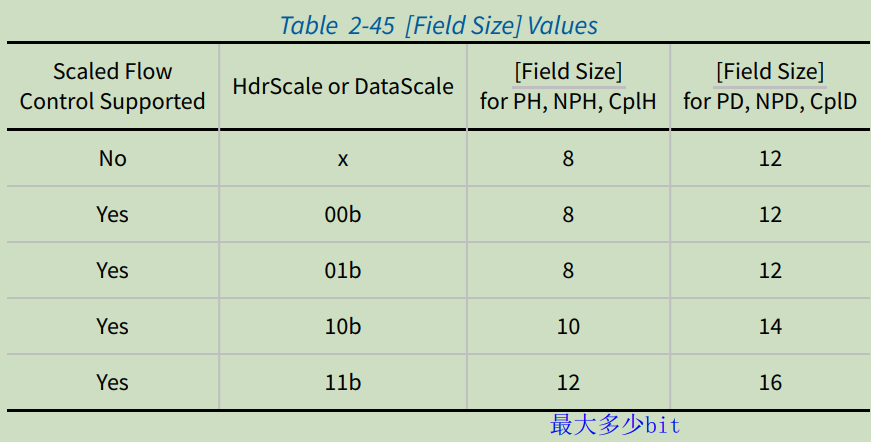

2.6.1.1 FC Information Tracked by Transmitter

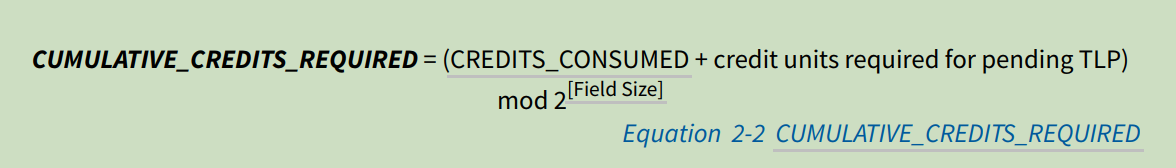

流控制TLP传输门 跟踪两个量:

CREDITS_CONSUMED:

计算从initfc之后tx端消耗的所有 credit;每次消费若干 credit(Increment),就加到当前的 CREDITS_CONSUMED 上,并对字段位宽进行模运算,保持在合法范围内。

eg:

2^[Field Size] = 2^12 = 4096

也就是说 CREDITS_CONSUMED 是个 12-bit 宽的字段,最大值为 4095。超过这个值时就 回绕(wrap around)。

当前 CREDITS_CONSUMED = 4090,Increment = 10:本次使用了10个credit;

计算:

(4090 + 10) mod 4096 = 4100 mod 4096 = 4;

CREDIT_LIMIT:

接收端允许的最大FC units。

每种类型的tlp包credit消耗计算规则:

除了infinite 类型的tlp包外,其余的tlp包要满足以上规则。

2.6.1.2 FC Information Tracked by Receiver

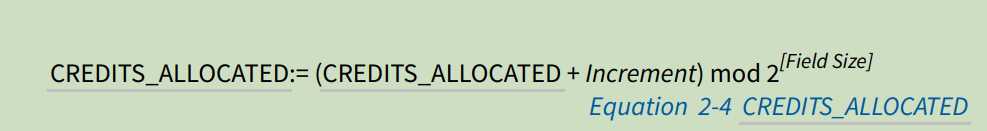

CREDITS_ALLOCATED:

用于传输的credit总数;

CREDITS_RECEIVED:TLP rx 接收到的credit总量。

credit buffer 大小如何计算

背靠背传输(Back-to-Back Transmission) 是指在总线或链路中,连续不间断地发送多个数据包(如 TLP),中间不插入空闲周期或等待周期,实现最大吞吐率的一种传输方式。

FC credit caculate:通过lane number,controller datapath width,max payload size,flow control update latencies,internal delay,PHY latency。

update latency从pcie spec表中给出;gen5x4 max_pay_size:256B;最大214个symbol time。

要求:连续tlp传输不能出现credit不够情况。

1. 在TLP包的最后一个synbol收到之后FC timer才开始工作。所以rx必须能够至少缓存1个max payload 包。

2. 更新FC,只有当latency timer 超时后才会更新;所以credit buffer要能装下timer 从0到超时时间段的所有tlp包

3. 延迟计算:

a) TLP 传输到远端时间

b) tlp包本地处理时间

c) FC update 传输时间

d)远端接收FC update时间

e)re-timer时间(如果存在) cx_max_retimer 值表示

depth =(calc_bytes)/(4*CX_NW)/4

calc_bytes =roundUptoNextMTU(data_size{1} + fc_lat_limit{2} +

fc_delay_bytes)

fc_lat_limit =data_size *fc_upd_fac

fc_delay_bytes =CX_INTERNAL_DELAY{3.b and 3.c}*CX_NB*CX_NL+

base_internal_delay{3.a and 3.d}*CX_NL + retimer_latency{3.e}*CX_NL

此处不做详细解释。

RADM_NPQ_DCRD_VC0: the num of tlp data to advertise for vc0;