源端串联端接

源端串联端接:

接触SI时最先遇到的信号完整性问题就是过冲和振铃,对于点对点拓扑结构来说,产生过冲和振铃的最直接原因就是传输通道阻抗不匹配,抑制过冲和振铃最有效的方法就是做好源端阻抗匹配。什么是源端阻抗匹配?我们定义驱动的输出阻抗为,源端端接电阻为R,传输线阻抗为

。源端阻抗匹配就是指

=

+R。源端串联端接除了对端接阻值有要求,还经常要求要把端接电阻靠近驱动端放置,这样做的目的是什么呢?下面我们就从串接阻值和放置位置来详细讨论源端串联端接需要注意的问题。

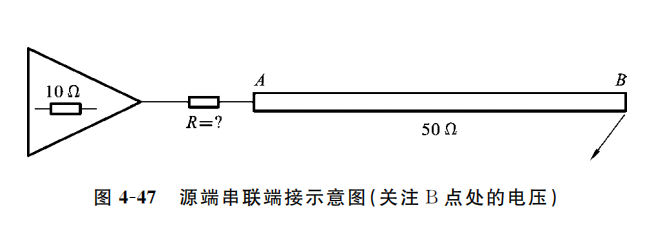

如图4-47所示,我们假设驱动器的内阻为10Ω,传输线阻抗为50 Ω,通道末端为开路。其实,实际电路在工作时,通道末端通常是高阻状态,也就是和开路差不多。通道末端开路,也就意味着全反射,这时在通道末端侦测到的电压就应该是入射电压的2倍。我们分三种情况,分别是驱动内阻加上端接电阻大于、小于和等于传输线阻抗。验证端接电阻阻值变化对信号的影响。

令R取值分别为0Ω、40 Ω、70Ω。按照电路串联分压理论,初始进入A点的电压为=

=50/(50+R+

),

表示驱动器原始电压,通道末端全反射,初始B点电压为

=2

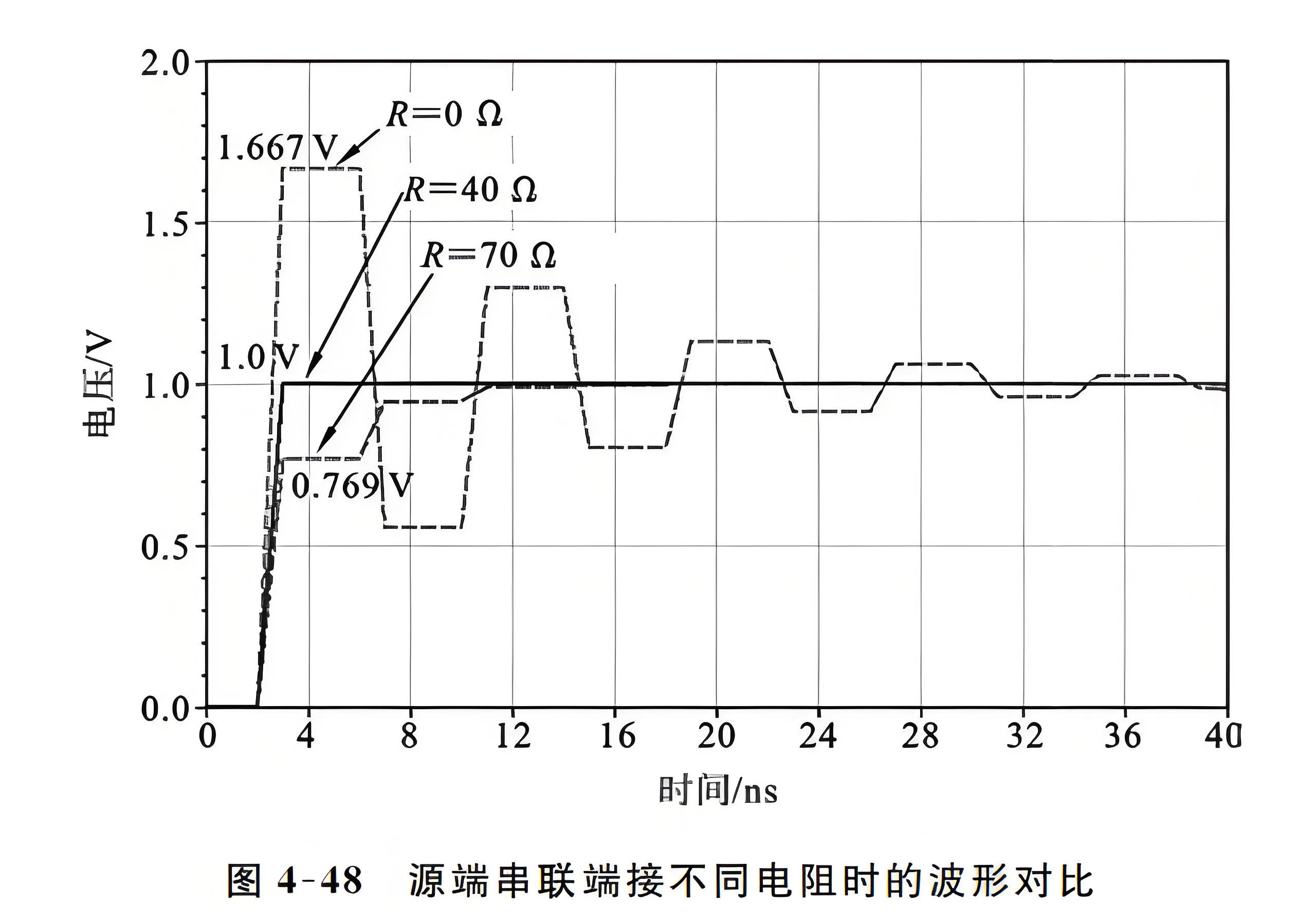

。B点的反射电压回到源端,又会进行一次反射。具体的计算方式可以参考前面所讲的反弹图的计算方法,最后的结果如图4-48所示。

我们姑且把驱动器内阻加上源端串联电阻一起称为源端阻抗。由图4-48可知,当源端阻抗小于传输线阻抗时,信号过冲比较厉害;当源端阻抗大于传输线阻抗时,会出现输出电压不足的情况。这两种情况都是我们不愿意看到的,最好的做法就是通过仿真,选择合适的源端串联电阻,使之与传输线阻抗相匹配。

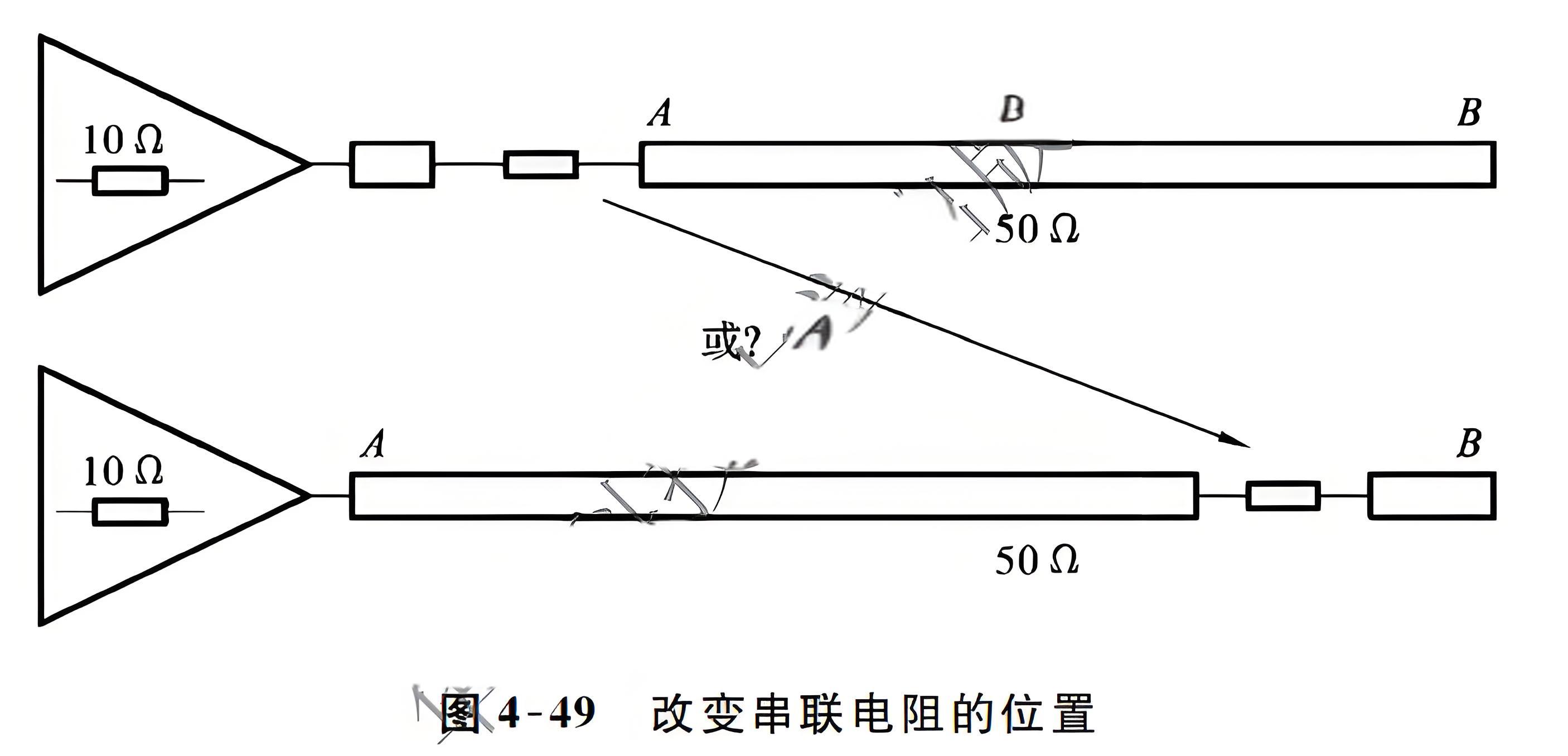

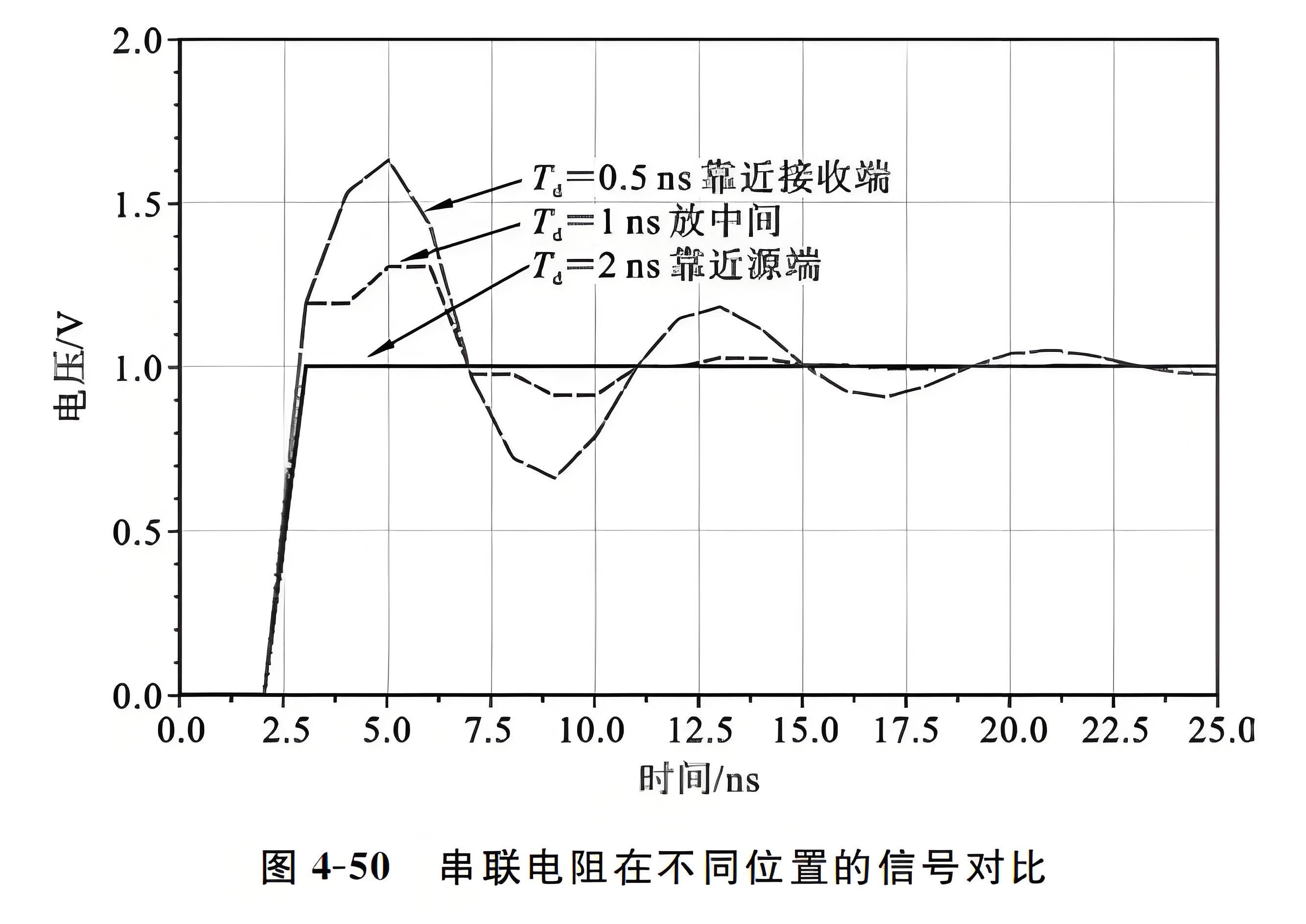

源端串联端接除了选择阻值,电阻的放置位置对输出信号也会有一定的影响。如图4-49所示,假设电阻到B端的时间为,

越大,这意味着电阻越靠近源端。

如图4-50所示,端接电阻越靠近驱动端效果越好。这个近是个相对的距离,跟信号的速率有关,比较明显的例子就是DDR,其数据线是双向的,当信号是写时序时,CPU是驱动端;B当信号是读时序时,DDR是驱动端。所以就将端接电阻放在传输线的中间。

大家思考个这样的问题,如图4-49中的拓扑结构,假如电阻阻值R和左右两边传输线阻抗Z₁/Zr都是50 Ω,当信号从驱动端传输过来时,在电阻左侧这个点的反射系数是多少?是(R-Z1)/(R+Z1)吗?

如果这个问题比较难想清楚,那么我们将上面的条件变换一下,电阻R的右边不是传输线Zr,而是另一个电阻Rr,这时的反射系数是多少?做这样一个变换之后,大家估计就清楚了,在电阻左边这个点上,反射系数是(R+Rr-Z1)/(R+Rr+Z1),也就是要把右边部分的电阻与传输线阻抗串联起来。

那么如何去理解串联电阻离源端还有一段距离时,这其中的多重反射呢?可以将其等同于4.3节中breakout区域走线来理解,“由于驱动端距离串阻比较近,这段的多重反射就被淹没了”;也可以理解为,在这个位置串阻先反射掉一部分的能量,避免接收端的反射过大,通过增加反射的次数,达到减小反射的强度的目的。