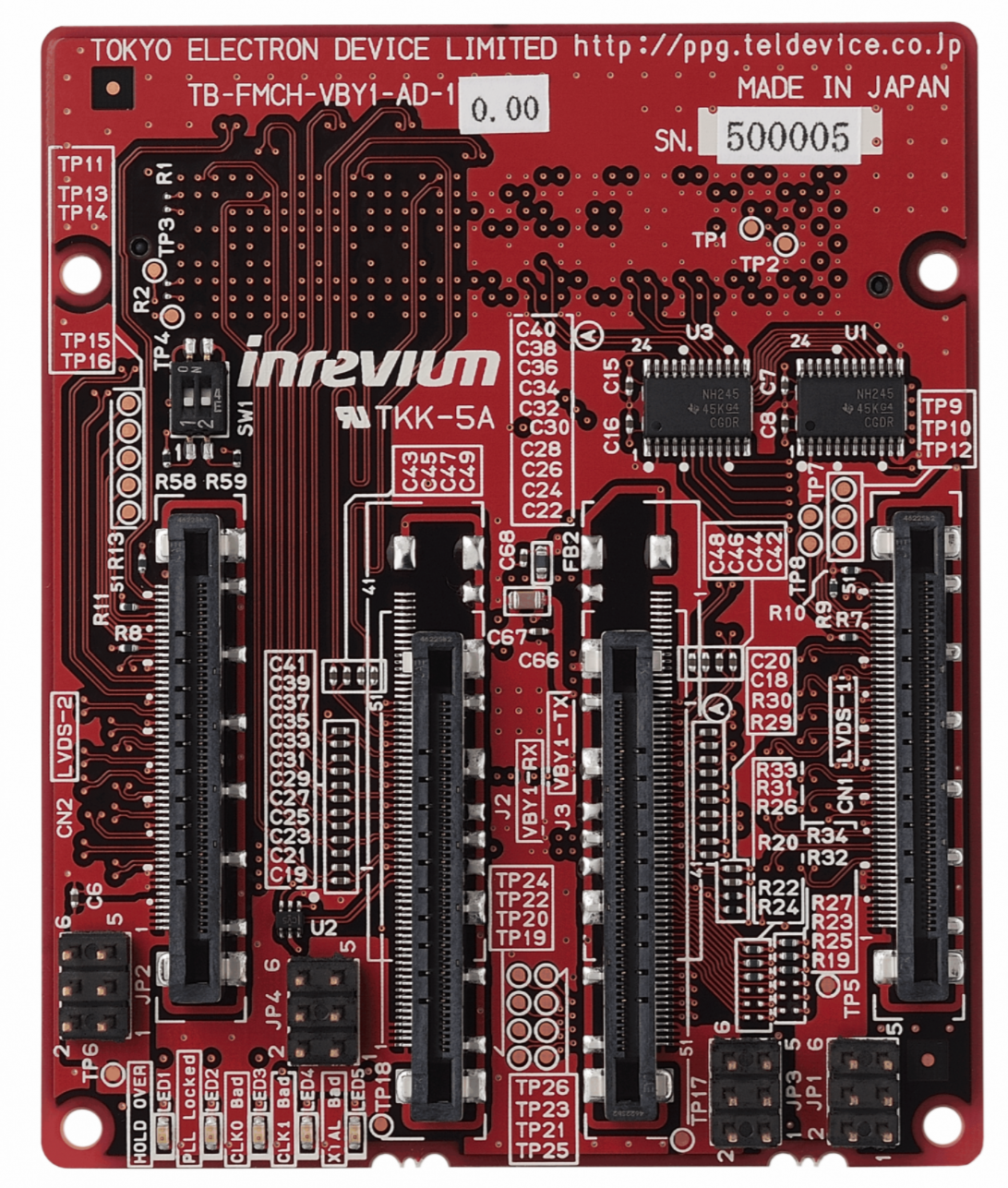

8Lane V-by-One HS LVDS FMC Card

8Lane V-by-One HS LVDS 卡它能够将 Samtec制造的 FMC连接器(高引脚数)和 JAE 制造的 FI-R系列连接器进行转换,并支持 THine Electronics,Inc.的Vby-One HS 传输协议。虽然安装了 JAE 制造的 FI-RE51S-VF,但如需通过 V-by-One HS协议实现 16LANE,可根据对端设备的配置,提供已更换为 FI-RE41S-VF 安装的电路板。该卡旨在与包含高引脚数连接器的平台板进行连接。

一、规格和特点

| Clock | Can be clocked from IDT ICS849N202I to Xilinx FPGA transceivers |

|---|---|

| Power supply | Power supply can be switched by jumper switch |

二、型号及接口

| Product Model Number | TB-FMCH-VBY1-AD |

|---|---|

| Deliverables | 8Lane V-by-One HS LVDS FMC Cards FMC connector fixing set Cabling for V-by-One HS 51pin Cabling for LVDS 41pin |

三、V-by-One IP及实现

参考链接:

创作中心-CSDN

创作中心-CSDN

主要参数:

| Features | Transmission rate up to 3.75Gbps per data lane for Kintex-7 FPGA Supports 1, 2, 4, and 8 data lanes (Customizable in 16, 32 data lane compatible consigned development) Flexible setting of swing width and pre-emphasis function Flexible Implementation and Package Compatibility |

|---|---|

| Core specifications | Transmission rate up to 3.75Gbps per data lane for Kintex-7 FPGA Supports 1, 2, 4, and 8 data lanes (Customizable in 16, 32 data lane compatible consigned development) Flexible setting of swing width and pre-emphasis function Flexible Implementation and Package Compatibility |

| Supporting FPGA | Kintex UltraScale(GTH) Virtex-7(GTH) Kintex-7(GTX) Artix-7(GTP) |

| Resolution | Refresh rate (pixel clock) | Color bit width | Number of data lanes |

|---|---|---|---|

| HD | 60Hz(74.25MHz) | 18/24/30/36bit | 1 |

| 120Hz(148.5MHz) | 18/24/30/36bit | 2 | |

| 240Hz(297MHz) | 18/24/30/36bit | 4 | |

| Full-HD | 60Hz(148.25MHz) | 18/24/30/36bit | 2 |

| 120Hz(297MHz) | 18/24/30/36bit | 4 | |

| 240Hz(594MHz) | 8/24/30/36bit | 8 | |

| 4K2K | 60Hz(594MHz) | 18/24/30/36bit | 8 |

| 120Hz(1188MHz) | 18/24/30/36bit | 16 | |

| 240Hz(2376MHz) | 18/24/30/36bit | 32 |