FPGA纯verilog实现MIPI-DSI视频编码输出,提供工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

- 我这里已有的 MIPI 编解码方案

- 3、设计思路框架

- 工程设计原理框图

- FPGA内部彩条

- RGB数据位宽转换

- RGB数据缓存

- MIPI-DSI协议层编码

- MIPI-DPHY物理层串化

- MIPI-LVDS显示屏

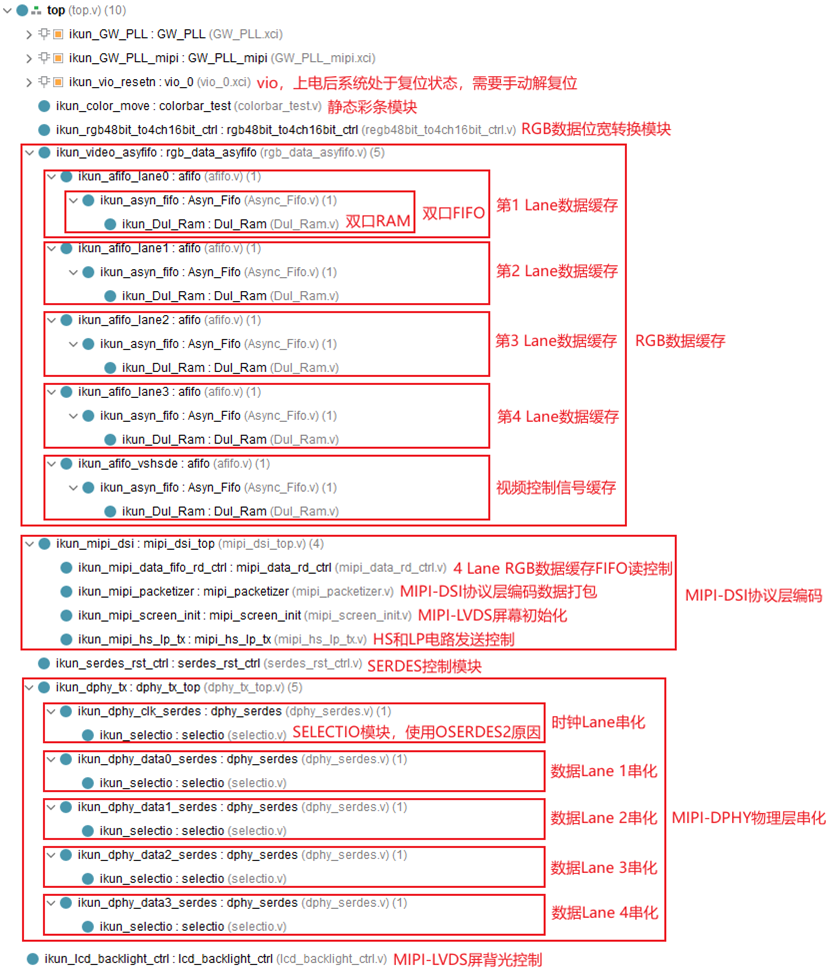

- 工程源码架构

- 4、工程源码1详解:Kintex7-325T版本

- 5、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 6、上板调试验证并演示

- 准备工作

- VIO解复位

- MIPI-DSI视频编码输出演示

- 7、工程源码获取

FPGA纯verilog实现MIPI-DSI视频编码输出,提供工程源码和技术支持

1、前言

FPGA实现MIPI视频编码现状:

MIPI视频编码分为DSI和D-PHY两大部分,其中D-PHY属于物理层,依托硬件,灵活性不高,方案不多;DSI属于协议层,依托代码,灵活性很高,方案很多;所以只要实现了D-PHY,MIPI-DSI解码其实就很灵活了;第一种D-PHY方案是使用FPGA内部资源实现,该方案优点是设计简单,缺点是硬件成本较高;第二种是使用专用的D-PHY芯片,比如MC20901,该方案优点是设计简单,缺点是硬件成本较高;本设计使用Xilinx系列FPGA纯verilog代码实现MIPI-DSI视频编码输出;

工程概述

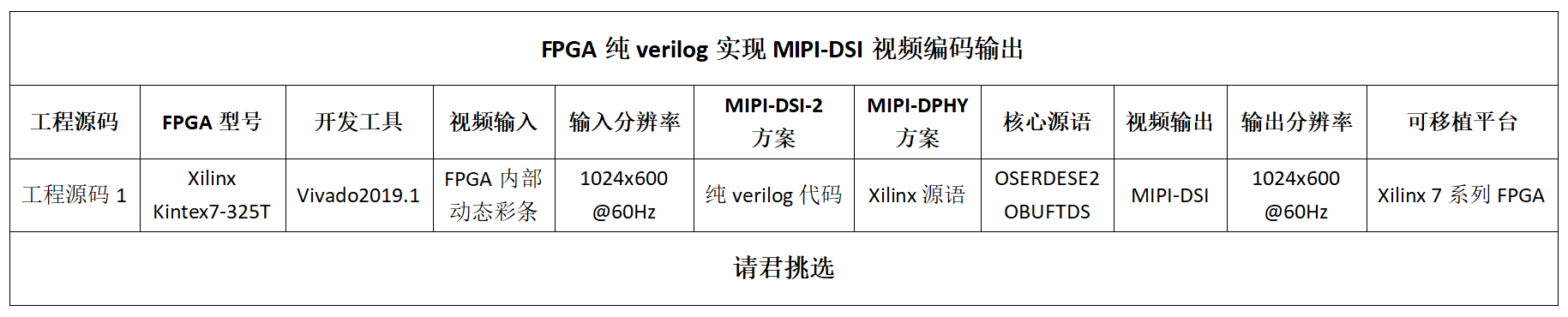

本设计使用Xilinx 7系列FPGA纯verilog代码实现MIPI-DSI视频编码输出;首先FPGA内部生成1个1024x600的静态彩条视频作为输入源,彩条视频为Native接口;然后彩条视频送入视频位宽转换模块实现位宽转换功能,将输入的24bit像素数据转换为4路16bit像素数据,以便于后续模块生成4 Lane MIPI数据;然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;然后4 Lane视频送入MIPI-DSI协议层编码模块,按照DSI协议将输入的RGB视频进行编码处理,然后输出HS电路数据和LP电路数据;然后MIPI-DSI数据送入MIPI-DPHY物理层串化模块,将输入的4 Lane并行MIPI-DSI数据串化为4 Lane高速串行的差分信号,模块依托Xilinx官方的OSERDESE2和OBUFTDS实现串化和单端转差分处理;中途还要对MIPI-LVDS显示屏做初始化操作;最后MIPI-DSI编码视频直接送MIPI-LVDS显示屏显示即可;针对市场主流需求,本设计提供1套vivado工程源码,具体如下:

现对上述1套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为高云Kintex7-325T-xc7k325tffg900-2;首先FPGA内部生成1个1024x600的静态彩条视频作为输入源,彩条视频为Native接口;然后彩条视频送入视频位宽转换模块实现位宽转换功能,将输入的24bit像素数据转换为4路16bit像素数据,以便于后续模块生成4 Lane MIPI数据;然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;然后4 Lane视频送入MIPI-DSI协议层编码模块,按照DSI协议将输入的RGB视频进行编码处理,然后输出HS电路数据和LP电路数据;然后MIPI-DSI数据送入MIPI-DPHY物理层串化模块,将输入的4 Lane并行MIPI-DSI数据串化为4 Lane高速串行的差分信号,模块依托Xilinx官方的OSERDESE2和OBUFTDS实现串化和单端转差分处理;中途还要对MIPI-LVDS显示屏做初始化操作;最后MIPI-DSI编码视频直接送MIPI-LVDS显示屏显示即可,输出分辨率为1024x600@60Hz,MIPI-4 Lane;本工程适用于Xilinx 7系列FPGA实现MIPI-DSI视频编码输出应用;

本文详细描述了FPGA纯verilog实现MIPI-DSI视频编码输出的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网以及其他开源免费获取渠道等等),若大佬们觉得有所冒犯,请私信批评教育;部分模块源码转载自上述网络,版权归原作者所有,如有侵权请联系我们删除;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我已有的所有工程源码总目录----方便你快速找到自己喜欢的项目

其实一直有朋友反馈,说我的博客文章太多了,乱花渐欲迷人,自己看得一头雾水,不方便快速定位找到自己想要的项目,所以本博文置顶,列出我目前已有的所有项目,并给出总目录,每个项目的文章链接,当然,本博文实时更新。。。以下是博客地址:

点击直接前往

我这里已有的 MIPI 编解码方案

我这里目前已有丰富的基于FPGA的MIPI编解码方案,主要是MIPI解码的,既有纯vhdl实现的MIPI解码,也有调用Xilinx官方IP实现的MIPI解码,既有2line的MIPI解码,也有4line的MIPI解码,既有4K分辨率的MIPI解码,也有小到720P分辨率的MIPI解码,既有基于Xilinx平台FPGA的MIPI解码也有基于Altera平台FPGA的MIPI解码,还有基于Lattice平台FPGA的MIPI解码,后续还将继续推出更过国产FPGA的MIPI解码方案,毕竟目前国产化方案才是未来主流,后续也将推出更多MIPI编码的DSI方案,努力将FPGA的MIPI编解码方案做成白菜价。。。

基于此,我专门建了一个MIPI编解码的专栏,并将MIPI编解码的博客都放到了专栏里整理,对FPGA编解码MIPI有项目需求或学习兴趣的兄弟可以去我的专栏看看,专栏地址如下:

点击直接前往专栏

3、设计思路框架

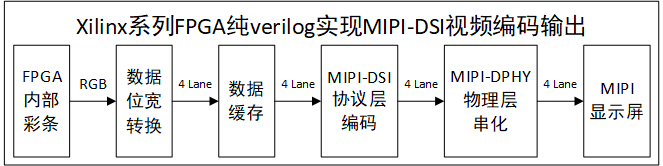

工程设计原理框图

工程设计原理框图如下:

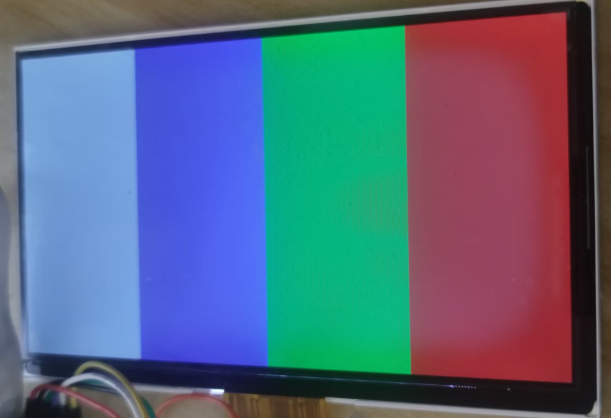

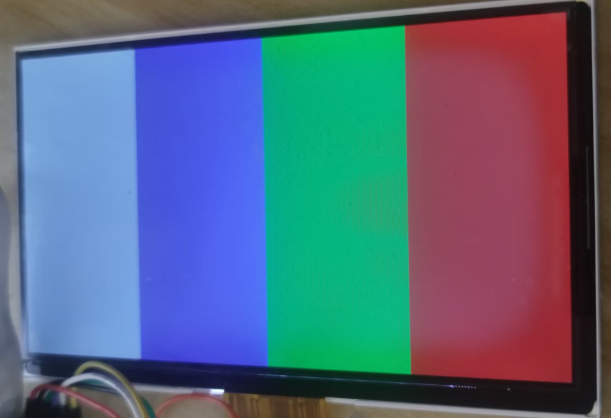

FPGA内部彩条

首先FPGA内部生成1个1024x600@60Hz的静态彩条视频作为输入源,彩条视频为Native接口,即常规的行同步信号、场同步信号、数据有效信号、像素数据等;FPGA内部彩条设计为4阶白、蓝、绿、红色彩条,如下:

FPGA内部彩条代码架构如下:

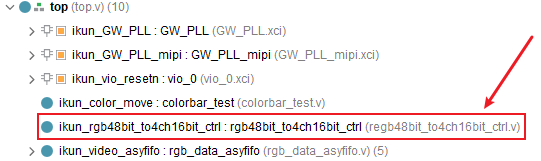

RGB数据位宽转换

然后彩条视频送入视频位宽转换模块实现位宽转换功能,将输入的24bit像素数据转换为4路16bit像素数据,以便于后续模块生成4 Lane MIPI数据;需要注意的是,24bit的彩条视频需要拓展至48bit,直接将单路的24bit RGB数据复制为2路即可;RGB数据位宽转换代码架构如下:

RGB数据缓存

然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;数据缓存使用纯verilog代码实现的异步FIFO实现;RGB数据缓存代码架构如下:

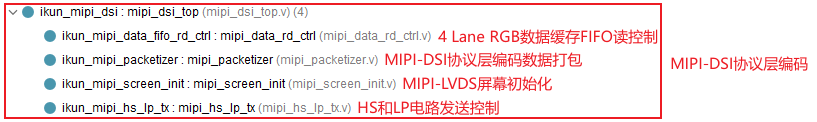

MIPI-DSI协议层编码

然后4 Lane视频送入异步FIFO缓存模块,以实现数据跨时钟域转换;然后4 Lane视频送入MIPI-DSI协议层编码模块,按照DSI协议将输入的RGB视频进行编码处理,然后输出HS电路数据和LP电路数据;MIPI-DSI协议层编码代码架构如下:

MIPI-DPHY物理层串化

然后MIPI-DSI数据送入MIPI-DPHY物理层串化模块,将输入的4 Lane并行MIPI-DSI数据串化为4 Lane高速串行的差分信号,模块依托Xilinx官方的OSERDESE2和OBUFTDS实现串化和单端转差分处理;MIPI-DPHY物理层串化代码架构如下:

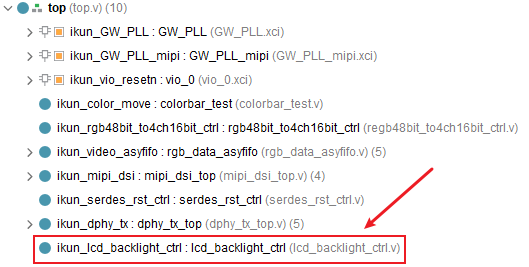

MIPI-LVDS显示屏

MIPI-LVDS显示屏分辨率为1024x600@60Hz;需要对MIPI-LVDS显示屏做初始化操作和背光控制,背光控制代码例化如下:

最后MIPI-DSI编码视频直接送MIPI-LVDS显示屏显示即可;MIPI-LVDS显示屏实物如下:

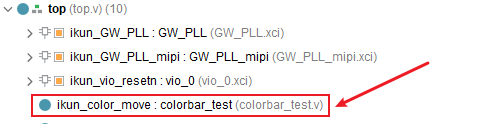

工程源码架构

工程源码架构如下:

4、工程源码1详解:Kintex7-325T版本

开发板FPGA型号:Kintex7-325T-xc7k325tffg900-2;

FPGA开发环境:Vivado2019.1;

输入:FPGA内部彩条,分辨率1024x600@60Hz;

输出:MIPI,分辨率1024x600@60Hz,4 Lane模式;

MIPI-DSI2-TX方案:纯verilog代码方案;

MIPI-D-PHY方案:纯verilog代码方案,OSERDESE2原语;

工程源码架构请参考前面第3章节中的《工程源码架构》小节;

工程作用:此工程目的是让读者掌握Xilinx系列FPGA纯verilog实现MIPI-DSI视频编码输出的设计能力,以便能够移植和设计自己的项目;

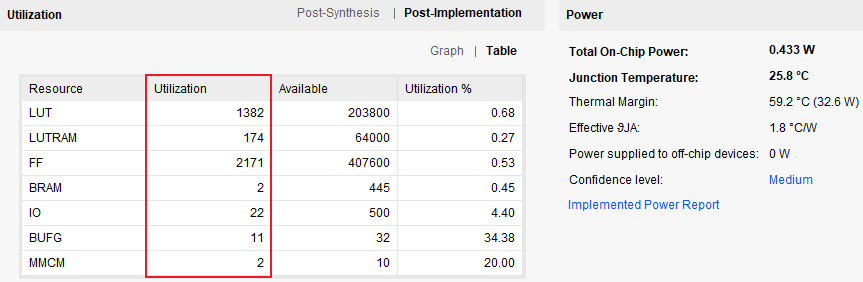

工程的资源消耗和功耗如下:

5、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

6、上板调试验证并演示

准备工作

FPGA开发板,推荐使用本博的开发板;

MIPI-LVDS显示屏;

开发板连接如下:

开发板上电后下载bit即可测试;

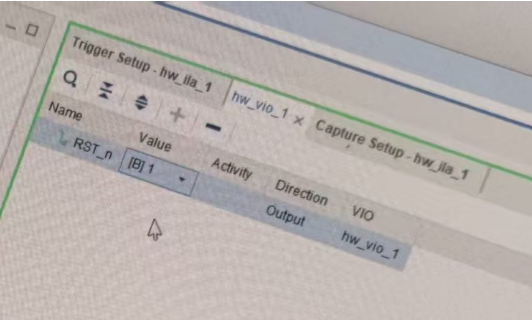

VIO解复位

由于上电后系统由VIO控制处于复位状态下,所以需要操作VIO进行解复位,如下:

即需要手动将RST_n设置为1;

MIPI-DSI视频编码输出演示

MIPI-DSI视频编码输出如下:

MIPI-TX原始

7、工程源码获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务: