锁相环技术简介(面向储能变流器应用)

锁相环(Phase Locked Loop,PLL)是一个相位误差控制系统,其工作原理是利用两个信号之间的相位误差来控制输出信号的频率,最终使两个信号之间的相位差保持恒定,从而达到相位锁定的目的。在AD/DC变换或需要并网的DC/AC变换等系统中,为满足控制要求,需要知道电网的频率与相位。因此要求系统具有频率和相位跟踪功能,即锁相功能。

一、锁相环基本原理

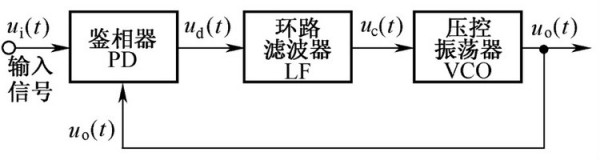

一个典型锁相环系统主要由鉴相器(Phase Detector,PD)、环路滤波器(Loop Filter,LF)和压控振荡器(Voltage Controlled Oscillator,VCO)三个基本电路组成。

1.鉴相器(PD)

鉴相器是完成相位比较的单元,用来比较输出信号和输入信号之间的相位。

2.环路滤波器(LF)

环路滤波器常采用低通滤波器结构,用于滤除ud(t)中的高频分量及噪声,提高环路的稳定性。

3.压控振荡器(VCO)

在锁相环中压控振荡器受低通滤波器输出电压uc(t)的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,或使压控振荡器输出信号的相位和输入信号的相位保持某种关系,由此达到相位锁定的目的。

在模拟电路中,压控元件一般采用变容二极管。有低通滤波器送来的控制信号uc(t)加在压控振荡器振荡回路中的变容二极管上,当uc(t)变化时,引起变容二极管电容的变化,从而使振荡器的频率发生变化。因此压控振荡器实际上就是一种电压-频率变换器,在锁相环中起着电压-相位变化作用。

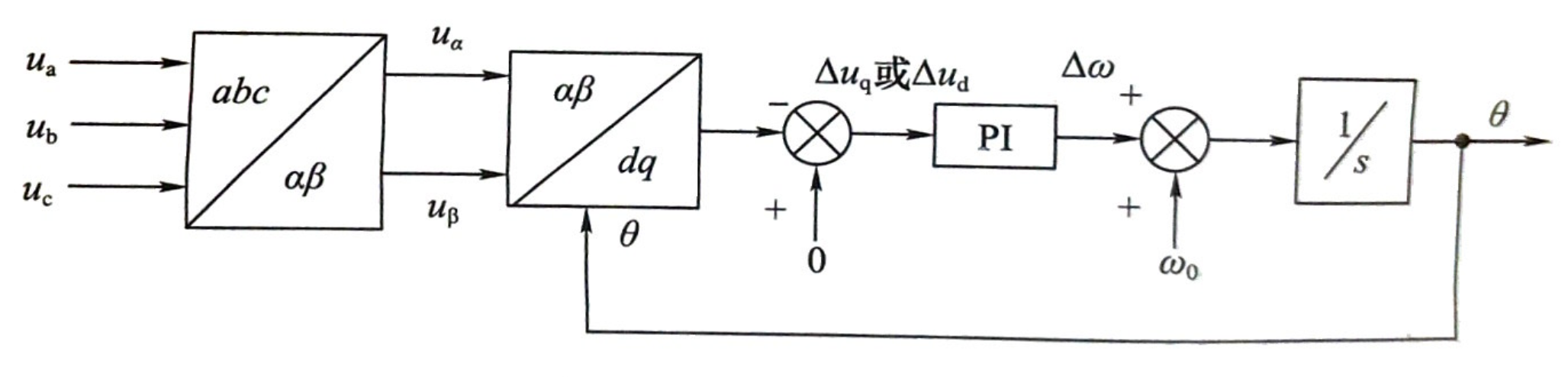

二、三相PLL

基本原理:首先将三相输入电压ua、ub、uc转换到两相静止坐标系αβ下,然后从αβ坐标系转换到与三相电压同步旋转的dq坐标系下,得到电压的直流分量ud、uq;如果锁相角与电网电压相位同步,则直流分量ud为定值,而uq为零(或者是uq为定值、ud为零,主要与abc-dq变换的设置有关)。因此,可以将参考值零和实际三相电压坐标系变换后的uq相减(也可以采用d轴调节进行鉴相),得到误差信号Δuq,经过PI调节后信号与初始角频率ω0相加后得到实际角频率;最后经过积分环节将角频率转换为相位信号输出,最终实现锁相功能。