锁定锁存器 | 原理 / 应用 / 时序

注:本文为 “锁定锁存器” 相关合辑。

英文引文,机翻未校。

中文引文,略作重排。

如有内容异常,请看原文。

Lockup latch – principle, application and timing

锁定锁存器——原理、应用与时序

What are lock-up latches

什么是锁定锁存器

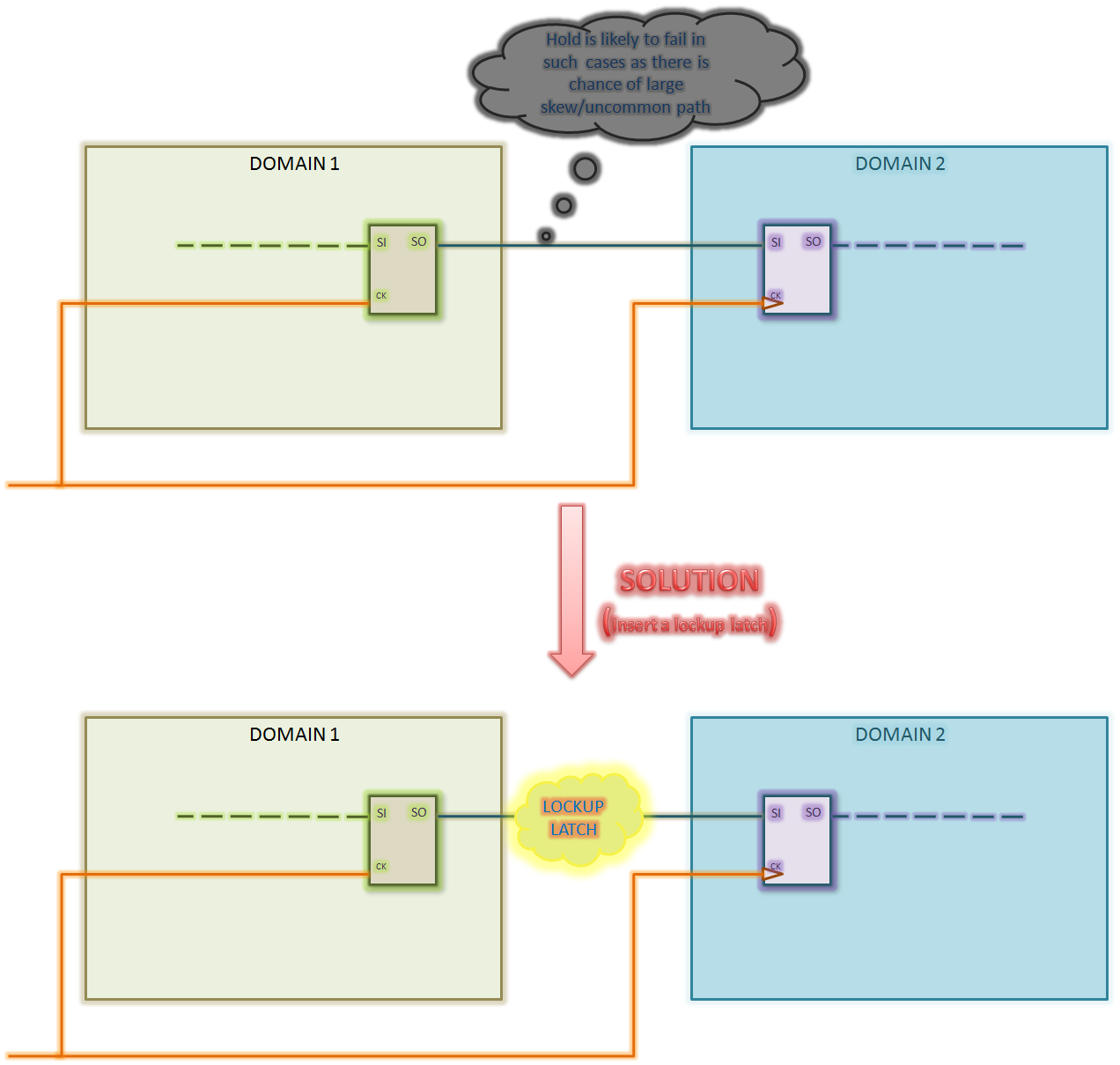

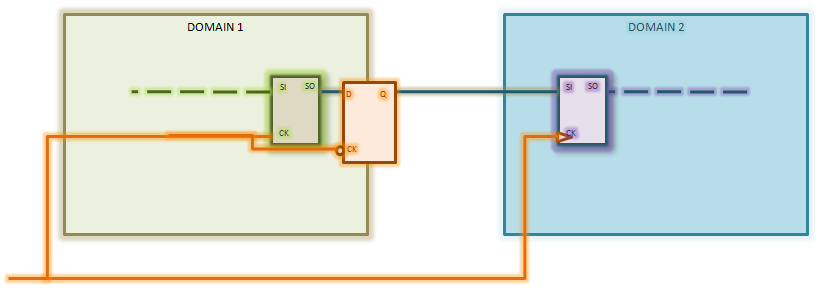

Lock-up latch is an important element in scan-based designs, especially for hold timing closure of shift modes. Lock-up latches are necessary to avoid skew problems during shift phase of scan-based testing. A lock-up latch is nothing more than a transparent latch used intelligently in the places where clock skew is very large and meeting hold timing is a challenge due to large uncommon clock path. That is why, lockup latches are used to connect two flops in scan chain having excessive clock skews/uncommon clock paths as the probability of hold failure is high in such cases. For instances, the launching and capturing flops may belong to two different domains (as shown in figure below). Functionally, they might not be interacting. Hence, the clock of these two domains will not be balanced and will have large uncommon path. But in scan-shift mode, these interact shifting the data in and out. Had there been no lockup latches, it would have been very difficult for STA engineer to close timing in a scan chain across domains. Also, probability of chip failure would have been high as there a large uncommon path between the clocks of the two flops leading to large on-chip-variations. That is why; lockup latches can be referred as as the soul mate of scan-based designs.

锁定锁存器是基于扫描的设计中的一个重要元素,尤其用于解决移位模式下的保持时序收敛问题。在基于扫描的测试的移位阶段,为了避免时钟偏移问题,锁定锁存器是必不可少的。锁定锁存器本质上是一种透明锁存器,它被巧妙地应用在时钟偏移极大、且由于存在较长的非公共时钟路径而导致保持时序难以满足的场景中。这就是为什么锁定锁存器被用于连接扫描链中那些时钟偏移过大或存在非公共时钟路径的两个触发器,因为在这种情况下,保持时序失败的概率很高。例如,发射触发器和捕获触发器可能属于两个不同的时钟域(如下图所示)。在功能模式下,它们可能不会相互作用。因此,这两个时钟域的时钟不会被平衡,会存在较长的非公共路径。但在扫描移位模式下,它们需要相互作用以实现数据的移入和移出。如果没有锁定锁存器,STA工程师要在跨时钟域的扫描链中实现时序收敛会非常困难。此外,由于两个触发器的时钟之间存在较长的非公共路径,会导致较大的片上偏差,芯片失效的概率也会很高。这就是为什么锁定锁存器可以被称为基于扫描的设计的“灵魂伴侣”。

Figure 1 : Lockup latches - the soul mate of scan-based designs

图 1:锁定锁存器——基于扫描的设计的灵魂伴侣

Where to use a lock-up latch

何时使用锁定锁存器

As mentioned above, a lock-up latch is used where there is high probability of hold failure in scan-shift modes. So, possible scenarios where lockup latches are to be inserted are:

如上所述,锁定锁存器用于在扫描移位模式下保持时序失败概率较高的场景。因此,需要插入锁定锁存器的可能场景如下:

- Scan chains from different clock domains: In this case, since, the two domains do not interact functionally, so both the clock skew and uncommon clock path will be large.

不同时钟域的扫描链:在这种情况下,由于两个时钟域在功能上不相互作用,因此时钟偏移和非公共时钟路径都会很大。 - Flops within same domain, but at remote places: Flops within a scan chain which are at remote places are likely to have more uncommon clock path.

同一时钟域内但位置较远的触发器:扫描链中位置较远的触发器可能具有更长的非公共时钟路径。

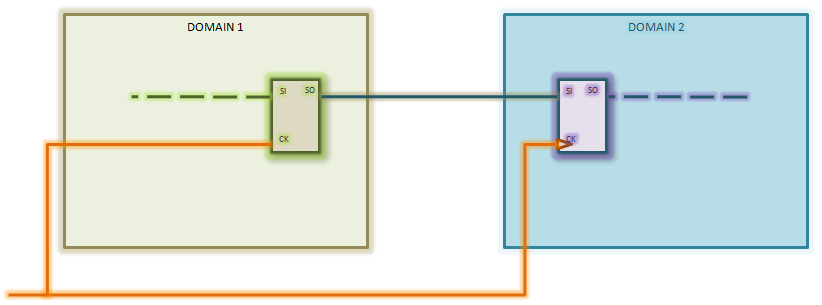

In both the above mentioned cases, there is a great chance that the skew between the launch and capture clocks will be high. There is both the probability of launch and capture clocks having greater latency. If the capture clock has greater latency than launch clock, then the hold check will be as shown in timing diagram in figure 3. If the skew difference is large, it will be a tough task to meet the hold timing without lockup latches.

在上述两种情况下,发射时钟和捕获时钟之间的偏移很可能会很大。发射时钟和捕获时钟都有可能具有较大的延迟。如果捕获时钟的延迟大于发射时钟的延迟,那么保持时序检查的情况将如图 3 的时序图所示。如果偏移差异很大,那么在没有锁定锁存器的情况下,要满足保持时序会非常困难。

Figure 2: A path crossing from domain 1 to domain 2 (scope for a lock-up latch insertion)

图 2:从时钟域 1 到时钟域 2 的路径(可插入锁定锁存器的场景)

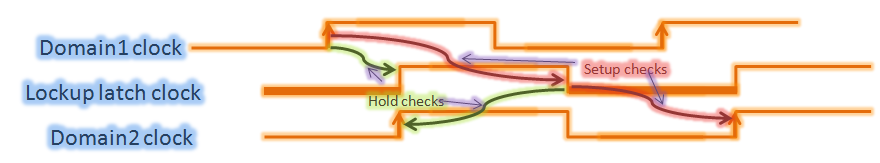

Figure 3: Timing diagram showing setup and hold checks for path crossing from domain 1 to domain 2

图 3:跨时钟域 1 到时钟域 2 的路径的建立和保持时序检查时序图

Positive or negative level latch?

使用高电平锁存还是低电平锁存?

It depends on the path you are inserting a lock-up latch. Since, lock-up latches are inserted for hold timing; these are not needed where the path starts at a positive edge-triggered flop and ends at a negative edge-triggered flop. It is to be noted that you will never find scan paths originating at positive edge-triggered flop and ending at negative edge-triggered flop due to DFT specific reasons. Similarly, these are not needed where path starts at a negative edge-triggered flop and ends at a positive edge-triggered flop. For rest two kinds of flop-to-flop paths, lockup latches are required. The polarity of the lockup latch needs to be such that it remains open during the inactive phase of the clock. Hence,

这取决于插入锁定锁存器的路径。由于插入锁定锁存器是为了解决保持时序问题,因此在路径始于正边沿触发触发器且终于负边沿触发触发器的情况下,不需要锁定锁存器。需要注意的是,由于可测性设计(DFT)的特定原因,你永远不会发现扫描路径始于正边沿触发触发器且终于负边沿触发触发器。同样,在路径始于负边沿触发触发器且终于正边沿触发触发器的情况下,也不需要锁定锁存器。对于其余两种触发器到触发器的路径,则需要锁定锁存器。锁定锁存器的极性需要满足在时钟的无效阶段保持开放(透明)。因此:

- For flops triggering on positive edge of the clock, you need to have latch transparent when clock is low (negative level-sensitive lockup latch)

对于正边沿触发的触发器,需要锁存器在时钟为低电平时保持透明(低电平敏感锁定锁存器) - For flops triggering on negative edge of the clock, you need to have latch transparent when clock is high (positive level-sensitive lockup latch)

对于负边沿触发的触发器,需要锁存器在时钟为高电平时保持透明(高电平敏感锁定锁存器)

Who inserts a lock-up latch

谁来插入锁定锁存器

These days, tools exist that automatically add lockup latches where a scan chain is crossing domains. However, for cases where a lockup latch is to be inserted in an intra-domain scan chain (i.e. for flops having uncommon path), it has to be inserted during physical implementation itself as physical information is not feasible during scan chain implementation (scan chain implementation is carried out at the synthesis stage itself).

如今,已有工具可以在扫描链跨时钟域时自动添加锁定锁存器。然而,对于需要在域内扫描链中(即对于存在非公共路径的触发器)插入锁定锁存器的情况,由于在扫描链实现阶段(扫描链实现是在综合阶段进行的)无法获取物理信息,因此必须在物理实现阶段插入锁定锁存器。

Which clock should be connected to lock-up latch

锁定锁存器应连接哪个时钟

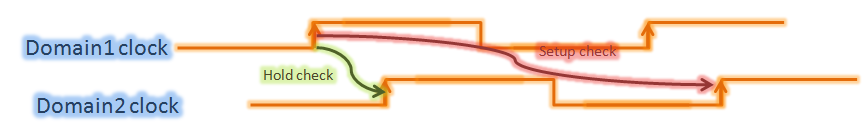

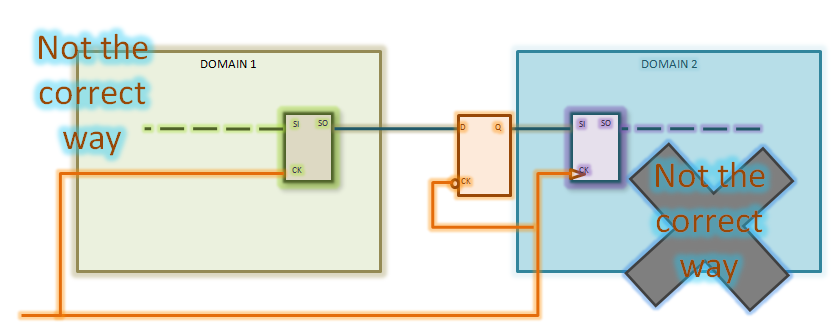

There are two possible ways in which we can connect the clock pin of the lockup latch inserted. It can either have same clock as launching flop or capturing flop. Connecting the clock pin of lockup latch to clock of capturing flop will not solve the problem as discussed below.

插入的锁定锁存器的时钟引脚有两种可能的连接方式。它可以与发射触发器的时钟相同,也可以与捕获触发器的时钟相同。如下所述,将锁定锁存器的时钟引脚连接到捕获触发器的时钟并不能解决问题。

Lock-up latch and capturing flop having the same clock (Will not solve the problem):

锁定锁存器与捕获触发器使用相同的时钟(无法解决问题)

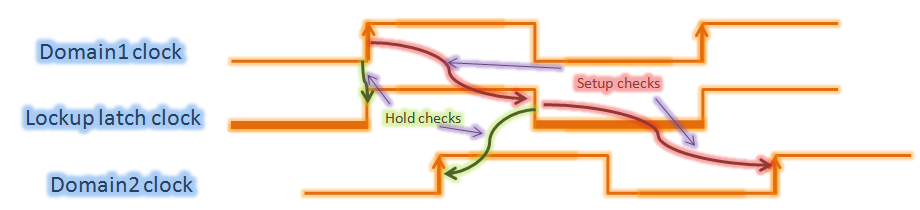

In this case, the setup and hold checks will be as shown in figure 5. As is apparent from the waveforms, the hold check between domain1 flop and lockup latch is still the same as it was between domain 1 flop and domain 2 flop before. So, this is not the correct way to insert lockup latch.

在这种情况下,建立和保持时序检查将如图 5 所示。从波形中可以明显看出,时钟域 1 触发器与锁定锁存器之间的保持时序检查仍然与之前时钟域 1 触发器和时钟域 2 触发器之间的保持时序检查相同。因此,这不是插入锁定锁存器的正确方式。

Figure 4: Lock-up latch clock pin connected to clock of capturing flop

图 4:锁定锁存器时钟引脚连接到捕获触发器的时钟

Figure 5: Timing diagrams for figure 4

图 5:图 4 的时序图

Lock-up latch and launching flop having the same clock:

锁定锁存器与发射触发器使用相同的时钟

As shown in figure 7, connecting the lockup latch to launch flop’s clock causes the skew to reduce between the domain1 flop and lockup latch. This hold check can be easily met as both skew and uncommon clock path is low. The hold check between lockup latch and domain2 flop is already relaxed as it is half cycle check. So, we can say that the correct way to insert a lockup latch is to insert it closer to launching flop and connect the launch domain clock to its clock pin.

如图 7 所示,将锁定锁存器连接到发射触发器的时钟会减小时钟域 1 触发器与锁定锁存器之间的偏移。由于偏移和非公共时钟路径都较小,这种情况下的保持时序检查很容易满足。锁定锁存器与时钟域 2 触发器之间的保持时序检查由于是半周期检查,本身就较为宽松。因此,可以说插入锁定锁存器的正确方式是将其插入到靠近发射触发器的位置,并将发射域的时钟连接到其时钟引脚。

Figure 6: Lock-up latch clock pin connected to clock of launch flop

图 6:锁定锁存器时钟引脚连接到发射触发器的时钟

Figure 7: Waveforms for figure 6

图 7:图 6 的波形图

Why don’t we add buffers

为什么不添加缓冲器

If the clock skew is large at places, it will take a number of buffers to meet hold requirement. In normal scenario, the number of buffers will become so large that it will become a concern for power and area. Also, since skew/uncommon clock path is large, the variation due to OCV will be high. So, it is recommended to have a bigger margin for hold while signing it off for timing. Lock-up latch provides an area and power efficient solution for what a number of buffers together will not be able to achieve.

如果某些地方的时钟偏移很大,那么需要大量的缓冲器才能满足保持时序要求。在正常情况下,缓冲器的数量会变得非常多,这将引发功耗和面积方面的问题。此外,由于偏移/非公共时钟路径较大,片上偏差(OCV)导致的变化也会较大。因此,在进行时序签核时,建议为保持时序预留更大的余量。锁定锁存器提供了一种面积和功耗都更高效的解决方案,而这是大量缓冲器所无法实现的。

Advantages of inserting lockup latches

插入锁定锁存器的优势

- Inserting lock-up latches helps in easier hold timing closure for scan-shift mode

插入锁定锁存器有助于更轻松地实现扫描移位模式下的保持时序收敛 - Robust method of hold timing closure where uncommon path is high between launch and capture flops

在发射触发器和捕获触发器之间存在较长非公共路径的情况下,是一种可靠的保持时序收敛方法 - Power efficient and area efficient

具有功耗和面积效率 - It improves yield as it enables the device to handle more variations.

它能提高良率,因为它使器件能够应对更多的变化。

Lockup registers: Instead of latches, registers can also be used as lockup elements; however, they have their own advantages and disadvantages. Please refer to Lockup latches vs. lockup registers : what to chose for a comparative study of using lockup latches vs lockup registers.

锁定寄存器:除了锁存器,寄存器也可以用作锁定元件,但它们各有优缺点。有关锁定锁存器与锁定寄存器的对比研究,请参考《锁定锁存器与锁定寄存器:该如何选择》。

Lockup latches vs. lockup registers: what to choose

锁定锁存器与锁定寄存器:如何选择

Both lockup latches and lockup registers are used to make scan chain robust to hold failures. What one uses for the same depends upon his/her priorities and the situation. However, it seems lockup latches are more prevalent in designs of today. This might be due to following reasons:

锁定锁存器和锁定寄存器都用于增强扫描链对保持时序失效的鲁棒性。具体选择使用哪一种取决于设计人员的优先级和具体情况。然而,在当今的设计中,锁定锁存器似乎更为常见,这可能基于以下原因:

- Area: As we know, a latch occupies only half the area as a register. So, using lockup latches instead of lockup registers gives us area and power advantage; i.e., less overhead.

面积:如我们所知,一个锁存器占用的面积仅为寄存器的一半。因此,使用锁定锁存器而非锁定寄存器能够带来面积和功耗上的优势,即开销更小。

- Timing: Lockup elements – timing perspective has given an analysis of how timing critical lockup elements (lockup latches and lockup registers) paths can be. According to it, using a negative lockup latch, you don’t have to meet timing at functional (at-speed) frequency. However, in all other cases, you need to meet timing. This might also be a reason people prefer lockup latches.

时序:锁定元件——时序视角分析了锁定元件(锁定锁存器和锁定寄存器)路径的时序关键程度。根据该分析,使用负电平敏感的锁定锁存器时,无需满足功能模式(全速)下的时序要求。然而,在其他所有情况下,则需要满足时序要求。这也可能是人们更倾向于使用锁定锁存器的原因之一。Lockup latches, on one hand relax only one side hold. So, you can afford to have skew only on one side, either on launch or on capture. Lockup registers, on the other hand, let you have skew on both the sides. So, lockup latches are preferable where you can afford to have tap on the clock either from launch flop or on capture flop. On the other hand, lockup flops can be used by tapping clock from any point as long as you meet setup and hold timings.

锁定锁存器仅放宽一侧的保持时序要求。因此,时钟偏移只能存在于一侧,即发射端或捕获端。而锁定寄存器则允许两侧都存在时钟偏移。因此,当你能够从发射触发器或捕获触发器之一获取时钟时,锁定锁存器是更优选择。另一方面,只要满足建立和保持时序要求,锁定寄存器可以从任意点获取时钟。

References:

参考文献:

- “Why not add buffer but lockup latch” - 《为什么添加的是锁定锁存器而不是缓冲器》

http://www.edaboard.com/thread82364.html

数字电路基础:关于锁存器 latch

风中少年01 于 2019-09-05 23:01:12 发布

锁存器是电平触发的控制器件,这与边沿触发的触发器有本质区别。锁存器是异步时序电路系统中对输入信号电平敏感的单元,用于存储信息。一个锁存器可存储 1 bit 信息,通常多个锁存器会一起出现,如 4 位锁存器、8 位锁存器。锁存器在数据未锁存时,输出端的信号随输入信号变化,就像信号通过一个缓冲器;一旦锁存信号有效,则数据被锁存,输入信号不起作用。因此,锁存器也被称为透明锁存器,指的是不锁存时输出对输入是透明的。

与触发器的区别:两者都是基本存储单元,但锁存器是电平触发的存储器,触发器是边沿触发的存储器。本质上,两者的基本功能相同,均可存储数据。锁存器用于组合逻辑,触发器用于时序电路(时钟触发)。

Verilog 对锁存器的描述(建模):

常见的锁存器包括三个端口:数据输入口、数据输出口。

always @(E or D)

beginif(E)Q = D ;

end

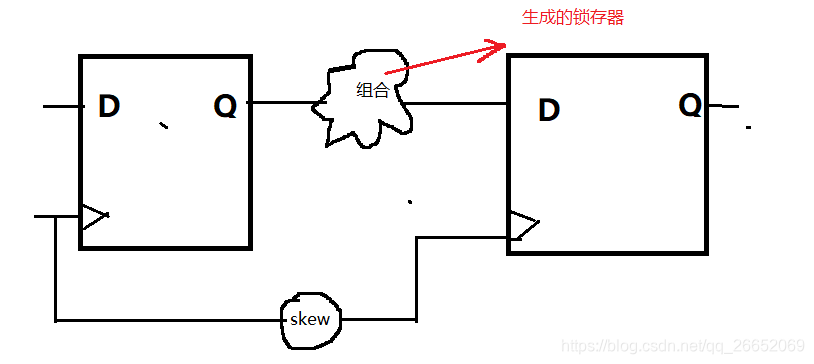

1. 什么情况下会生成锁存器?

在组合逻辑中,若存在某个信号需要保持不变,则会生成锁存器。

以下为几个 Verilog 描述示例:

描述方式 1:

always@(*)

beginif(sl)beginq = a ;end

end

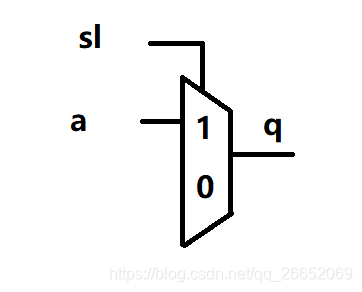

根据组合逻辑的描述,假设生成如下选择器,即 sl=1 时,q=a,如下所示:

描述方式 2:

需要注意的是,上述 Verilog 描述中隐含了 else 分支,即当 sl=0 时,q 保持不变(q=q),因此该 Verilog 描述与以下描述等效:

always@(*)

beginif(sl)beginq = a ;endelsebeginq = q ;end

end

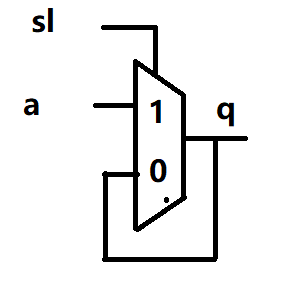

如何实现这一功能?最直接的想法似乎是采用如下电路:

这是不允许的,组合逻辑中不能有回路,要求均为正向路径。严格来说,Verilog 描述组合逻辑“有反馈”时,代码可被编译并实现为组合电路,但编译器会给出警告,因为该代码的结果没有实际意义,无法确定结果。

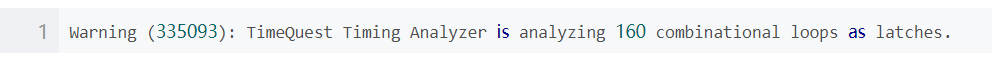

原因:TimeQuest 时序分析器发现使用非最佳资源(具有组合反馈的查找表(LUT))实现锁存器。TimeQuest 分析器用等效的锁存器替换组合循环。TimeQuest 分析器将此逻辑视为异步端点,且不会分析通过该节点的路径。

操作:必须使用异步加载数据信号的寄存器来实现这些锁存器,或者从设计中删除它们。有关更多信息,请在 TimeQuest 分析器中运行 check_timing tcl 命令。

以加法为例,生成的加法电路会执行几次?是否会一直加?如何控制?

描述方式 3:

always@(*)

begina = a + 1;

end

尝试综合时,综合工具会将 Latch 优化掉,这会导致前、后仿真结果不一致。

描述方式 4:

always @ (A,B)C = A & B;

只要 A 或 B 有变化,就会触发对 C 的赋值。

描述方式 5:

always@(*)

begincase(d)2'b00: a=b>>1; // 此处未对 C 描述,因此 C 保持不变,会生成锁存器2'b11: c=b>>1;// a 保持不变default:begina = b ;c = b;end

end

一篇博文中提到一个值得注意的问题:

在如下设计中,采用时序逻辑设计却生成了锁存器。

module Decode(

input A,

input B,

input C,

output reg[31:0] edata,

output reg[31:0] eCapData,

input bCap,

output reg CapSt,

input n_rst,

input [31:0] rstVal,

input clk);reg[1:0] state;always@(posedge clk or negedge n_rst)

beginif(!n_rst)beginedata <= rstVal;state <= {A,C};endelsebeginstate <= {A,B};edata <= {31'd0,A};*****此处省略一万*****end

分析得出的原因:表面上按照触发器的方式编写代码,实则不然。在异步复位代码段中,输出仍由外界输入决定,因此综合后产生了锁存器。

将代码修改如下,问题得以解决:

module Decode(

input A,

input B,

input C,

output reg[31:0] edata,

output reg[31:0] eCapData,

input bCap,

output reg CapSt,

input n_rst,

input [31:0] rstVal,

input clk);reg[1:0] state;always@(posedge clk or negedge n_rst)

beginif(!n_rst)beginedata <= 32'd0;state <= 2'd0;endelsebeginstate <= {A,B};edata <= {31'd0,A};*****此处省略一万*****end

2. 锁存器的危害?

首先需要说明,latch 并非完全有害,否则 FPGA 中不会同时存在 latch 和 flip-flop(例如,在支持 DDR 的 IOB 中,利用 latch 实现 DDIO)。那么,为什么锁存器比触发器节省面积,却仍要避免使用 latch 而采用触发器呢?

对时序分析的影响:

应尽可能避免使用或生成锁存器,主要因为锁存器的存在不利于时序分析。下图中,若组合逻辑不生成 latch,分析时序是否符合要求时,可根据寄存器输出延迟 Tco、组合逻辑延迟 Tcomb、触发器建立时间 Ts 进行分析,要求总延迟不超过时钟周期,这是可预知的。若两个触发器间的组合逻辑中生成了 latch,由于 latch 是电平触发(而非时钟边沿触发),可能在时钟有效沿之间被触发,导致无法确定 latch 输出的高低电平(与时钟不同步),这是由锁存器的特性决定的。而采用 D 触发器时,分析只需考虑触发器之间的路径即可。

另一种说法:

锁存器为电平触发,无效电平时锁存,有效电平时输入直接反应到输出,由于延时不同容易产生毛刺。组合逻辑中数据不需要锁存,应避免产生锁存器。FPGA 资源中没有锁存器,需用触发器加逻辑门构成,消耗较多逻辑资源;但有时为满足一些规范协议,会用到锁存器,因此 FPGA 中使用较少。而在 ASIC 设计中,由于锁存器结构较简单、传输速度快,可有效提高集成度,因此使用较多。

总结:

- 对毛刺敏感,不能异步复位,上电后状态不确定;

- Latch 会使静态时序分析变得非常复杂;

- 在 PLD 芯片中,基本单元由查找表和触发器组成,生成锁存器反而消耗更多资源(这是最基本的原因)。

3. 如何避免生成锁存器

组合逻辑生成锁存器的原因是逻辑中存在需要保持不变的信号,而组合逻辑不能有环路(即反馈),因此通过生成锁存器实现信号保持。

可从以下两个角度入手避免生成锁存器:

(1)采用时序逻辑,即在组合逻辑中插入触发器,多用触发器实现信号寄存;

(2)尽可能避免组合逻辑中存在需要保持不变的信号,或避免组合逻辑存在环路。

【注】:

常说组合逻辑中 if-else 语句不要省略 else,case 语句条件分支不要缺省,否则容易产生锁存器。其本质是避免出现信号保持不变的情况,因为缺省后默认信号保持不变。组合逻辑中 if 语句缺省 else 会导致 else 时信号保持不变,从而生成锁存器;但如果组合逻辑中 if-else 语句的 else 分支仍描述信号保持不变,则即使有 else 依旧会生成锁存器。

引用一篇博文中的总结:

简述组合逻辑的注意事项:

(1)避免组合逻辑反馈环路(容易产生毛刺、振荡、时序违规等)。

解决方法:A. 牢记任何反馈回路必须包含寄存器;B. 检查综合、实现报告的 warning 信息,发现反馈回路(combinational loops)后进行相应修改。

(2)替换延迟链。

解决方法:用倍频、分频或者同步计数器实现。

(3)替换异步脉冲产生单元(毛刺生成器)。

解决方法:用同步时序设计脉冲电路。

(4)慎用锁存器。

解决方法:

A、使用完备的 if…else 语句;

B、检查设计中是否含有组合逻辑反馈环路;

C、对每个输入条件设计输出操作,对 case 语句设置 default 操作(特别是在状态机设计中,最好有一个 default 的状态转移,且每个状态最好有一个 default 的操作)。

D、如果使用 case 语句,特别是在设计状态机时,尽量附加综合约束属性,综合为完全条件 case 语句。

小技巧:仔细检查综合器的综合报告,目前大多数综合器会对综合出的 latch 报“warning”,通过综合报告可较方便地找出无意中生成的 latch。

数字电路基础——锁存器

Oliver-H 已于 2024-04-07 15:06:52 修改

锁存器

锁存器(通常称为 Latch) 是数字电路中一种具有记忆功能的逻辑元件。锁存器是对脉冲电平敏感的存储单元电路,它仅在输入脉冲的高电平(或低电平)期间对输入信号敏感并改变状态。在数字电路中,锁存器可记录二进制数字信号“0”和“1”。

1、简介

锁存器(latch)是电平触发的存储单元,数据存储的动作取决于输入时钟(或使能)信号的电平值,仅当锁存器处于使能状态时,输出才会随数据输入发生变化。

锁存器不同于触发器,锁存器在不锁存数据时,输出端的信号随输入信号变化,就像信号通过一个缓冲器一样;一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。因此,锁存器也称为透明锁存器,指的是不锁存时输出对输入是透明的。

锁存器的分类包括 RS 锁存器、门控 RS 锁存器和 D 锁存器,此处我们详细介绍 D 锁存器。

什么是 D 锁存器?

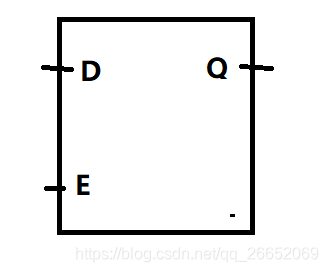

D 锁存器是能够将输入的单路数据 D 存入锁存器的电路,其电路图如下所示。

从 D 锁存器的电路图可以看出,该电路主要由两个部分组成:第一部分是由 G1、G2 两个与非门组成的 RS 锁存器,第二部分是由 G3、G4 两个与非门组成的控制电路。C 为控制信号,用于控制 G3 和 G4 的激励输入。

下面分析 D 锁存器的工作原理:

当控制信号 C=0 时,根据与非门的逻辑定律,无论 D 输入什么信号,RD 和 SD 信号均为 1。根据由与非门组成的 RS 锁存器的逻辑定律,当 RD 和 SD 同时为 1 时,锁存器的输出端 Q 将维持原状态不变。

当控制端 C=1 时,若 D=0,则 SD=1、RD=0,根据 RS 锁存器的逻辑规律,电路的状态为 0;若 D=1,则 RD=1、SD=0,锁存器的状态为 1。也就是说,此时锁存器的状态由激励输入端 D 确定,且 D 的值即为锁存器的状态,这就是前面所说的将单路数据 D 存入锁存器。

根据上述描述,可推出 D 锁存器的特性表(Qn 指触发器当前逻辑状态,即触发前的状态;Qn+1 指触发后的状态)。

由该表可知,当 C=1 时,D 的状态与 Qn+1 的状态完全一致:当 D=0 时,Qn+1=0;当 D=1 时,Qn+1=1。

D 锁存器的波形图如下所示。

从 D 锁存器的波形图可以看出,D 是锁存器的输入信号,C 是锁存器的控制信号,Q 是锁存器的输出信号。当控制信号 C 为高电平时,输出信号 Q 随输入信号 D 的变化而变化(如虚线内所示,Q 的波形与 D 的波形一致)。当控制信号 C 从高电平变为低电平时,输入信号 D 的状态决定锁存器将要锁存的状态。例如,C 由高变低的两条虚线内,对应的输入信号 D 为低电平,则输出信号 Q 锁存低电平;最后两条虚线内,D 为高电平,则 Q 锁存高电平。

下面从实际逻辑设计的角度分析锁存器的弊端。

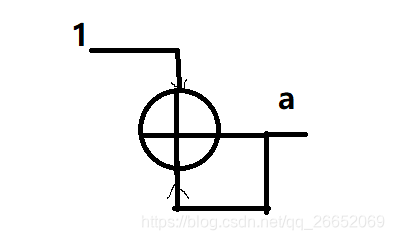

在绝大多数设计中,应避免产生锁存器。锁存器会导致设计的时序出现问题,且其隐蔽性较强,新手难以排查。锁存器最大的危害在于无法过滤毛刺,且会影响工具进行时序分析,这对下一级电路极其危险。因此,只要能用触发器的地方,就不使用锁存器。

由上图可知,锁存器没有时钟信号,只有数据输入、使能及输出 q 端。由于没有时钟信号,无法对该器件进行时序分析,这在时序电路中是非常危险的,可能导致时序不满足,进而使电路功能无法实现。

2、实验任务

设计一个锁存器电路。

3、程序设计

代码中出现 latch 的两个原因:在组合逻辑中,if 或 case 语句描述不完整(如 if 缺少 else 分支,case 缺少 default 分支),导致代码在综合过程中产生 latch。解决办法是 if 必须带 else 分支,case 必须带 default 分支。

需要注意的是,仅当不带时钟的 always 语句中 if 或 case 语句描述不完整时,才会产生 latch;带时钟的语句中,if 或 case 语句描述不完整不会产生 latch。

3.1 缺少 else 分支的锁存器代码

根据程序设计思路,设计一个缺少 else 分支的 if 语句的锁存器代码(latch.v)如下:

//实验任务:设计一个锁存器电路

//程序设计:

//代码中出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//需要注意的是,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//***

//** main code

//***always @(*) beginif(a==1)y=b;//else// y=0;

endendmodule

上述组合逻辑电路使用了 if 语句,但缺少 else 分支,通过 Vivado 查看其 RTL 视图如下。

从 RTL ANALYSIS 视图可以看出,模块下显示 RTL_LATCH,表明该电路为 latch。

3.2 补齐 else 分支

补充 else 分支后,电路结构如下,代码如下:

//实验任务:设计一个锁存器电路

//程序设计:

//代码中出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//需要注意的是,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//***

//** main code

//***always @(*) beginif(a==1)y=b;elsey=0;

endendmodule

添加 else 分支后,通过 RTL ANALYSIS 视图查看综合的电路结构如下。

上图所示电路结构为一个 mux 选择电路,表明添加 else 分支后,电路不会产生 latch。

3.3 缺少 default 的 case 语句的锁存器代码

下面编写一个不带 default 的 case 语句,代码如下:

//////////////////////////////////////////////////////////////////////////////////

//实验任务:设计一个锁存器电路

//程序设计:

//代码中出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//需要注意的是,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//***

//** main code

//***always @(*) begin

// if(a==1)

// y=b;

// //else

// // y=0;case(a)0:y = b;endcase

endendmodule

从 RTL ANALYSIS 视图可以看出,模块下显示 RTL_LATCH,表明该电路为 latch。

3.4 补齐 default 的 case 语句

补充 case 语句的 default 分支后,电路结构如下,代码如下:

//////////////////////////////////////////////////////////////////////////////////

//实验任务:设计一个锁存器电路

//程序设计:

//代码中出现 latch 的两个原因:在组合逻辑中,if 或者 case 语句不完整的描述,

//比如 if 缺少 else 分支,case 缺少 default 分支,导致代码在综合过程中出现了 latch。

//解决办法就是 if 必须带 else 分支,case 必须带 default 分支。

//需要注意的是,只有不带时钟的 always 语句的 if 或者 case 语句不完整才会产生 latch,

//带时钟的语句 if 或者 case 语句不完整描述不会产生 latch。module latch(//input clk, //system clkinput a,input b,output reg y // output signal);//***

//** main code

//***always @(*) begin

// if(a==1)

// y=b;

// //else

// // y=0;case(a)0:y = b;default:y = 0;endcase

endendmodule

该语句包含 case 的 default 分支,通过 Vivado 的 RTL ANALYSIS 查看综合的电路结构如下。

上图所示电路结构为一个 mux 选择电路,表明添加 case 的 default 分支后,电路不会产生 latch。

4、本章总结

重点掌握:组合逻辑中代码出现 latch 的原因是 if 语句或 case 语句描述不完整(如 if 缺少 else 分支,case 缺少 default 分支),导致代码在综合过程中产生 latch。解决办法是 if 必须带 else 分支,case 必须带 default 分支。

需要注意的是,仅当不带时钟的 always 语句中 if 或 case 语句描述不完整时,才会产生 latch;带时钟的语句中,if 或 case 语句描述不完整不会产生 latch。

数字电路中的锁存器(latch)和各种触发器(flip-flop)

Cheeky_man 原创于 2021-08-10 22:33:46 发布

电平敏感的存储器件称为锁存器。可分为高电平锁存器和低电平锁存器,用于不同时钟之间的信号同步。

- 有交叉耦合的门构成的双稳态的存储原件称为触发器。分为上升沿触发和下降沿触发,可以认为是两个不同电平敏感的锁存器串连而成。前一个锁存器决定了触发器的建立时间,后一个锁存器则决定了保持时间。

一、SR 锁存器 (保持电路状态,具备记忆功能)

SR 锁存器是各种触发器电路的基本构成部分。与触发器的区别之一是输出是由输入的置 1 或置 0 信号直接完成的,而不需要触发信号的触发。

1、SR 锁存器工作原理

用或非门组成的 SR 锁存器状态分析

-

当 SD=1S_D = 1SD=1、RD=0R_D = 0RD=0 时,Q=1Q = 1Q=1、Q′=0Q' = 0Q′=0。在 SD=1S_D = 1SD=1 信号消失以后(即 SDS_DSD 回到 0 ),由于有 QQQ 端的高电平接回到 G2 的另一个输入端,因而电路的 1 状态得以保持。

-

当 SD=0S_D = 0SD=0、RD=1R_D = 1RD=1 时,Q=0Q = 0Q=0、Q′=1Q' = 1Q′=1。在 RD=1R_D = 1RD=1 信号消失以后,电路保持 0 状态不变。

-

当 SD=RD=0S_D = R_D = 0SD=RD=0 时,电路维持原来的状态不变。

-

当 SD=RD=1S_D = R_D = 1SD=RD=1 时,Q=Q′=0Q = Q' = 0Q=Q′=0,这既不是定义的 1 状态,也不是定义的 0 状态。而且,在 SDS_DSD 和 RDR_DRD 同时回到 0 以后无法断定锁存器将回到 1 状态还是 0 状态。

-

因此,在正常工作时输入信号应遵守 SDRD=0S_D R_D = 0SDRD=0 的约束条件,亦即不允许输入 SD=RD=1S_D = R_D = 1SD=RD=1 的信号。

SR 锁存器也可以用与非门构成,如下图所示。这个电路是以低电平作为输入信号的,所以用 SD′S_D'SD′ 和 RD′R_D'RD′,分别表示置 1 输入端和置 0 输入端。在右下图所示的图形符号上,用输入端的小圆圈表示用低电平作输入信号,或者称低电平有效。

用与非门组成的锁存器

2、SR 锁存器的真值表

两种 SR 触发器的特性表

QQQ 表示输入变化之前的输出, Q∗Q^*Q∗ 表示输入变化之后的输出

3、SR 触发器的特性方程

{Q∗=S+R′QSR=0(约束条件)\left\{ \begin{align*} & Q^*=S+R'Q \\ & SR=0\left(约束条件 \right) \\ \end{align*} \right. {Q∗=S+R′QSR=0(约束条件)

二、触发器

- 触发器与锁存器的不同在于,它除了置 1、置 0 输入端以外,又增加了一个触发信号输人端。只有当触发信号到来时,触发器才能按照输入的置 1、置 0 信号置成相应的状态,并保持下去。我们将这个触发信号称为时钟信号(CLOCK),记作 CLK。当系统中有多个触发器需要同时动作时,就可以用同一个时钟信号作为同步控制信号了。

- 触发信号的工作方式可以分为电平触发、边沿触发和脉冲触发三种。下面将会看到,在不同的触发方式下,触发器的动作过程各具有不同的动作特点。掌握这些动作特点,对于正确使用触发器是十分必要的。

1、电平触发的触发器

电路结构:

由两部分组成:SR 锁存器(与非门 G1、G2 构成)+ 输入控制电路(两个与非门 G3、G4 构成)

电平触发 SR 触发器(门控 SR 锁存器)

工作原理:

- 由图可知,当CLK=0 时,门 G3、G4 的输出始终停留在 1 状态,S、R 端的信号无法通过 G3、G4 而影响输出状态,故输出保持原来的状态不变。

- 只有当触发信号 CLK 变成高电平以后,S、R 信号才能通过门 G3、G4 加到由门 G1、G2 组成的锁存器上,“触发” 电路发生变化,使 Q 和 Q’ 根据 S、 R 信号而改变状态。因此,将 CLK 的这种控制方式称为电平触发方式。

2、 电平触发的 D 触发器 ——D 型锁存器

将上左图改接成下左图的形式,得到电平触发的 D 触发器(D 型锁存器)

电平触发的 D 触发器

- 由图可见,若 D=1,则 CLK 变为高电平以后触发器被置成 Q=1,CLK 回到低电平以后触发器保持 1 状态不变。

- 若 D=0,则 CLK 变为高电平以后触发器被置成 Q=0,CLK 回到低电平以后触发器保持 0 状态不变。因为它仍然工作在电平触发方式下,所以同样具有电平触发的动作特点。

它的特性表如下表所示。

因为在 CLK 的有效电平期间输出状态始终跟随输入状态变化,输出与输入的状态保持相同,所以又将这个电路称为 “透明的 D 型锁存器”(Transparent D-Latch)。

3、边沿触发的触发器

3.1 电路结构和工作原理

- 为了提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于 CLK 信号下降沿(或上升沿)到达时刻输入信号的状态。而在此之前和之后输入状态的变化对触发器的次态没有影响。

- 为实现这一设想,人们相继研制成了各种边沿触发(edge-triggered)的触发器电路。目前已用于数字集成电路产品中的边沿触发器电路有:

- 用两个电平触发 D 触发器构成的边沿触发器、维持阻塞触发器、利用门电路传输延迟时间的边沿触发器等几种较为常见的电路结构形式。

下图是用两个电平触发 D 触发器组成边沿触发 D 触发器的原理性框图,图中的 FF1 和 FF2 是两个电平触发的 D 触发器(也称为 D 型锁存器)。

用两个 D 锁存器组成的边沿触发器

- 由图可见,当 CLK 处于低电平时:

- CLK1 为高电平,因而 FF1 的输出 Q1 跟随输入端 D 的状态变化,始终保持Q1=D。

- 与此同时,CLK2 为低电平,FF2 的输出Q2(也就是整个电路最后的输出 Q)保持原来的状态不变。

- 当 CLK 由低电平跳变至高电平:

- CLK1 随之变成了低电平,于是Q1 保持为 CLK 上升沿到达前瞬间输入端 D 的状态,此后不再跟随 D 的状态而改变。

- 与此同时,CLK2 跳变为高电平,使 Q2 与它的输入状态相同。由于 FF2 的输入就是 FF1 的输出 Q1,所以输出端 Q 便被置成了与 CLK 上升沿到达前瞬时 D 端相同的状态,而与以前和以后 D 端的状态无关。

3.2 边沿触发器的特性表

在图形符号中,用 CLK 输入端处框内的 “>” 表示触发器为边沿触发方式。在特性表中,则用 CLK 一栏里的 “↑” 表示边沿触发方式,而且是上升沿触发,如下表所示。

边沿触发器的特性表

3.3 边沿触发方式的动作特点

通过对上述边沿触发器工作过程的分析可以看出,边沿触发方式的动作特点,这就是触发器的次态仅取决于时钟信号的上升沿(也称为正边沿)或下降沿(也称为负边沿)到达时输入的逻辑状态,而在这以前或以后,输入信号的变化对触发器输出的状态没有影响。

4、脉冲触发的触发器

4.1 电路结构和工作原理

将边沿触发器里的两个电平触发 D 触发器(D 型锁存器)换成电平触发的 SR 触发器,如下图所示,来讨论一下它的触发过程。

脉冲触发的 SR 触发器

图(a)的电路是脉冲触发 SR 触发器的典型电路(以前也把这个电路称作主从 SR 触发器)。FF1 和 FF2 分别称为主触发器和从触发器。

- 当 CLK=0 时,FF1 保持原状态不变。

- 在 CLK 变为高电平后,CLK=1、CLK’=0,主触发器的输出 Q1将按照 S 和 R输入端信号被置成相应的状态,而从触发器保持原来的状态不变。

- 当CLK 回到低电平,亦即下降沿到来时,从触发器的输出 Q2 被置成与此刻 Q1 相同的状态,而主触发器开始保持状态不变。

由此可见,在一个时钟周期里,输出端的状态只可能改变一次,而且发生在 CLK 的下降沿。这 — 点和边沿触发器类似。

但需要注意的是,现在输入端的主触发器 FF1 是一个电平触发的 SR 触发器,而不是电平触发的 D 触发器了。

-

由于在CLK 高电平期间主触发器输出的状态可能随 S 和 R 状态的变化而发生多次翻转,输出端的状态不可能始终与输入状态保持一致。

-

因此,在脉冲触发 SR 触发器中,不能像边沿触发器那样,

仅仅根据 CLK 下降沿到来时刻输入端 S 和 R 状态确定输出端 Q 的状态,而必须考察全部 CLK=1 期间主触发器状态的变化情况。这一点就是脉冲触发方式和边沿触发方式的区别所在。(主触发器的输出≠最后的输出)

-

例如,在图(a)的电路中,当 CLK=1 期间输入信号先是 S=0、R=1,主触发器被置成 Q1=0; 随后又变为 S=1、R=0,于是主触发器被置成了 Q1=1。而在 CLK 下降沿到来之前输入又变成了 S=0、R=0,这时主触发器将保持 Q1=1 不变。这样在 CLK 下降沿到来时,输出便被置成 Q=Q1=1。

-

显然,如果只根据 CLK 下降沿到来时的输入状态,是无法正确地确定输出状态的。

-

在CLK 高电平期间输入 S、R 不变的情况下,可以列出脉冲触发 SR 触发器的特性表,如表所示。表中用 CLK 一行里的 “

” 符号表示脉冲触发方式,而且 CLK 以高电平为有效电平(即 CLK 高电平时接受输入信号),输出端状态的变化则发生在 CLK 下降沿。这种情况也称为正脉冲触发。

” 符号表示脉冲触发方式,而且 CLK 以高电平为有效电平(即 CLK 高电平时接受输入信号),输出端状态的变化则发生在 CLK 下降沿。这种情况也称为正脉冲触发。

脉冲触发的 SR 触发器的特性表

因为需要等到 CLK 的有效电平消失后(即回到低电平),输出状态才改变,故也把这种触发方式称为延迟触发。

via:

-

Lockup latch – principle, application and timing

https://vlsiuniverse.blogspot.com/2013/06/lockup-latches-soul-mate-of-scan-based.html -

Lockup latches vs. lockup registers: what to choose

https://vlsiuniverse.blogspot.com/2016/08/lockup-latches-vs-lockup-flops.html -

数字电路基础—锁存器-CSDN博客

https://blog.csdn.net/yishuihanq/article/details/131249383 -

数字电路基础:关于锁存器 latch_数字电路中latch-CSDN博客

https://blog.csdn.net/qq_26652069/article/details/100555598 -

数字电路中的锁存器(latch)和各种触发器(flip-flop)_sr锁存器真值表-CSDN博客

https://blog.csdn.net/qq_36045093/article/details/119578284 -

简述组合逻辑的注意事项 - alifpga - 博客园

https://www.cnblogs.com/alifpga/p/9352999.html