学习第一遍 -- 第一章:SoC设计绪论

本系列是基于《SoC设计方法与实现(第四版) - 魏继增、郭玮、史再峰、郭筝、谢憬 编著》

系列文章仅为学习记录,便于手机端时时复习巩固、以及进一步理解。如有侵权,请联系鄙人、鄙人将删除!另,强烈推荐本书!

感谢本书作者们的知识分享,本人是在看到别人推荐本书优秀,所以想深入学习,但怕有所遗漏、以及自己的分享欲,所以想以博文的形式记录。再次申明:如有侵权,请联系鄙人、鄙人将删除

子目录

- 第一章:SoC设计绪论

- 1.1 微电子技术概述

- 1.2 SoC概述

- 1.3 SoC设计的发展趋势及面临的挑战

- 1.3.3 未来的SoC

第一章:SoC设计绪论

1.1 微电子技术概述

-

集成电路发展的6个阶段:

- 小规模集成电路(SSI,Small-Scale Integration,12个晶体管);

- 中规模集成电路(MSI,Medium-Scale Integration,100~1000个晶体管);

- 大规模集成电路(LSI,Large-Scale Integration,1000~100_000个晶体管);

- 超大规模集成电路(VLSI,Very Large-Scale Integration,15万个晶体管);

- 特大规模集成电路(ULSI,Ultra Large-Scale Integration,1000万个晶体管);

- 巨大规模集成电路(GSI,Giga Scale Integration,1亿个晶体管)。

-

IC产业结构的3次重大变革:

- 以生产为导向的初级阶段;

- 代工厂与设计公司的崛起;

- Fabless:半导体集成电路行业中无生产线设计公司的简称。

- Foundary:芯片代工厂的简称。

- “四业分离”的IC产业;

- “四业”:设计、制造、封装、测试;

- 另一特征:系统设计和IP(Intelligent Property,知识产权)设计开始分工。

1.2 SoC概述

- SoC:System on Chip,系统级芯片,又称片上系统。

- 将系统的主要功能综合到一块芯片中。

- 定义:包括一个或多个计算“引擎”(微处理器/微控制器/数字信号处理器)、至少十万门的逻辑和相当数量的存储器。

- 分类:专用SoC芯片(ASIC);通用SoC芯片。

- 基本单元:IP,即由各种超级宏单元模块电路组成并经过验证的芯核,也可以理解为满足特定规范、并能在设计中复用的功能模块。

- SoC的优势:

- 可以实现更为复杂的系统;

- 具有较低的设计成本;

- 具有更高的可靠性;

- 缩短产品设计时间;

- 减少产品反复的次数;

- 可以满足更小尺寸的设计要求;

- 可达到低功耗的设计要求。

1.3 SoC设计的发展趋势及面临的挑战

- SoC设计技术的发展与挑战

- 设计成本(Design Cost)

- 对于SoC而言,其包含了软件和硬件两部分,不同的软硬件划分方案和实现方法决定了设计成本;

- 制造的非周期性发生费用(NRE,Non-Recurring Engineering)越来越高,主要包括掩模版(Mask)和工程师的设计费用,一旦涉及发生错误,将导致这一成本的成倍增长;

- 摩尔定律加快了设计更新的脚步,也就是缩短了产品的生命周期。相对较长的设计和验证周期增加了成本。

- IP复用和EDA工具的发展大大降低了设计成本。

- 集成密度(复杂性)

- 集成密度是指芯片单位面积上所含的元件数。

- 两方面的挑战:

- 硅器件的复杂性(指:工艺尺寸缩小及新器件结构所带来的影响,以前可以忽视的现象现在对于涉及的正确性存在着相当大的影响)

- 对于器件而言,无法确定各个参数理想的缩小比例(包括电源电压、阈值电压等);

- 尺寸缩小使得寄生电容、电感的影响无法忽略,对于制造工艺的可靠性造成一定的影响。

- 设计的复杂性

- 芯片验证更为复杂;

- 芯片测试更为复杂;

- 混合电路设计更为复杂。

- 硅器件的复杂性(指:工艺尺寸缩小及新器件结构所带来的影响,以前可以忽视的现象现在对于涉及的正确性存在着相当大的影响)

- 时序收敛

- 集成电路设计中的时序收敛一般指前后端设计时序能够达到设计需求。

- 随着工艺的进步(尺寸越来越小),线延迟占主导地位,时序收敛问题越来越严重。

- 设计工具的时序准确性不足、及版图后的时序收敛问题,已经成为成功实现这类设计项目的两大关键障碍。

- 在逻辑综合期间,用于评估互连负载和时延的基于统计扇出(Fanout)的线负载(wireload)模型,与版图设计完成后,实际的互联负载和时延之间就存在很大区别,从而导致设计的综合后和版图设计后两个版本之间缺乏可以预测的时序。

- 出现时序收敛问题时,设计工程师必须修改RTL设计或约束,重新综合并重新设计版图,大大增加了前端/后端的迭代工作,既耗时、也影响了项目的进度。(为此,必须找到一种方法,能够在设计的早期获得更加精确的时序信息。)

- 集成电路设计中的时序收敛一般指前后端设计时序能够达到设计需求。

- 信号完整性

- 信号完整性(Signal Integrity)是指一个信号在电路中产生正确的、相应的能力。

- 信号具有良好的信号完整性是指,在需要的时间段内,该信号具有所必须达到的电压电平数值。

- 在SoC设计中,信号之间的耦合作用会产生信号完整性问题,忽视信号完整性问题可能导致信号之间产生串扰,可靠性、可制造性和系统性能也会降低。

- 随着集成电路工艺制造技术的发展,导致信号串扰的机会在增加:

- 金属布线层数持续增加:随着布线层数的增加,相邻的沟道电容也会增加。

- 另外,目前复杂设计中的电路门数的剧增使得更多、更长的互连线成为必要。长的互连线不仅使得耦合电容增加,长线上的电阻也会增加,二越来越细的金属线同样也会导致电阻的增加,这是由于互连线的横断面减小的缘故。即使采用现有的铜线互连工艺也不能够解决这方面的问题,仅仅只是延缓了解决电阻问题的时间。

- 低功耗设计

- 随着制造工艺尺寸的减小,CMOS管的静态功耗(漏电)急剧增加,并且呈指数增长趋势。功耗的提高带来了一系列的现实问题及设计挑战:

- 另外,虽然电池技术已经取得了一定的进步,寿命有所延长、体积有所减小,但这些变化都跟不上下一代集成电路设计功耗迅速增加的需求。传统电源管理技术不足以使电池寿命维持到最终用户可接受的水平。

- 从宏观结构上看,IC功耗来自IC内部的各功能模块及功能模块间通信的功耗,而功能模块的划分、功能特性、数量和相互关系及任务的分配是在系统架构设计时确定的。IC的功耗是各功能模块的功耗的总和。对于性能的不同要求,对模块的功能要求就不同,从而影响IC的实现规模。功能越复杂,实现规模越大,IC的功耗就越高,所以系统架构级的设计从根本上关系到IC功耗的大小。随着ESL(电子系统级)设计方法的出现,使得在设计的早期进行软硬件协同设计成为可能,系统级设计将在低功耗设计中发挥越来越重要的作用。

- 从微观电路实现上看,集成电路的功耗主要由动态功耗和静态功耗两部分组成。目前集成电路主要以静态CMOS为主,在这类电路中,动态功耗是整个电路功耗的主要组成部分;其次是静态功耗,随着工艺尺寸的不断减小,泄漏电流消耗的功率所占的比重越来越大,成为IC功耗的主要来源。如何降低泄漏电流功耗又成为一个棘手的问题。因此,对于设计人员来讲,需要针对不同的功耗进行设计方法的折中。

- 可制造性设计及成品率

- 过去的成品率,完全取决于代工厂的制造工艺水平;

- 现在的成品率,将更多的依赖于设计本身的特征。

- 随着电路中门数的继续增长,以及新的制造技术的发展(包括铜制造工艺),出现了许多意想不到的因素,如平整性对时序的影响、过孔空洞效应等,所有这些因素都会引入新的缺陷类型,影响成品率。

- 布线后的工艺应用的复杂性增加了,光学和工艺校正(OPC,Optical and Process Correction)成为0.13um工艺的必需环节,而进行OPC可能会大大影响成品率。

- 其他旨在提高成品率的布线后的工艺应用,如金属填充、开孔和冗余孔洞插入等,实际也可能增加缺陷。

- 集成电路可制造性设计(DFM):

- 在一个芯片付诸制造之前,尤其是在芯片批量生产之前,如果能够准确预测出该产品的制造成品率,将对IC制造起到非常重要的作用。在芯片生产之前采取一些修正措施,如改变设计规则、选择先进的工艺线、改变芯片的布局布线和加入容错设计等,可使继承电路的成品率达到最大,大大缩短产品的研制周期。

- 它将电路性能与生产能力紧密结合,使集成电路的成品率和利润达到最优化。

- 设计成本(Design Cost)

- SoC设计方法的发展与挑战

- SoC的发展:

- 随着集成电路制造工艺的发展,SoC上将集成更多数量和种类的器件。

- 设计、制造、封装和测试变得越来越密不可分。

- 人们对高性能的SoCial的需求会更加迫切。

- 未来的SoC中将会用到更多处理器或加速器,一边更加灵活地支持不断出现的新应用。

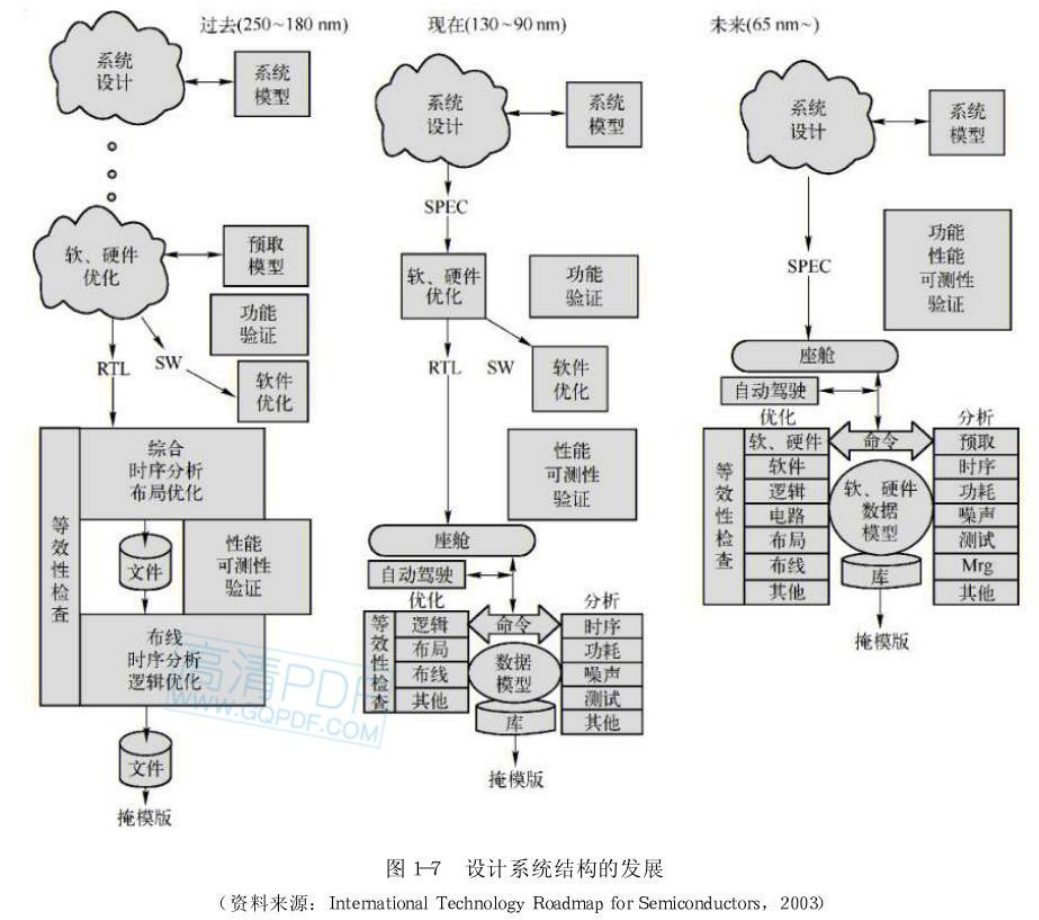

- SoC设计方法的发展趋势:

- IP复用将不仅仅在硬件领域,在软件设计领域同样需要;

- 今后的设计将在一个应用平台上完成,该平台将包括一个或多个处理器和逻辑单元,即基于平台的设计;

- 可编程、可配置、可扩展的处理器核的使用,会使得原有的设计流程和设计者思维发生变化;

- 系统级验证时,利用高级语言搭建验证平台和编写验证向量,需要相应的工具支持;

- 软硬件协同综合,使得在同样的约束条件下,系统达到最优的设计性能。

- (以上这些都要求设计层次想着更高的抽象层次发展,设计工具之间更紧密的结合,更早地实现功能验证和性能验证)

- SoC的发展:

1.3.3 未来的SoC

- 在未来的SoC设计中,设计者会努力争取将系统所有的重要数字功能,做在一个芯片上。

- SoC将设计将所有的重量级功能,集成到一个芯片上。

- 未来的众核芯片上将集成数百个乃至数千个小核,可更有效地提高SoC性能,改善芯片通信方式,并降低功耗。

- 在未来的SoC设计和销售中,软件的作用所占的比重将越来越大。

- 未来的SoC设计不仅包含了硬件,还要包含很大规模的软件,传统的软硬件划分准则不再有效。

- 同时,芯片销售将包括驱动程序、监控程序和标准的应用接口,还可能包括嵌入式操作系统。

- 软件的增值会给设计公司带来更多的收入,设计思路会发生很大的变化。

- 在未来的SoC设计中,功耗问题将遇到更大的限制和挑战。

- 高性能(Power Efficient)的新型SoC系统架构,将成为SoC发展的主要驱动力。

- ???以前,绝大多数这样的功能都是靠使用专用硬件加速器来实现的。这就使得设计的周期长、成本高,而且产品寿命短。以电子系统级设计为代表的先进的SoC 设计方法的出现,使得以多个处理器或 DSP和可配置的处理器为中心的复杂 SoC 设计变得简单。而灵活的软 件方案可以更有效地解决这个多变、复杂的应用问题。可以预测,以多个处理器和可配置的处理器为中心的复杂SoC必将成为未来的主流。