两个数据表的故事第 2 部分:理解“设计”Dk

在第一部分“两个数据表的故事”中,我解释了 IPC-TM-650-2.5.5.5 测试方法手册 [7] 导致空气滞留如何成为仿真和被测器件 (DUT) 测量之间有效介电常数 (Dkeff) 和相位延迟差异的主要原因。测试夹具的截留空气导致层压板供应商的 Dk/Df 表中公布的 Dk 低于实际印刷电路板 (PCB) 应用中的测量值。这是因为在实际 PCB 中,所有东西都粘合在一起,没有空气滞留,如图 1 的横截面图所示。

图 1.箔粘合到芯或预浸料电介质的示例。Rz 是由轮廓仪测量的箔的 10 点平均粗糙度。Hsmooth 是电介质的厚度,就像去除了箔一样。

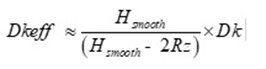

当具有相同 Rz 粗糙度的铜箔粘合到芯或预浸料的每一侧时,Dkeff 由以下简单的校正因子 [1] 从公布的 Dk 启发式确定:

方程 1.

哪里:

Hsmooth 是电介质的厚度,就像去除了箔一样

Dk = 层压板供应商的 Dk/Df 表中公布的介电常数

Rz = 10 点平均值,相当于铝箔供应商数据表中公布的 Rz(JIS) 或 Rz(DIN)。不要将其与 Rq 混淆,Rq 是粗糙度的 RMS 值。

罗杰斯公司 [4] 明白这一点。这就是为什么除了通过 TM650 钳位带状线谐振器测试方法 [7] 测量的体 Dk 之外,他们还提供“设计”Dk。设计 Dk 是使用差分相长法从几个不同的测试批次的材料和最常见的厚度上得出的平均值。该方法基于测量同一面板上两个相同长度的微带传输线几何形状的相位差。因为这是一个真正的微带线应用,所以电介质完全粘合到铜上,没有空气滞留。知道相位和长度差异,就可以凭经验确定有效 Dk。

所得有效 Dk 的准确性取决于几个因素,例如:

-

-

夹具设计

-

-

-

两条传输线之间的长度比

-

-

-

被测样品的材料厚度

-

-

-

铜的厚度

-

-

-

微带电路上箔的实际粗糙度。

-

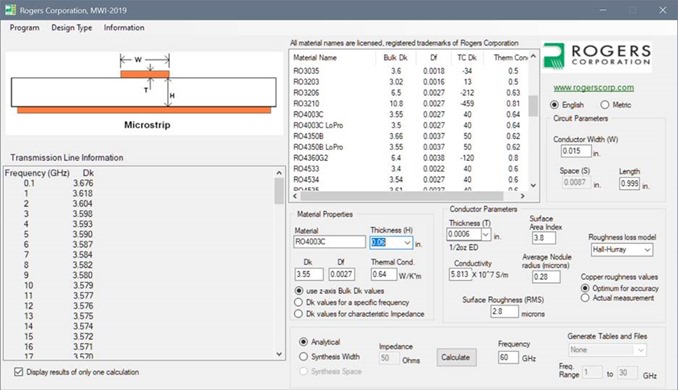

罗杰斯提供了一个方便的阻抗计算器,而不是实际的 Dk/Df 表,如图 2 的RO4003C示例所示。有三个 Dk 选项可供使用:

-

-

Z 轴体 Dk

-

-

-

特定频率的 Dk 值

-

-

-

特性阻抗的 Dk 值

-

第一个单选按钮,如图 2 所示,z 轴体 Dk 值为 3.55,由 TM650 2.5.5.5 测试方法手册测量。但是,当选择不同的频率时,该值不会改变。这使得这个数字值得怀疑,因为显然设计 Dk 确实会随频率而变化。因此,此数字可被视为等同于营销数据表,不应使用。

当选择中间的单选按钮时,将显示特定频率的 Dk 值,该值对应于在图 2 右下频框中输入的频率。这是最有用的选项,因为它允许用户在他们为其应用选择的任何频率(包括特性阻抗)下选择正确的设计 Dk。此选项已经考虑了箔片粗糙度效果,因此无需在模拟器中使用校正因子。

最后一个单选按钮选择用于特性阻抗计算的 Dk。它是一个具有不同 Dk 的 “设计” Dk。与 Bulk Dk 选项类似,它不会随频率而变化。对于除 Rogers 计算器以外的任何仿真工具,都不应使用体 Dk 和 Dk 值作为特性阻抗值。

图 2.罗杰斯公司阻抗计算器示例。对于 8 mil 厚的 RO4003C 电介质,体积 Dk 为 3.55,而设计 Dk 随频率的变化显示在左下角窗口。

在信息选项卡下,用户可以下载指定厚度随频率变化的设计 Dk,如图 2 左下角窗口所示。可以选择此数据并将其复制到剪贴板,并粘贴到电子表格中以供进一步处理。

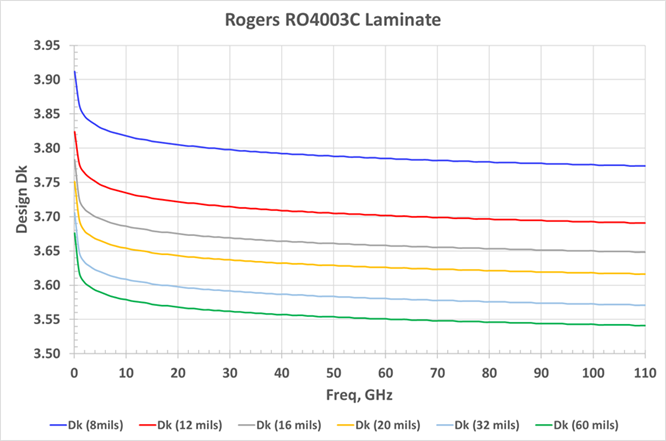

图 3 绘制了 RO4003C 材料在 8 mil 到 60 mils 的各种厚度下的设计 Dk 与频率的关系。可以看出,设计 Dk 在频率上不是恒定的,而且对于不同的厚度来说,它是不同的,主要是由于测量中已经包含的箔的粗糙度。

对于相同的箔粗糙度,较薄的材料比较厚的材料具有更高的设计 Dk。这是因为当箔齿突出到薄的介电材料中时,电场的浓度更高,导致顶部和底部铜层之间的电容更高。对于厚电介质,箔齿对电容的影响较小,因此对 Dkeff 的影响较小,如公式 1 在数学上描述的那样。

由于箔的粗糙度不会显着影响厚层压板的设计 Dk,因此我们可以假设整体 Dk 大致相当于 60 mil 层压板随频率变化的设计 Dk。

图 3.设计 Dk 与频率的关系,适用于从 8 mils 到 60 mils 的各种厚度RO4003C,主要是由于箔的粗糙度。对于相同的箔粗糙度,较薄的材料比较厚的材料具有更高的设计 Dk。

从启发式的角度来看,我们可以重新排列公式 1,并根据公式 2 估计RO4003C层压板上使用的箔的 Rz 粗糙度为 6.302 μm。

方程 2.

哪里:

Hsmooth 是 8 mil (203 μm) 层压板的厚度

对于 60 mil (1524 μm) 层压板,DkBulk = 3.55

Dkeff = 60 GHz 时 8 mil (203 μm) 层压板的设计 Dk

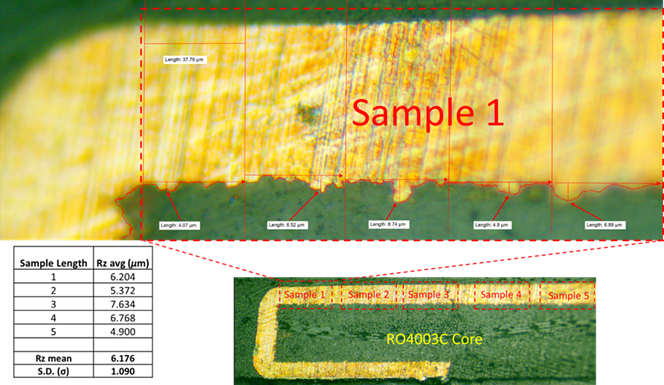

测量了来自 Picotest [6] 提供的时域反射计 (TDR) 演示板的横截面样品,如图 4 所示。TDR 演示板采用 8 mil 厚的 Rogers RO4003C 芯层压板制成,并覆有 2 盎司铜箔。

分析了五个突出显示的铜粗糙度随机样品长度,标记为图 4 的样品 1 到样品 5。然后将每个样品的总长度分成五个相等的部分,类似于样品 1 的放大图,以测量每个部分的最大峰谷高度。然后对每个样品长度的五次测量进行平均,以确定 Rz 粗糙度,如 IPC TM650 2.2.17A [8] 中所述,如图 4 所示。

五个样品的 Rz 平均值为 6.176 μm,标准差 (SD) 为 1.090 μm。这与根据公式 2 确定的 6.302 μm 的估计粗糙度形成鲜明对比。

图 4.来自基于 Rogers RO4003C 的 TDR 演示板的横截面样品,由 Picotest [6] 提供,用于确定箔的 Rz 粗糙度。

当我们使用图 4 和公式 1 中测得的实际粗糙度时,我们可以计算不同厚度在 60 GHz 时的 Dkeff,如表 1 所示。可以看出,与计算器报告的设计 Dk 相比,delta 小于 1%!

表 1.在 60 GHz 时将简单校正因子应用于 Bulk Dk 时 Roger 的设计 Dk 与 Dkeff 的比较。

| 高度 | 高度 | 大容量 Dk | 设计 Dk | Rz | Dkeff | 三角洲 |

| 8.0 | 203 | 3.550 | 3.785 | 6.176 | 3.780 | -0.13% |

| 12.0 | 304 | 3.550 | 3.702 | 6.176 | 3.700 | -0.04% |

| 16.0 | 406 | 3.550 | 3.657 | 6.176 | 3.661 | 0.12% |

| 20.0 | 508 | 3.550 | 3.625 | 6.176 | 3.638 | 0.37% |

| 32.0 | 812 | 3.550 | 3.580 | 6.176 | 3.605 | 0.69% |

| 60.0 | 1524 | 3.550 | 3.550 | 6.176 | 3.579 | 0.82% |

罗杰斯公司提供了一个方便的计算器来代替 Dk/Df 表,其中可以直接使用随频率变化的“设计”Dk 值,而无需校正粗糙度。当分析实际横截面时,与计算器中的设计 Dk 相比,使用启发式方法校正的 Dkeff 具有出色的相关性。因此,在使用罗杰斯层压板时,应将“设计”Dk 用于阻抗建模和 PCB 叠层设计。