Verilog 硬件描述语言自学——重温数电之典型组合逻辑电路

目录

1)编码器

a. 编码器的定义与分类

b. 编码器的工作原理

2)译码器/数据分配器

a. 译码器的定义与分类

b. 典型译码器电路及应用

3)数据选择器

a. 数据选择器的定义与功能

b. 数据选择器的扩展应用

4)数值比较器

a. 1位数值比较器(设计)

b. 2位数值比较器

c. 集成数值比较器

d. 集成数值比较器的位数扩展

5)算术运算电路

a. 半加器和全加器

b. 加法器的应用

c. 减法运算

1)编码器

a. 编码器的定义与分类

编码:赋予二进制代码特定含义的过程称为编码。

如:8421BCD码中,用1000表示数字8;

如:ASCII码中,用1000001表示字母A等;

编码器:具有编码功能的逻辑电路。

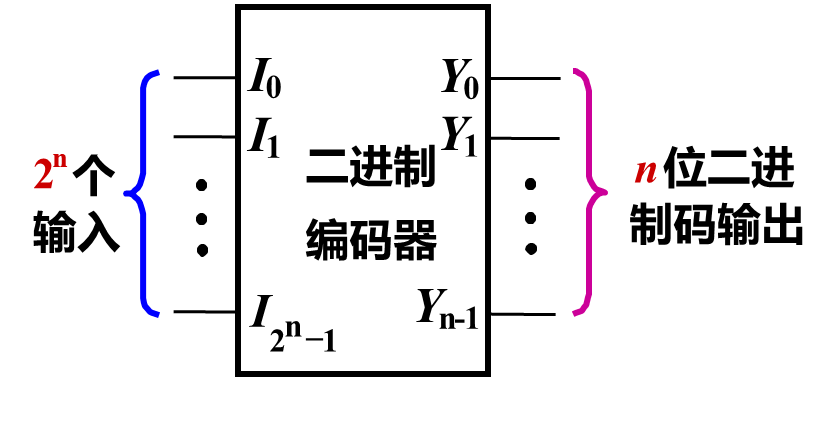

编码器的逻辑功能:能将每一个编码输入信号变换为不同的二进制的代码输出。

如BCD编码器:将十个编码输入信号分别编成10个4位码输出。

如8线-3线编码器:将8个输入的信号分别编成8个3位2进制数码输出。

编码器的分类:普通编码器和优先编码器。

普通编码器:任何时候只允许输入一个有效编码信号,否则输出就会发生混乱。

优先编码器:允许同时输出两个以上的有效编码信号。当同时输入几个有效编码信号时,优先编码器能按预先设定的优先级别,只对其中优先权最高的一个进行编码

b. 编码器的工作原理

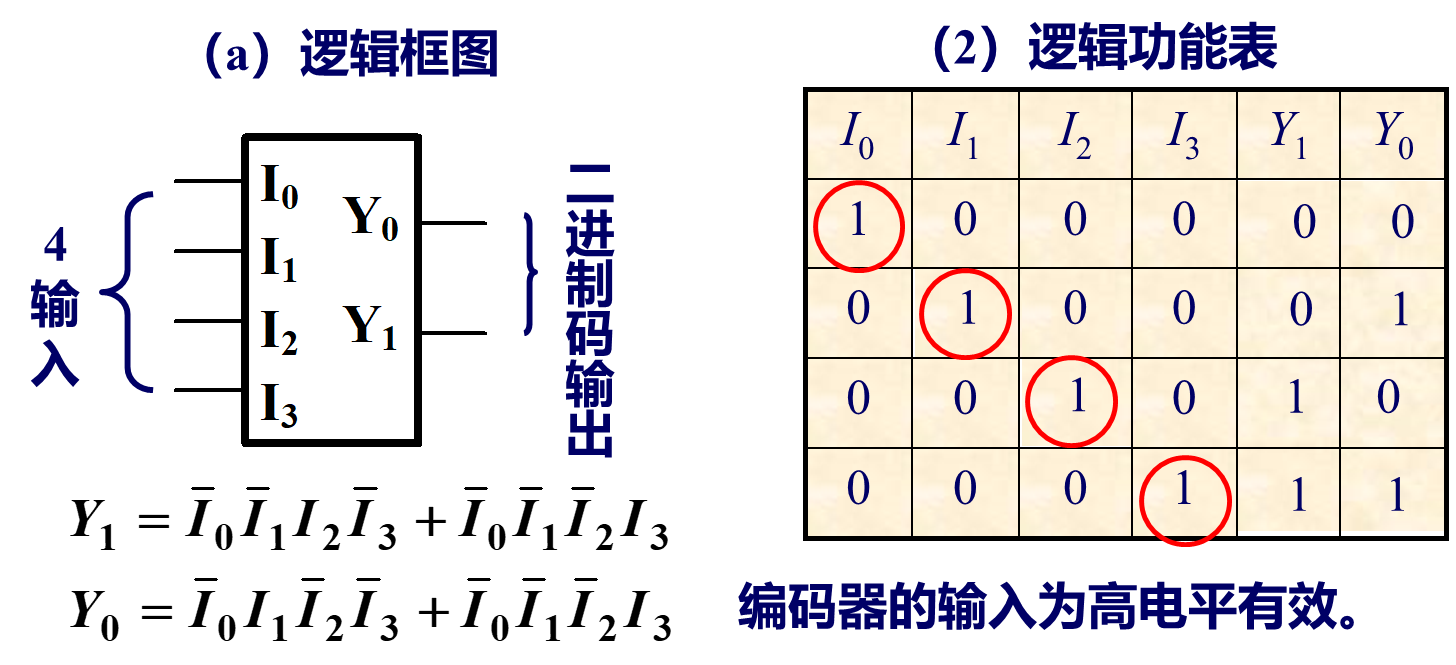

普通二进制编码器:

二进制编码器的结构框图

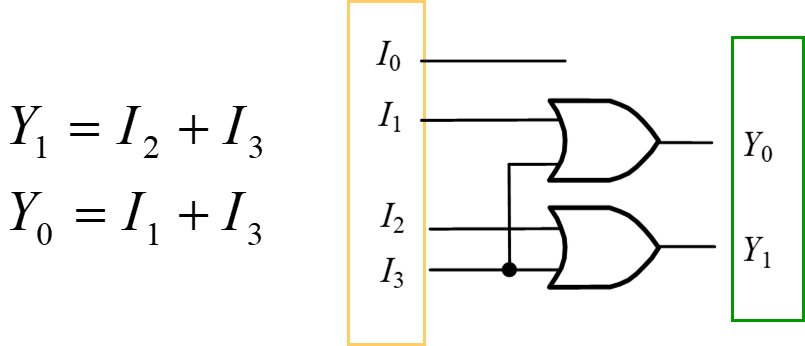

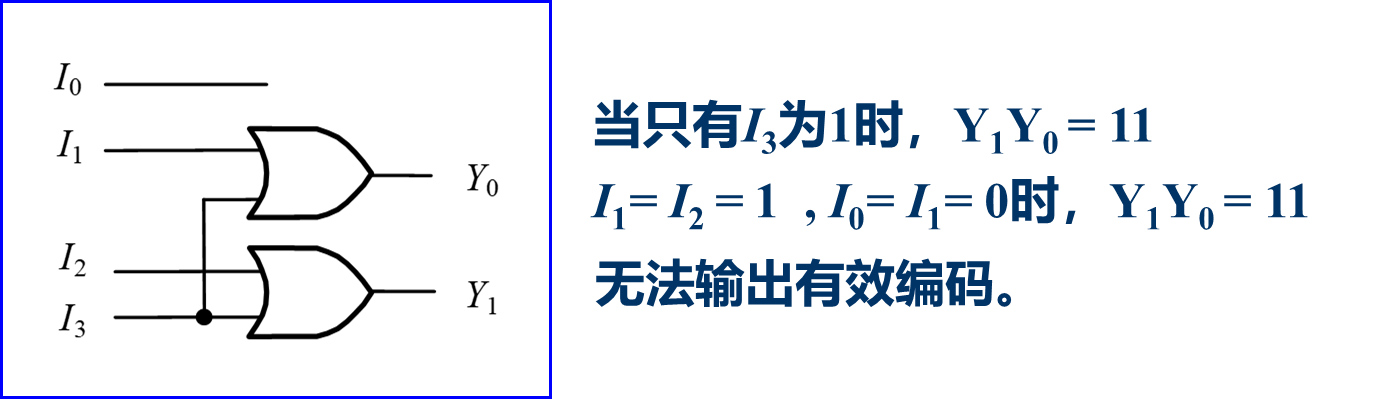

4线—2线普通二进制编码器(设计)

该表达式是否可以再简化?

上述是将输入的其他12种组合对应的输出看做0,如果看做无关项,则表达式为:

如果有2个以上的输入为有效信号?

结论:普通编码器不能同时输入两个以上的有效编码信号 。

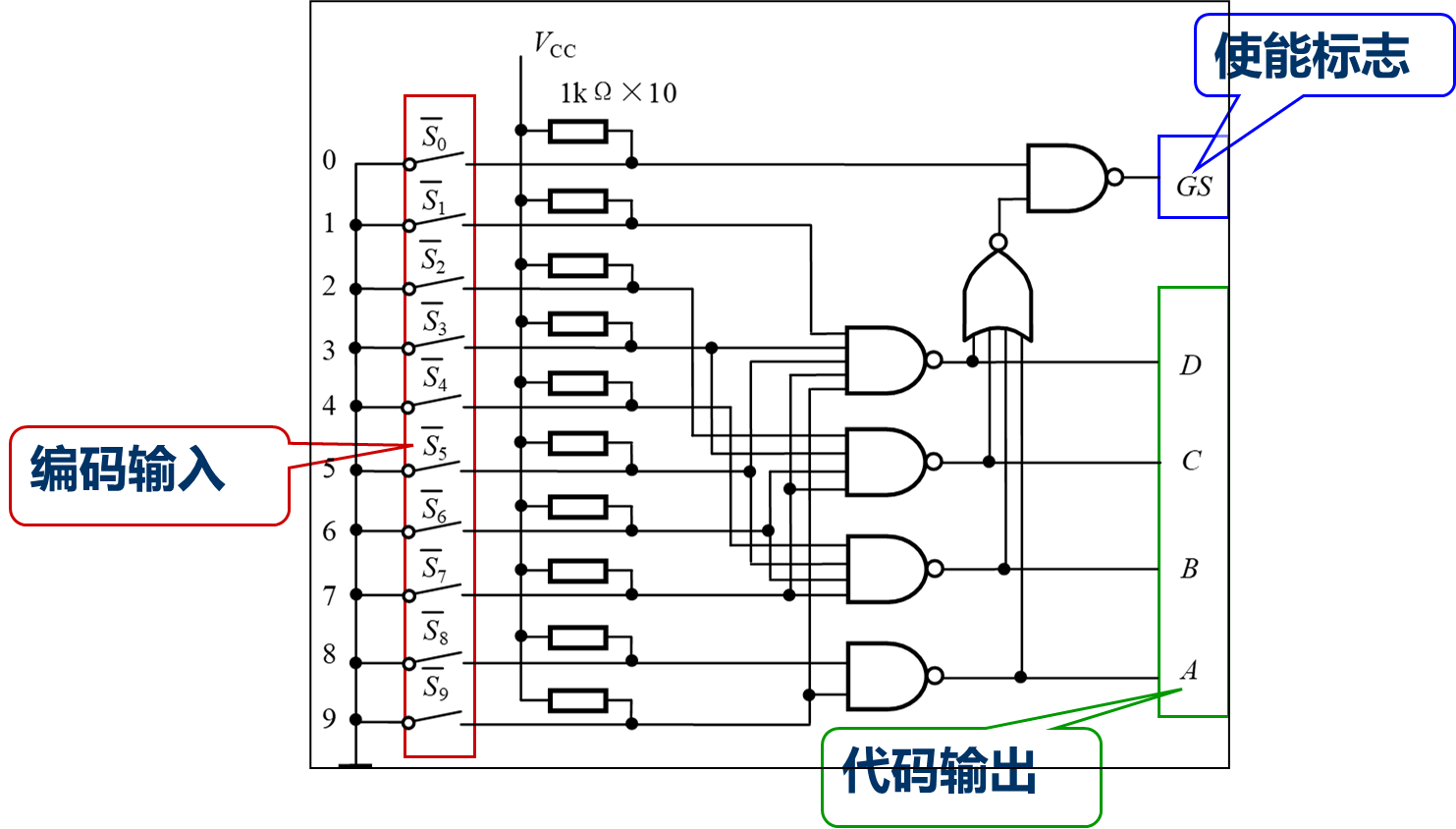

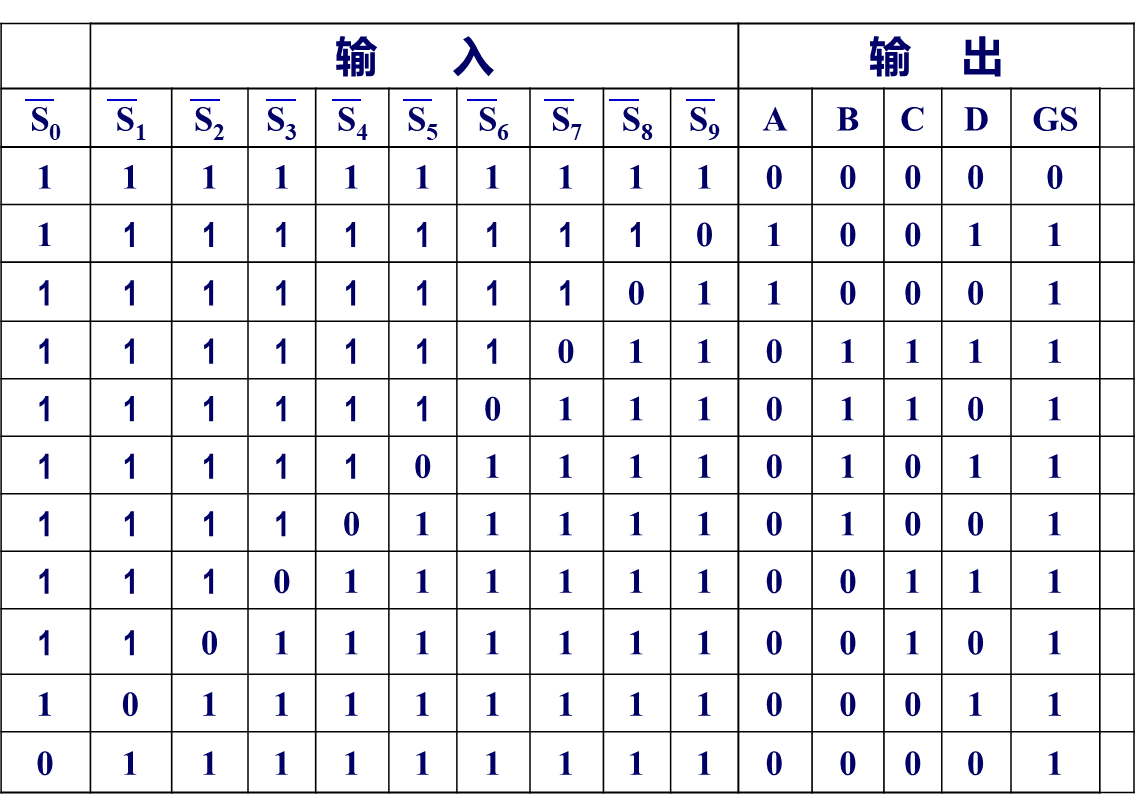

键盘输入8421BCD码编码器(分析)

键盘输入8421BCD码编码器功能表

该编码器为输入低电平有效,输出高电平有效,GS为标志位。

优先编码器

优先编码器的提出:实际应用中,经常有两个或更多输入编码信号同时有效。 必须根据轻重缓急,规定好这些外设允许操作的先后次 序,即优先级别。识别多个编码请求信号的优先级别,并进行相应编码的逻辑部件称为优先编码器。

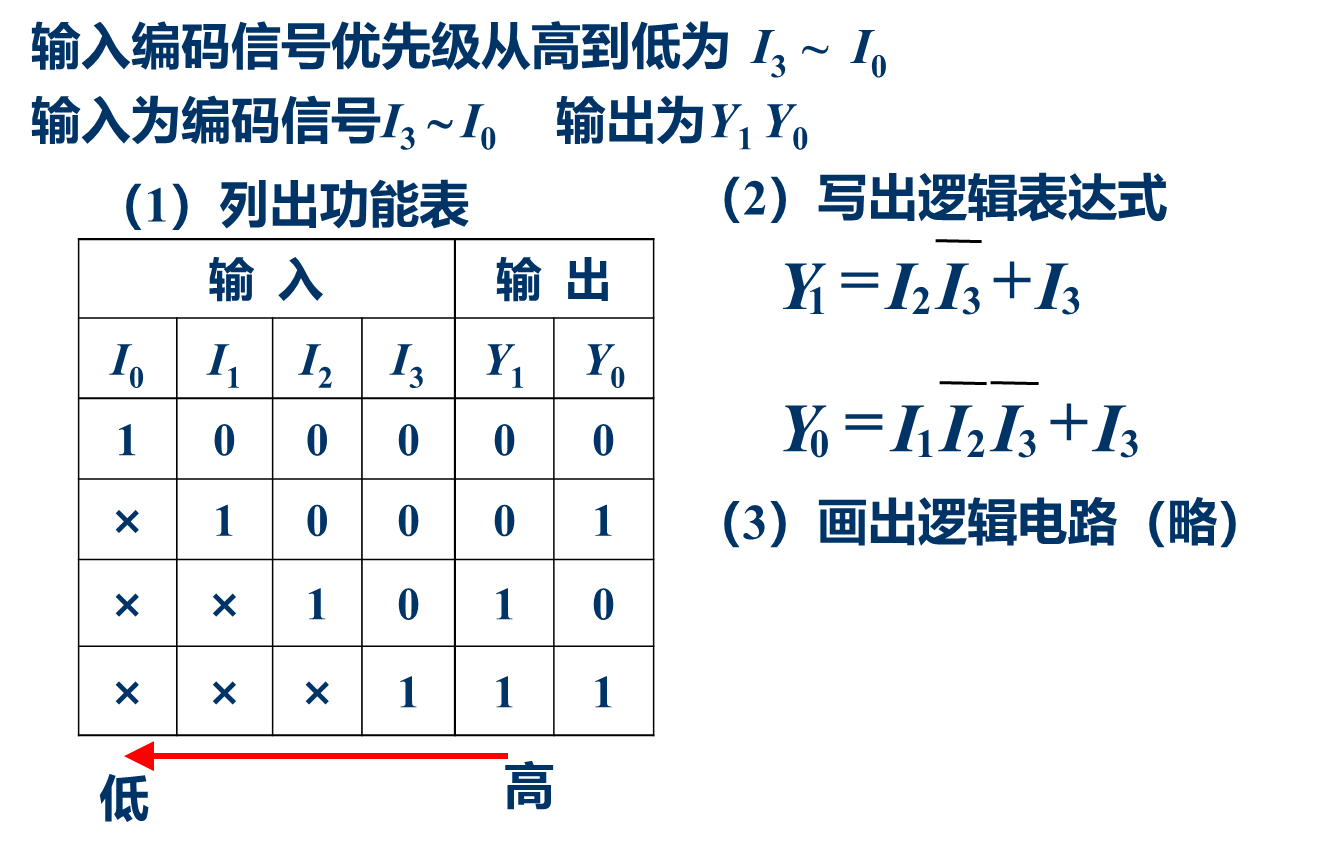

优先编码器线(4─2 线优先编码器)(设计)

输入编码信号高电平有效,输出为二进制代码

典型编码器电路

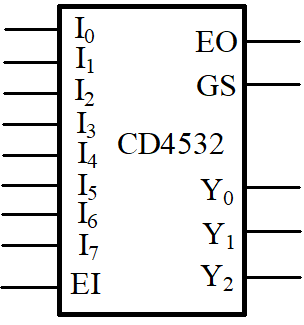

优先编码器CD4532的示意框图

优先编码器CD4532功能表

| 输 入 | 输 出 | ||||||||||||

| EI | I7 | I6 | I5 | I4 | I3 | I2 | I1 | I0 | Y2 | Y1 | Y0 | GS | EO |

| 0 | × | × | × | × | × | × | × | × | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | × | × | × | × | × | × | × | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | × | × | × | × | × | × | 1 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | × | × | × | × | × | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 | × | × | × | × | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 1 | × | × | × | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | × | × | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | × | 0 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0 |

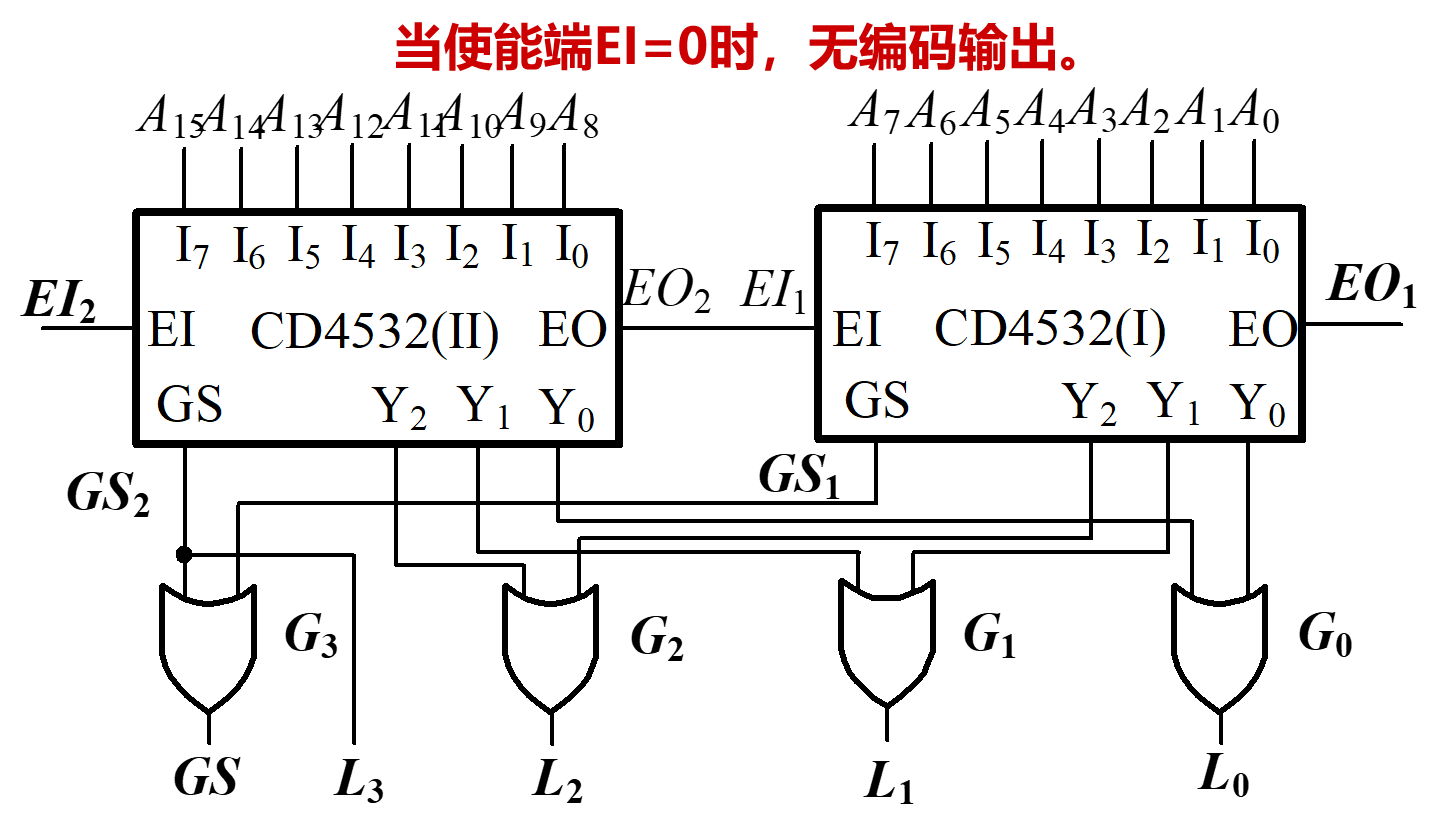

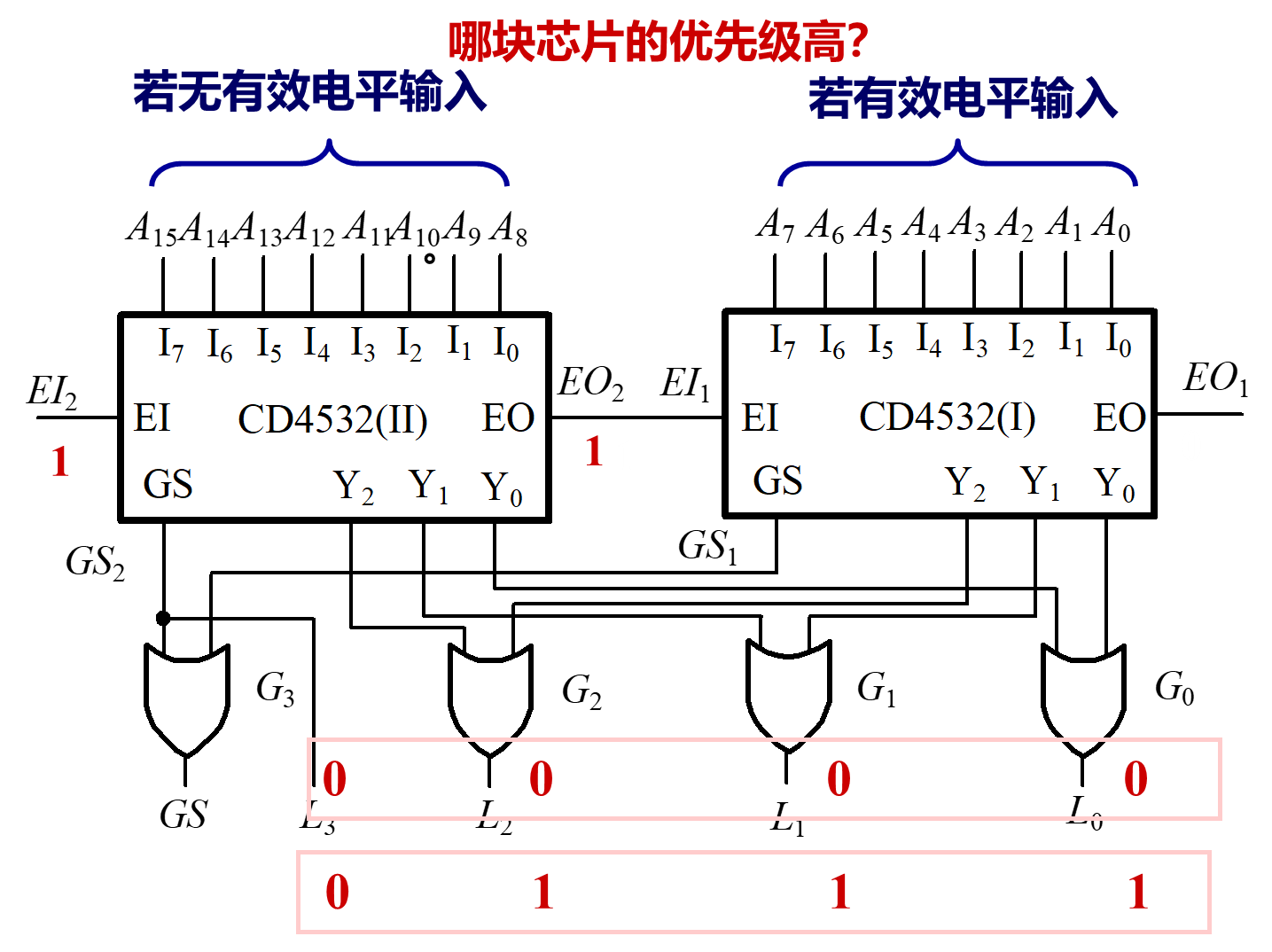

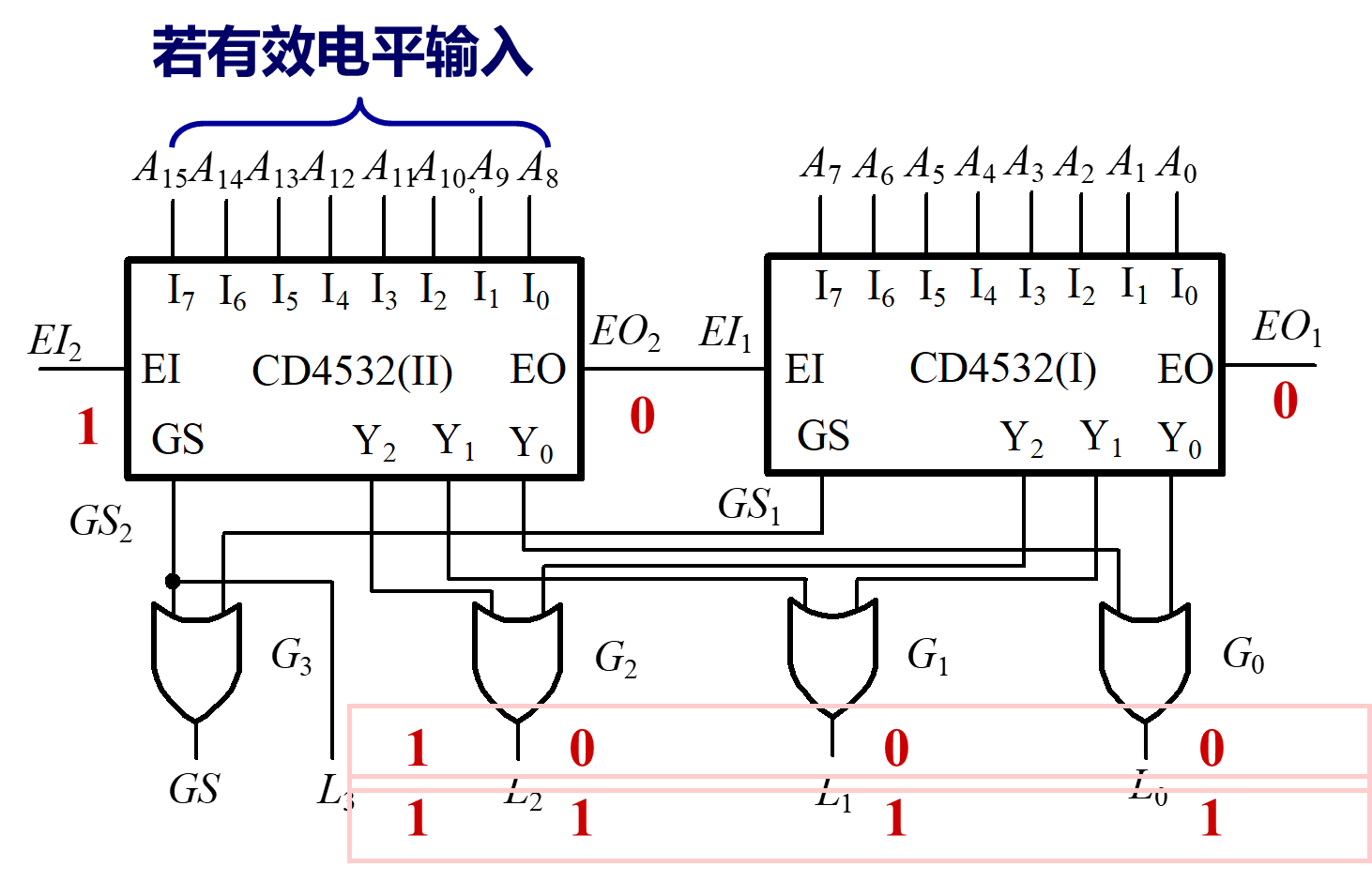

用两片CD4532构成16线-4线优先编码器,其逻辑图如下图所示,试分析其工作原理:

2)译码器/数据分配器

a. 译码器的定义与分类

译码:译码是编码的逆过程,它能将二进制码翻译成代表某一特定含义的信号(即电路的某种状态)

译码器:具有译码功能的逻辑电路称为译码器

译码器的分类:

唯一地址译码器:将一系列代码转换成与之一一对应的有效信号。常见的唯一地址译码器:二进制译码器、二—十进制译码器、显示译码器。

代码变换器:将一种代码转换成另一种代码。

b. 典型译码器电路及应用

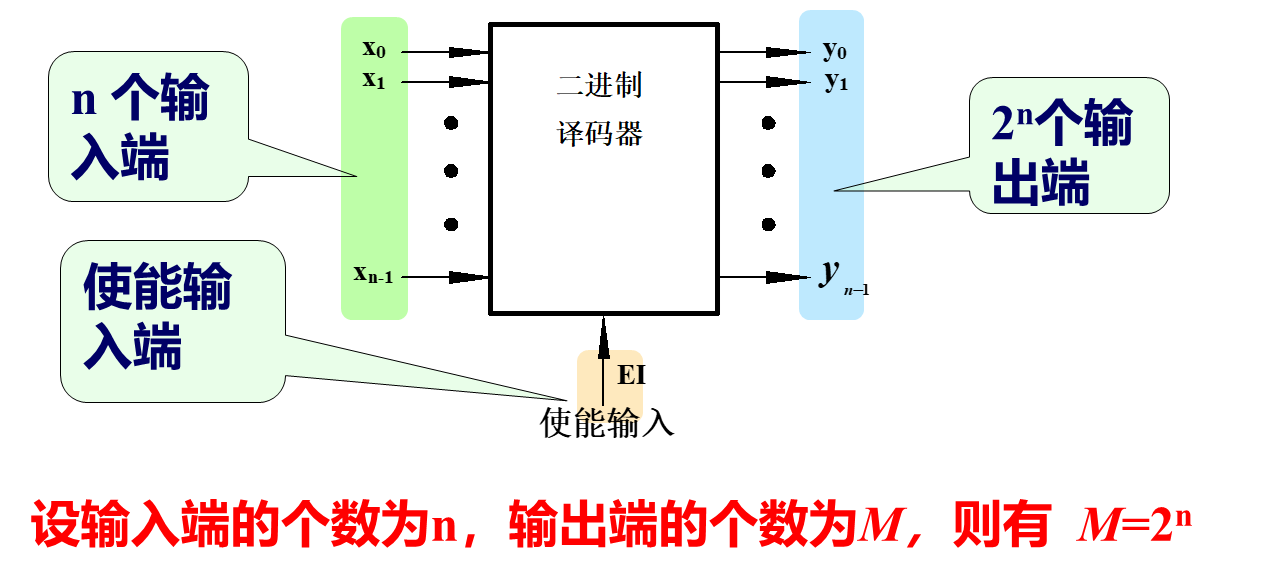

二进制译码器:

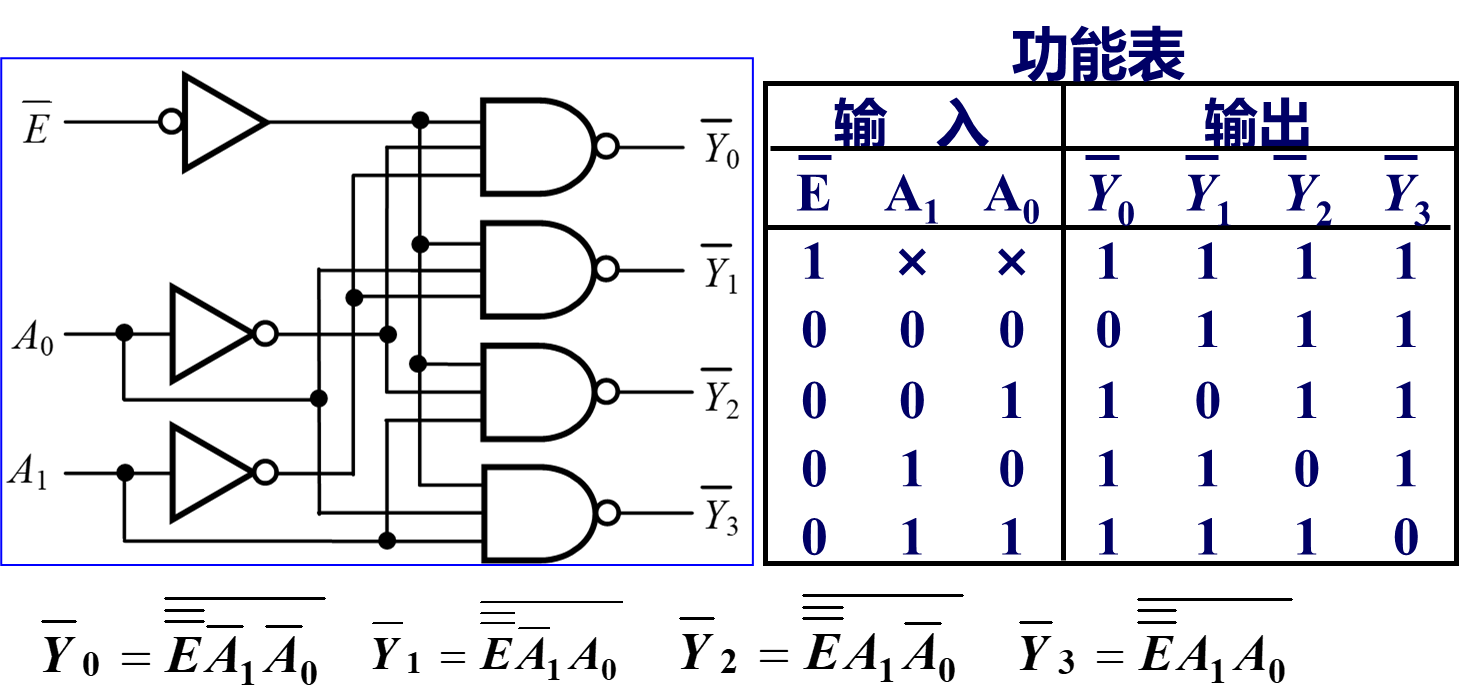

2线 - 4线译码器的逻辑电路(分析)

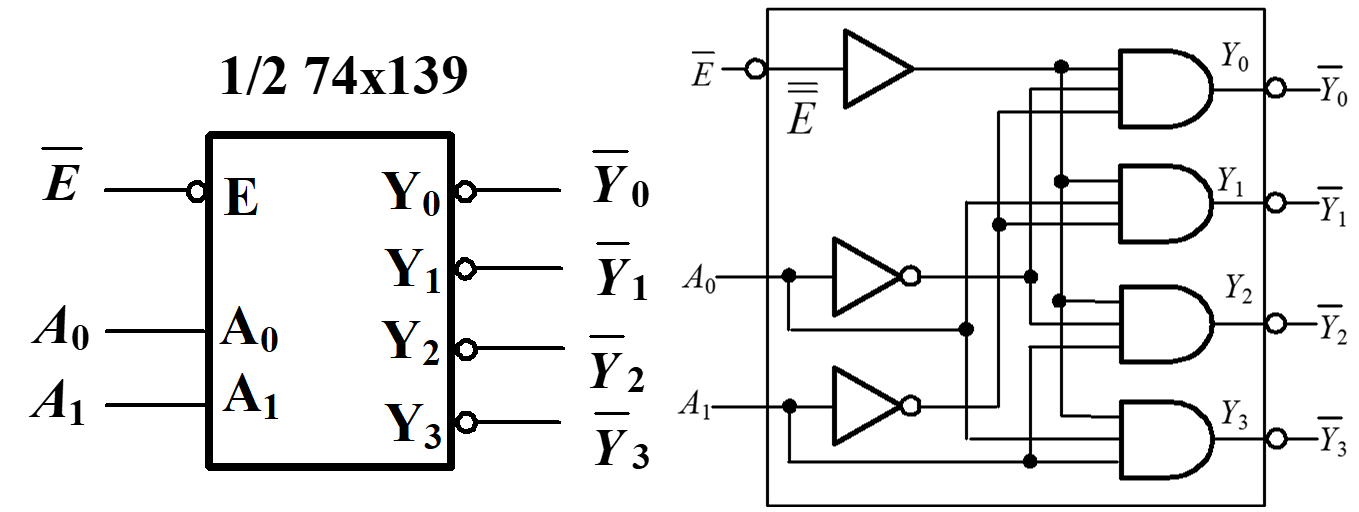

2线-4线译码器(74HC139)

逻辑符号说明:逻辑符号框外部的符号,表示外部输入或输出信号名称,字母上面的“—”号说明该输入或输出是低电平有效。符号框内部的输入、输出变量表示其内部的逻辑关系。在推导表达式的过程中,如果低有效的输入或输出变量(如)上面的“—”号参与运算(如E变为E ),则在画逻辑图或验证真值表时,注意将其还原为低有效符号。

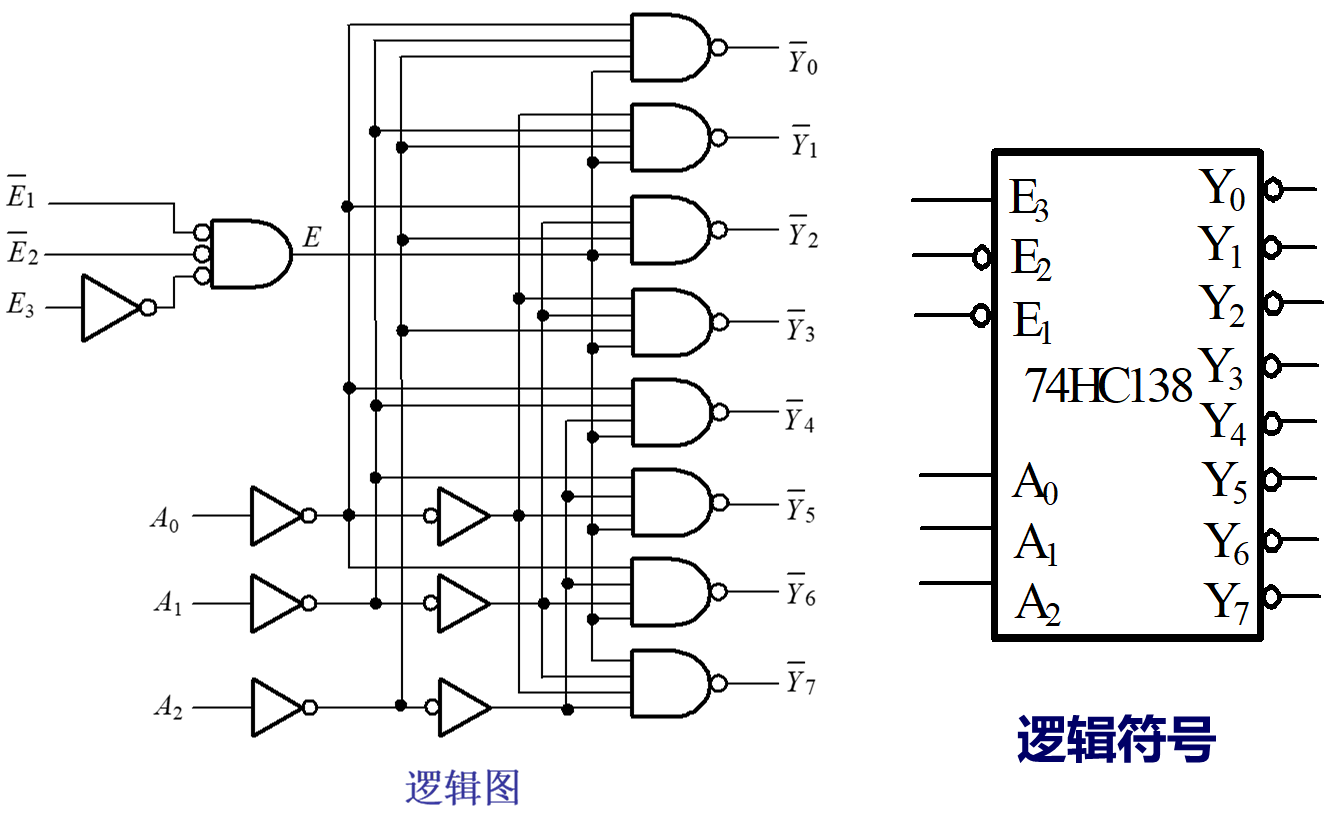

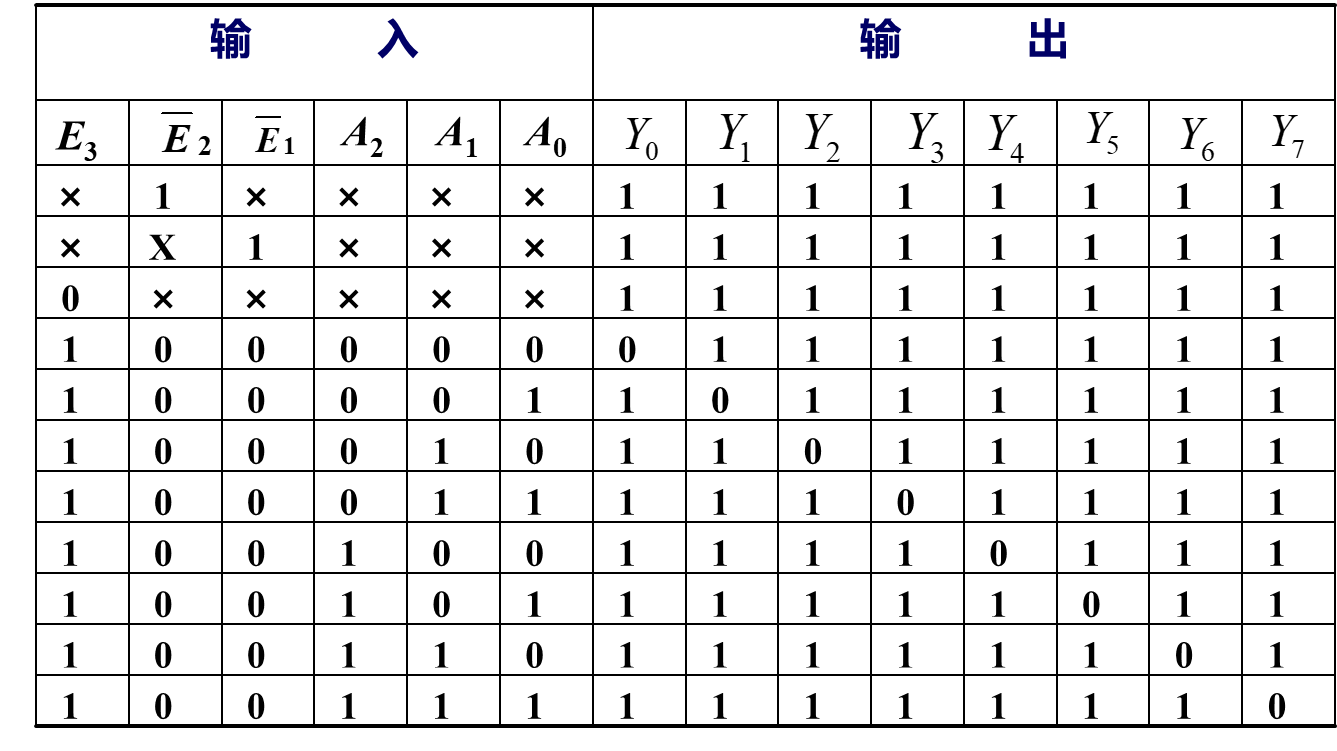

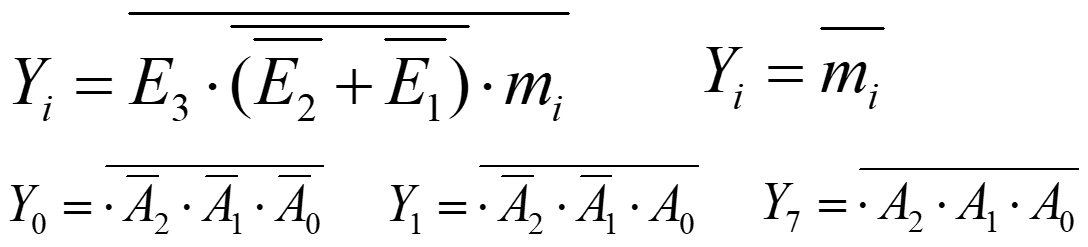

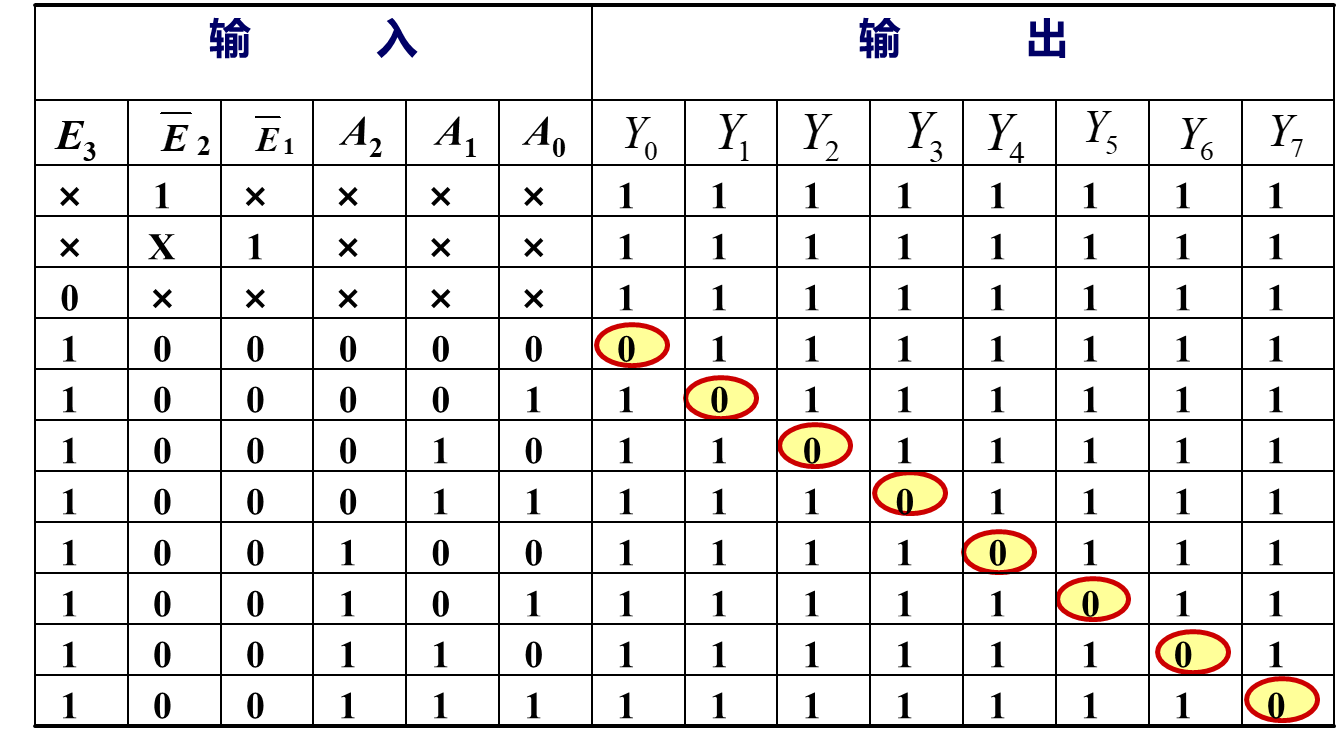

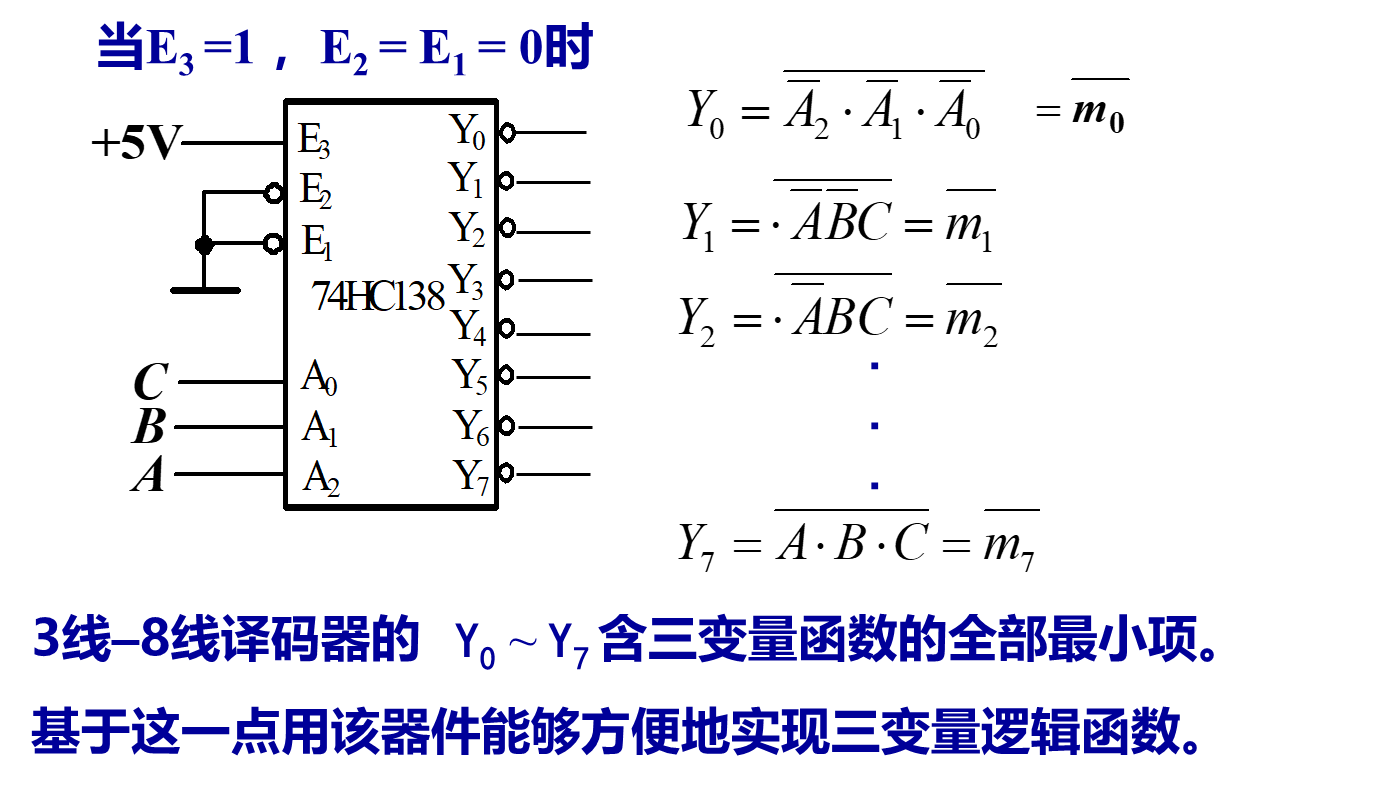

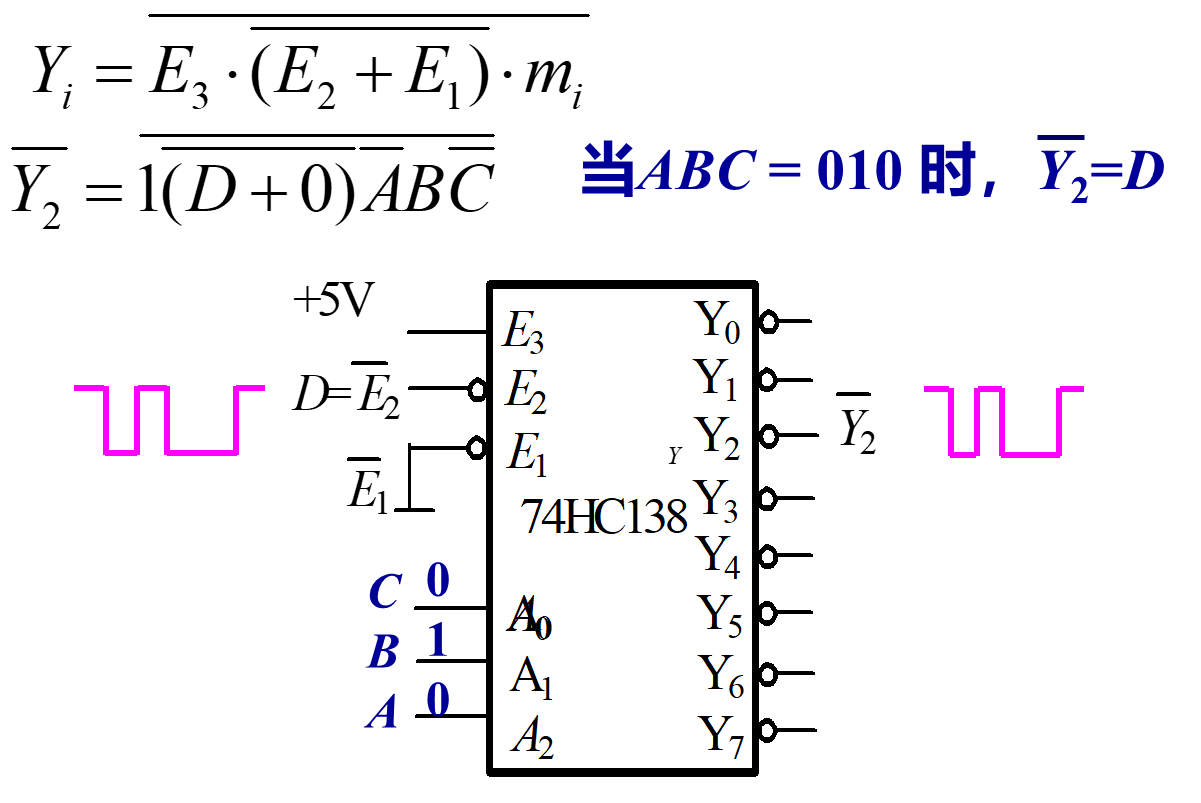

3线-8线译码器(74HC138)

3线-8线译码器(74HC138)功能表

译码器的拓展:

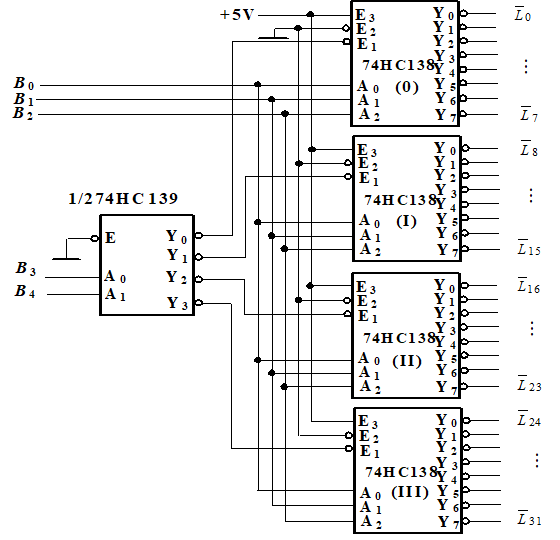

例如:用74X139和74X138构成5线-32线译码器

例如:用译码器实现逻辑函数

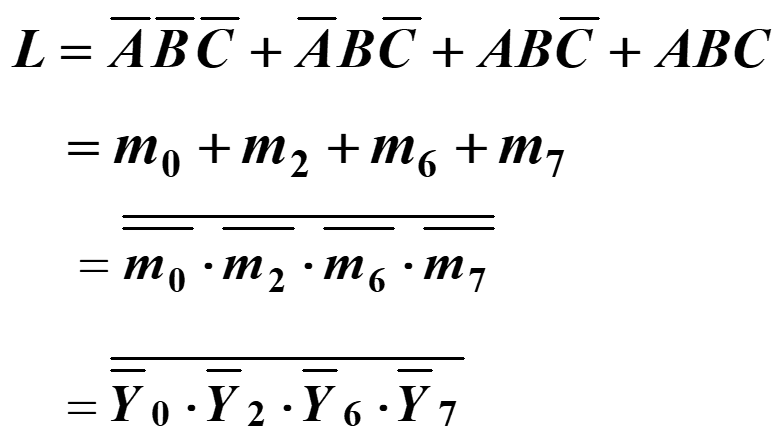

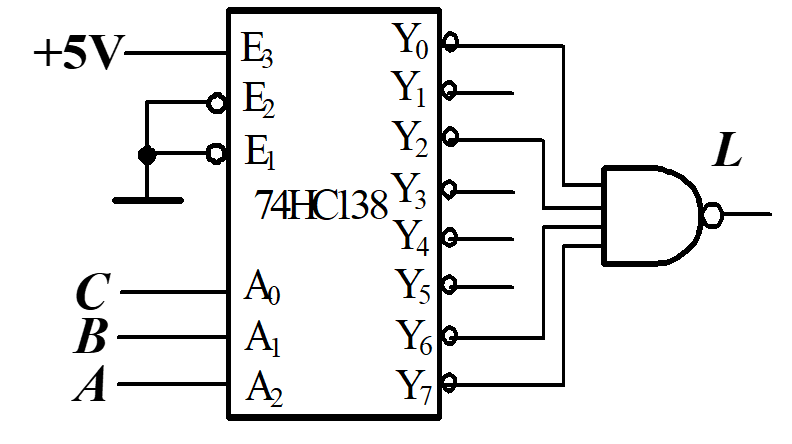

用一片74HC138实现函数![]()

首先将函数式变换为最小项之和的形式:

在译码器的输出端加一个与非门,即可实现给定的组合逻辑函数:

又如:用74HC138组成数据分配器

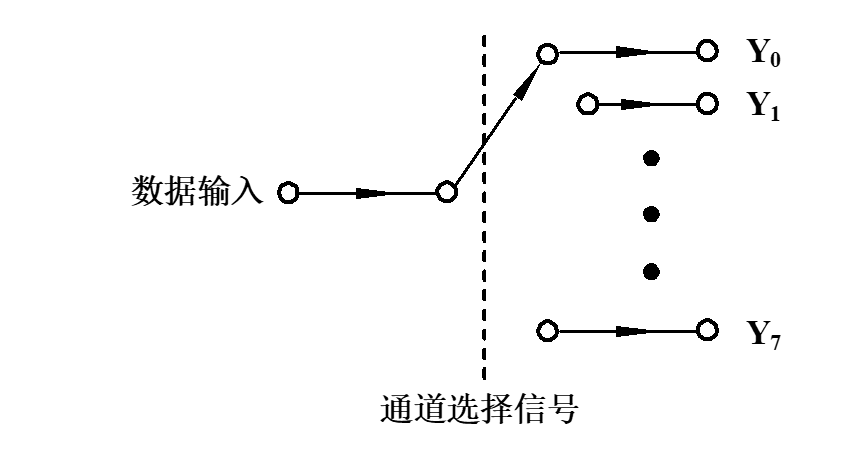

数据分配器:相当于多输出的单刀多掷开关,是将公共数据线上的数据按需要送到不同的通道上去的逻辑电路。

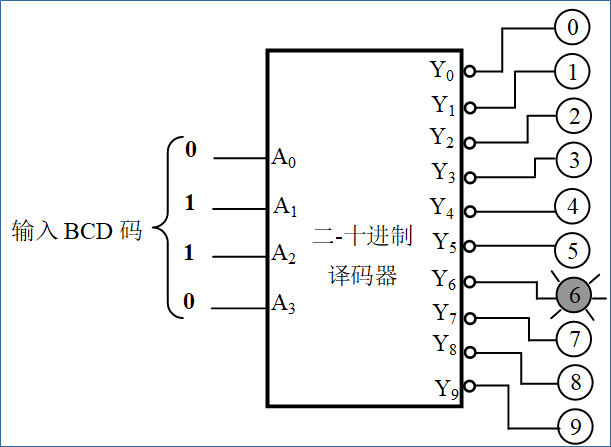

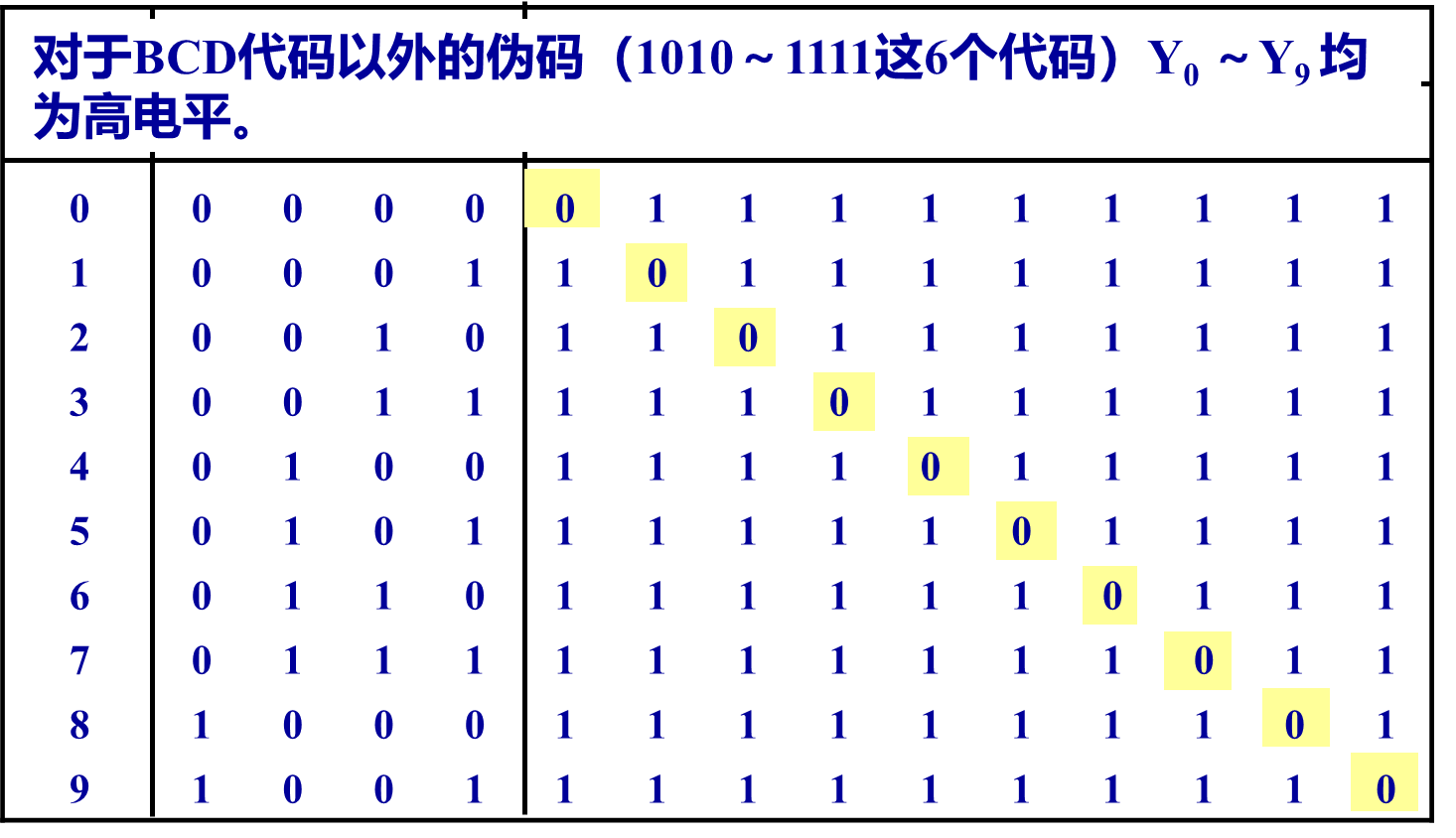

二–十进制译码器

功能:将8421BCD码译成为10个状态输出。

二–十进制译码器的真值表

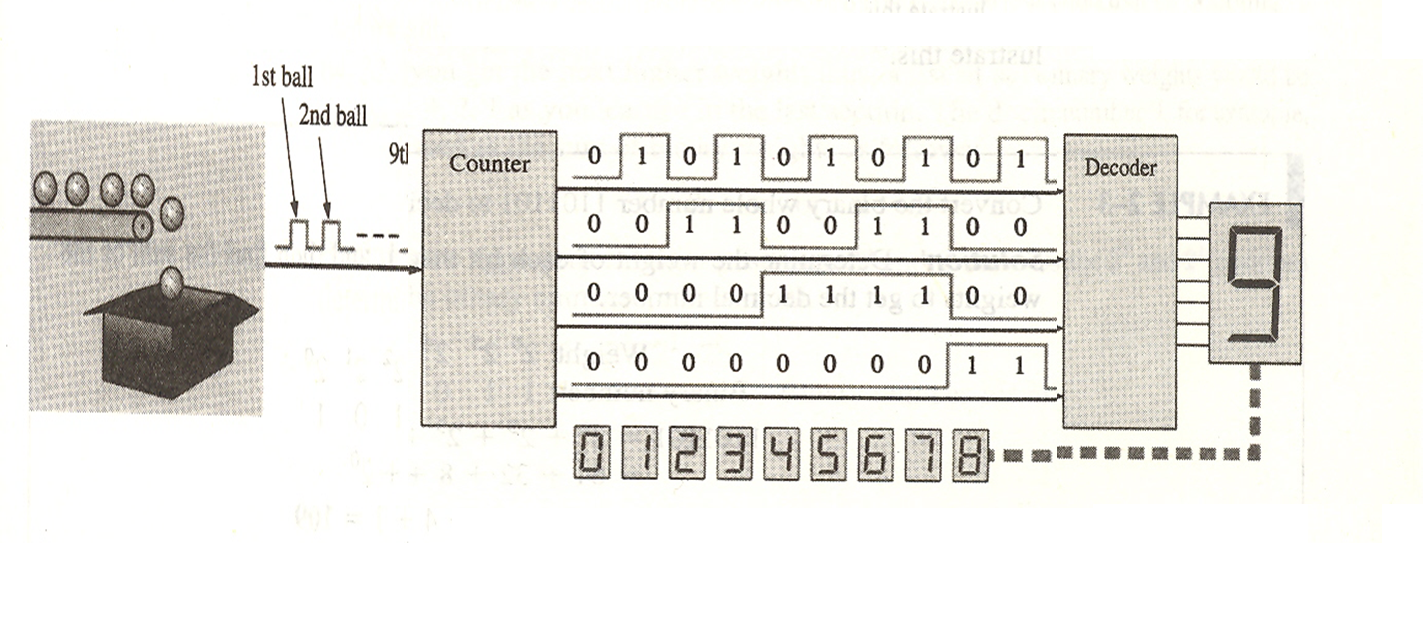

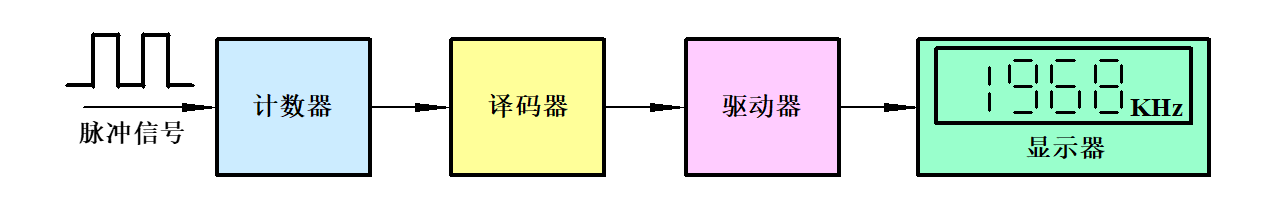

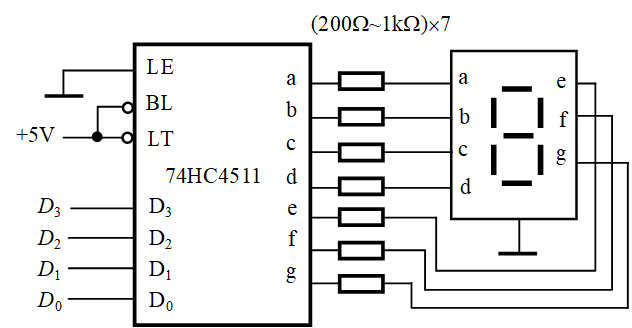

显示译码器:

七段显示译码器:

最常用的显示器:半导体发光二极管和液晶显示器。

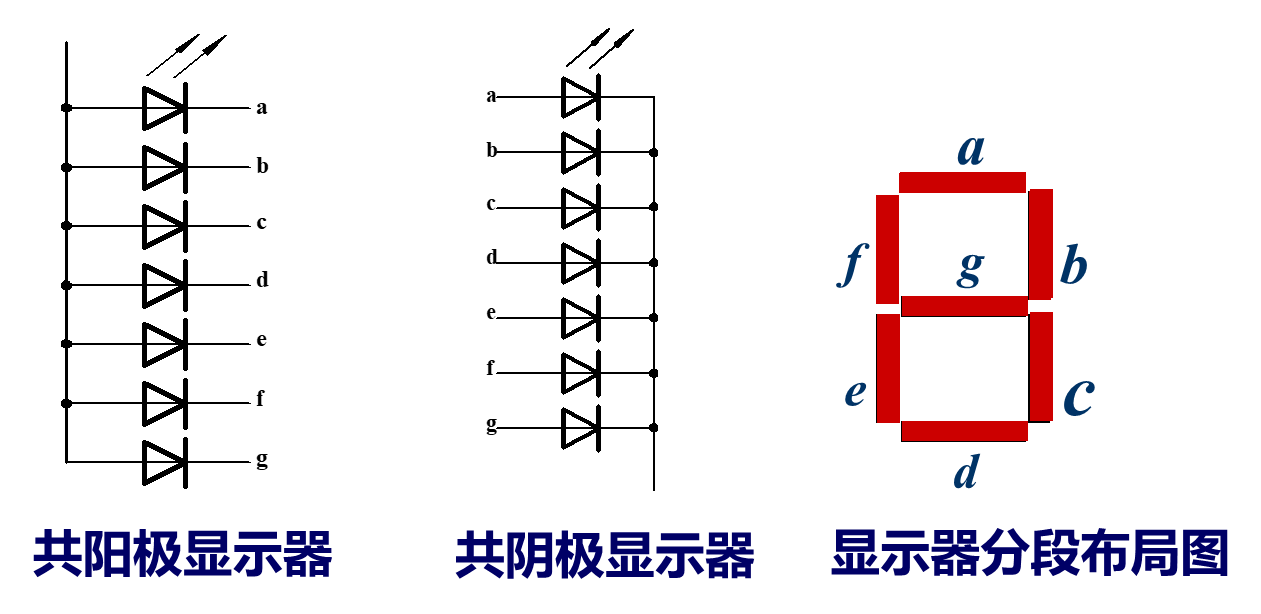

常用的集成七段显示译码器:CMOS七段显示译码器74HC4511

显示译码器与显示器的连接方式:

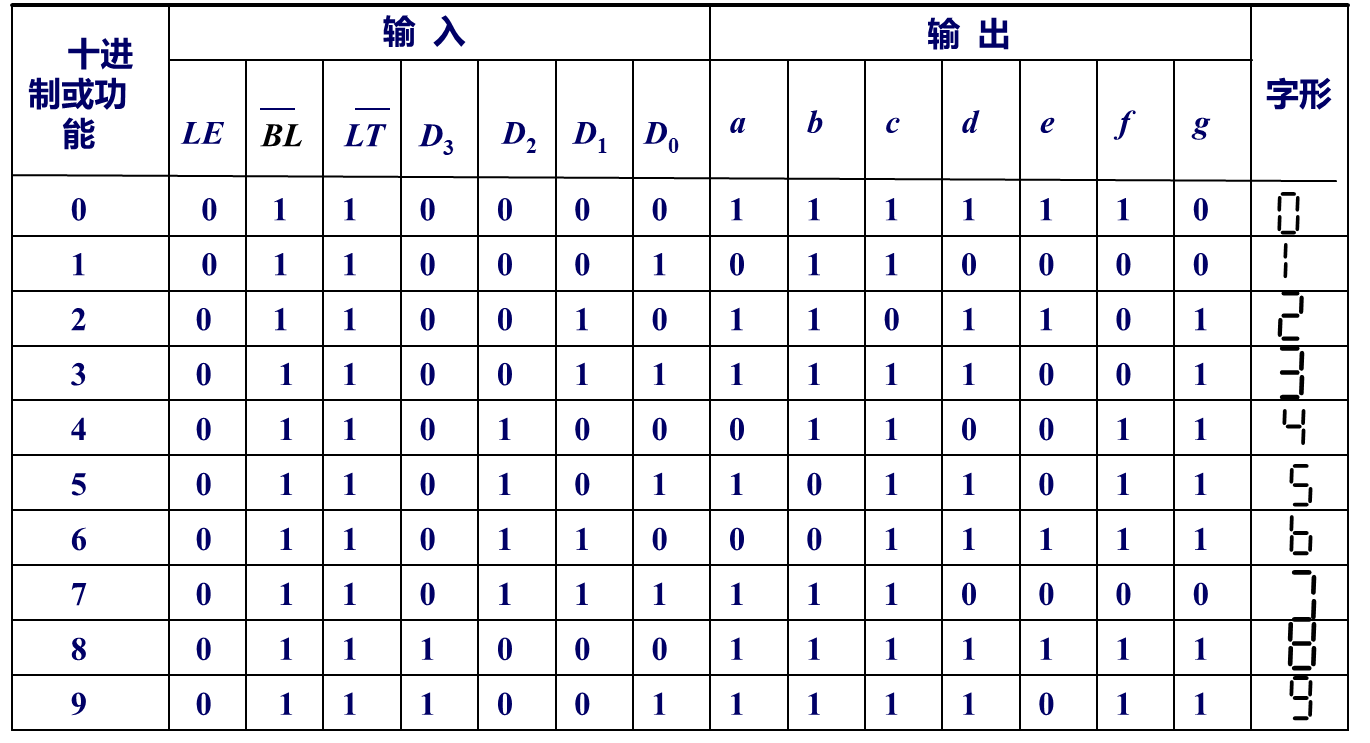

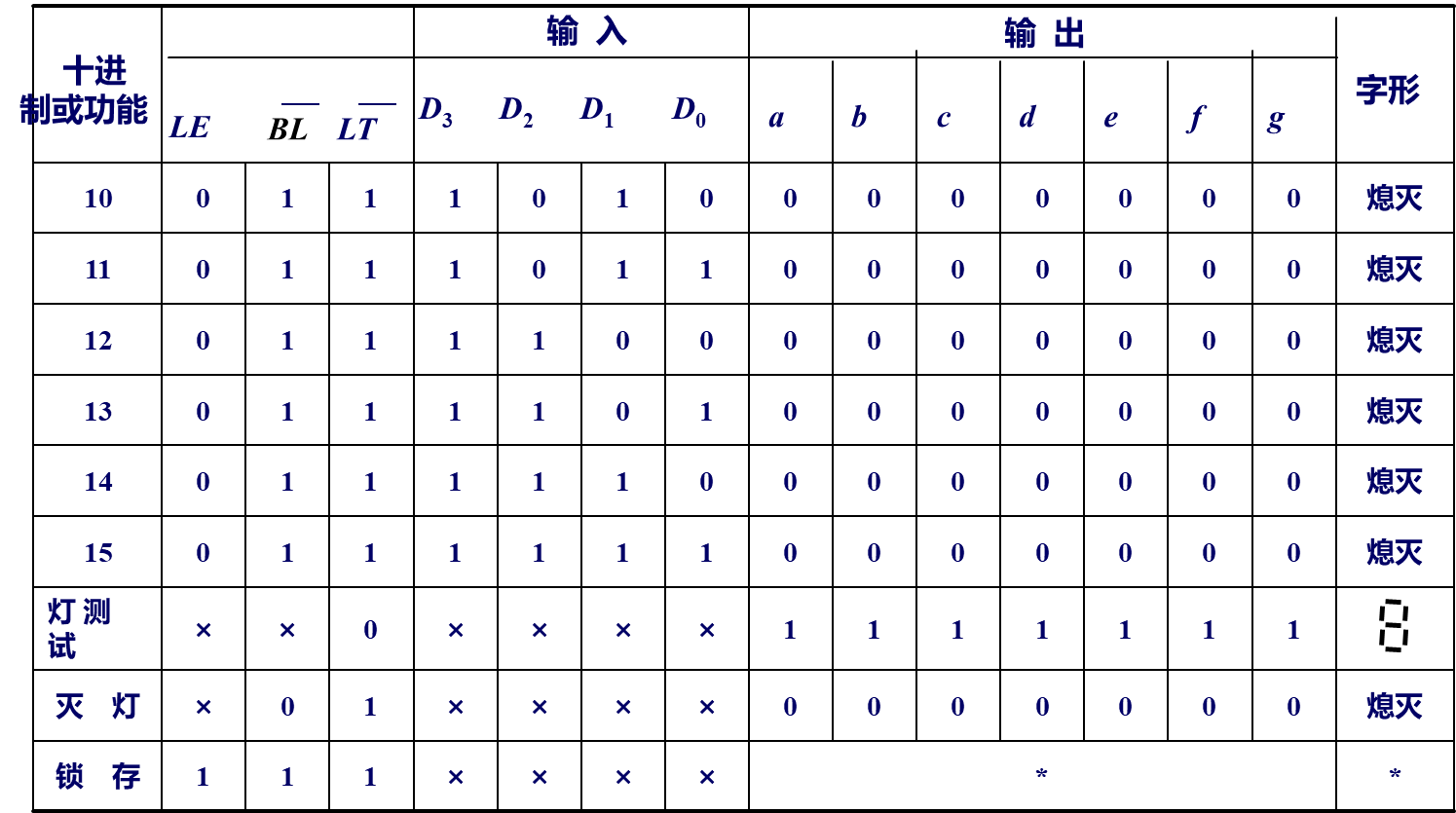

CMOS七段显示译码器74HC4511功能表

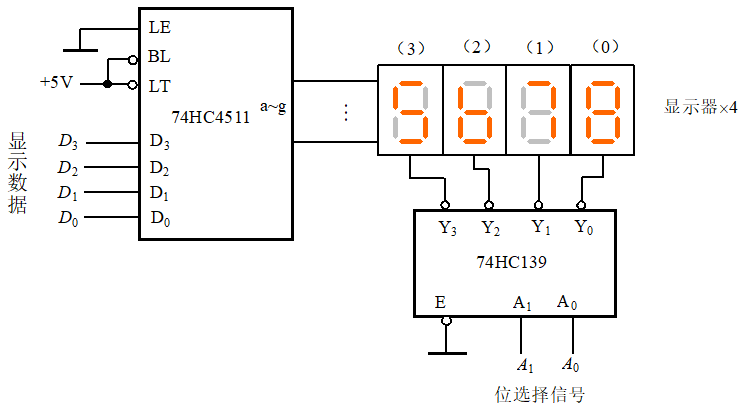

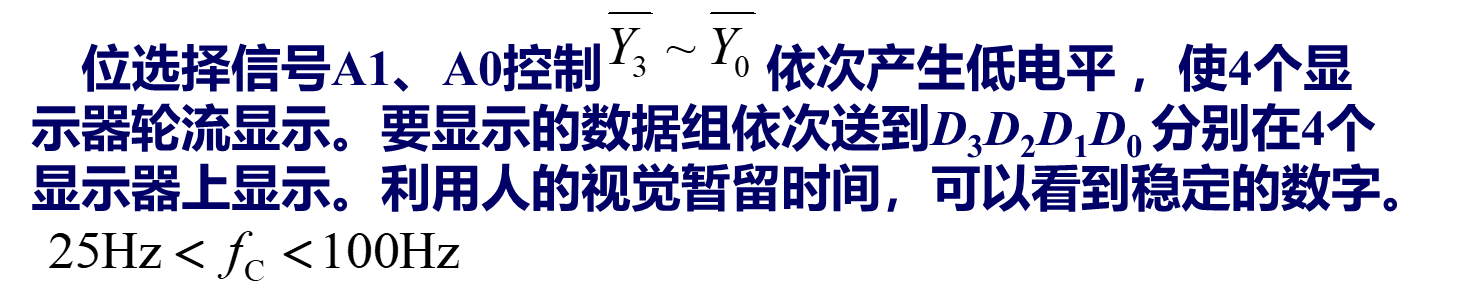

例如:由译码器、显示译码器以及4个七段显示器构成的4位动态显示电路如图所示,试分析工作原理。

3)数据选择器

a. 数据选择器的定义与功能

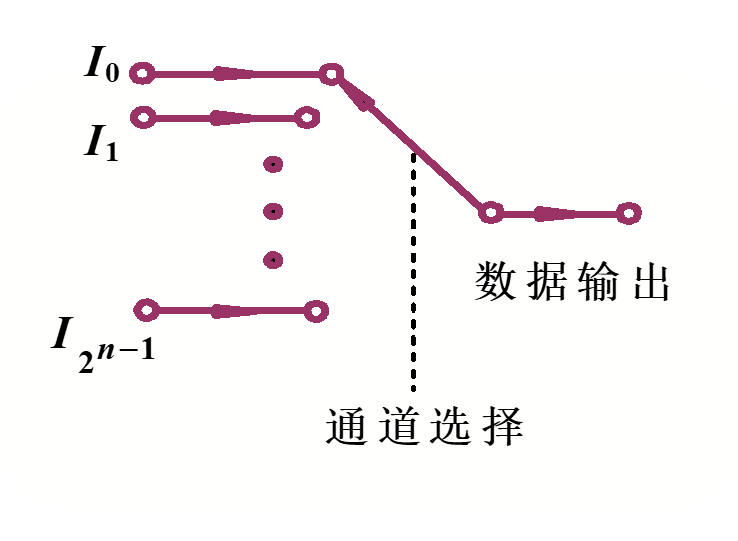

数据选择器:能实现数据选择功能的逻辑电路,它的作用相当于多个输入的单刀多掷开关,又称"多路开关"。

数据选择的功能:在通道选择信号的作用下,将多个通道的数据分时传送到公共的数据通道上去。

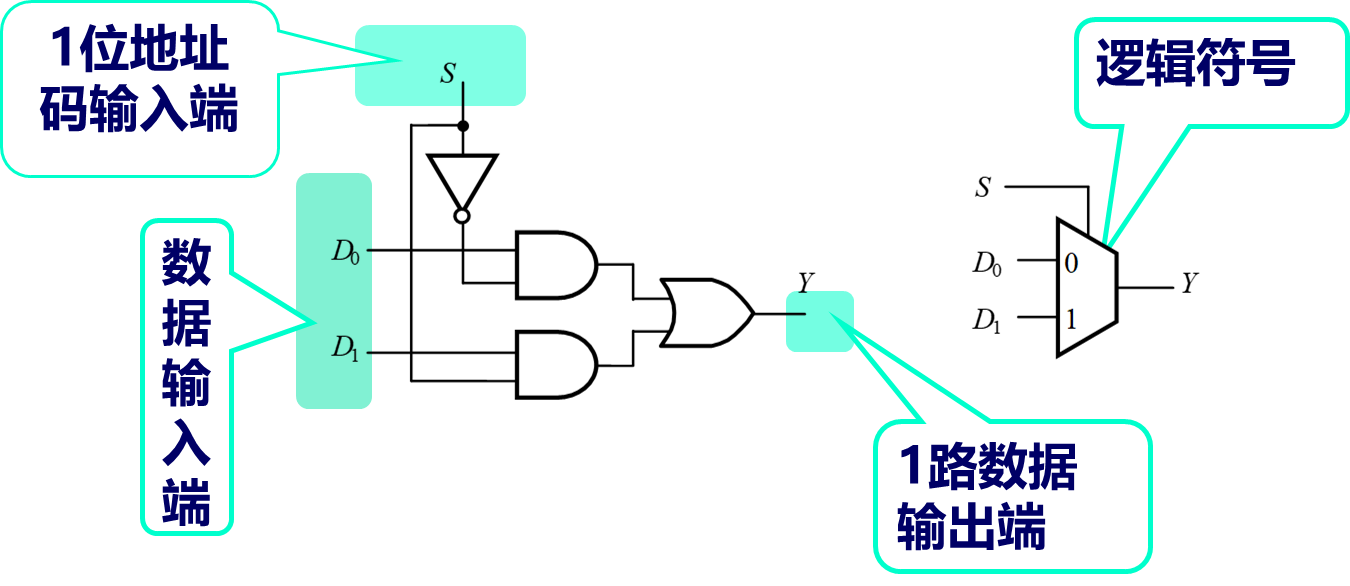

2选1数据选择器

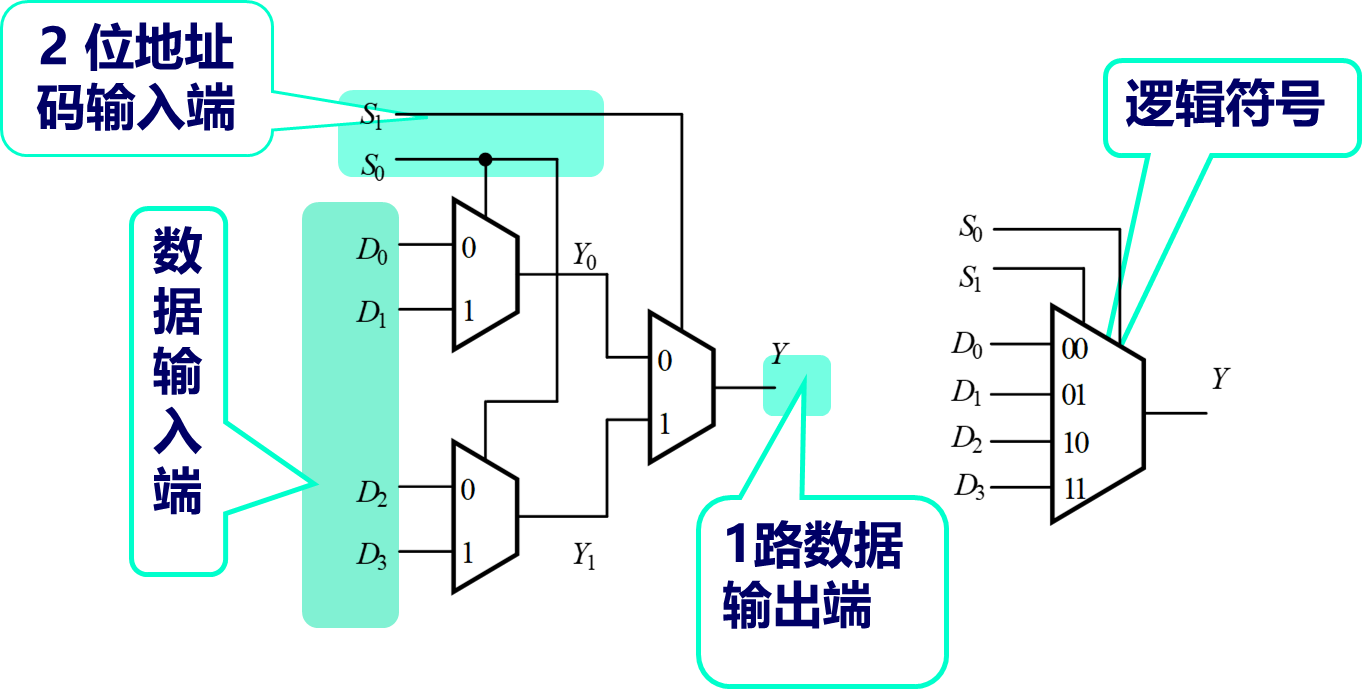

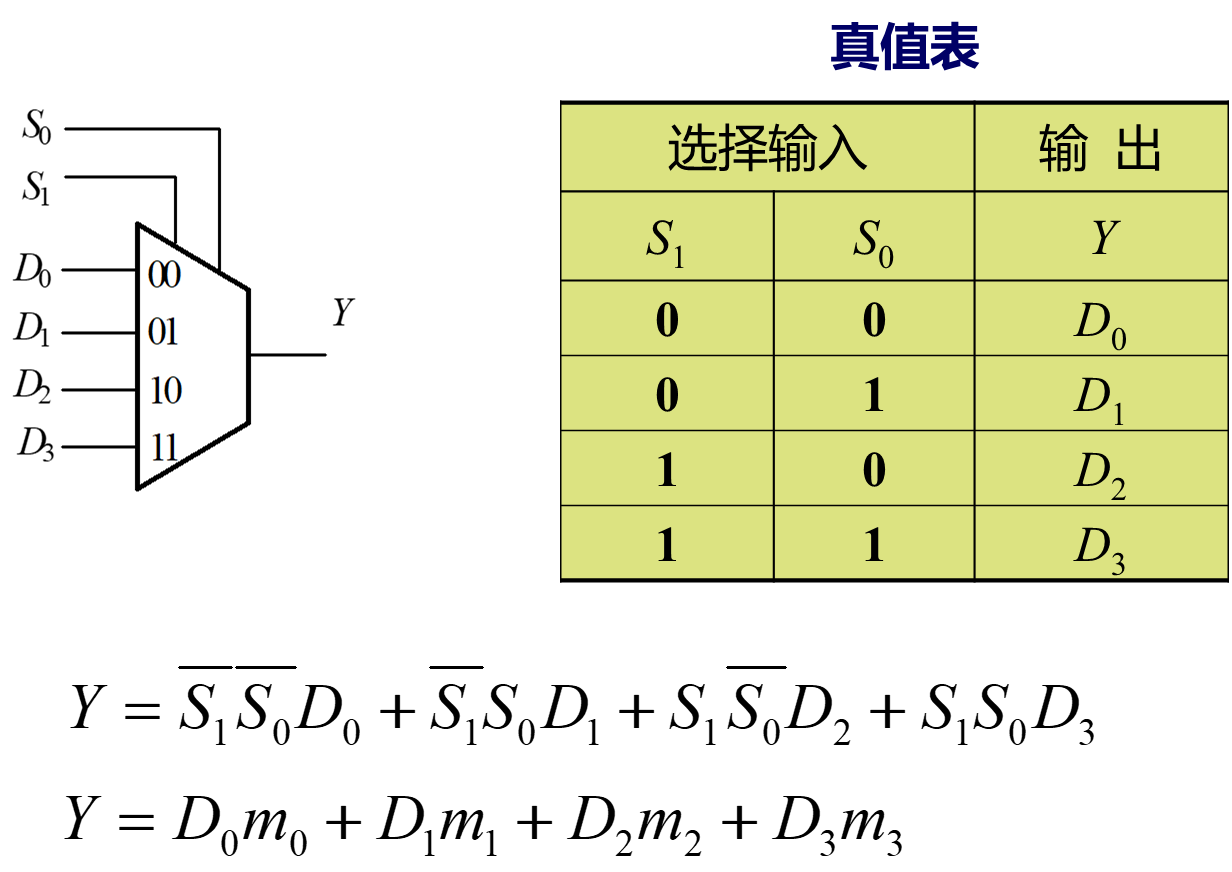

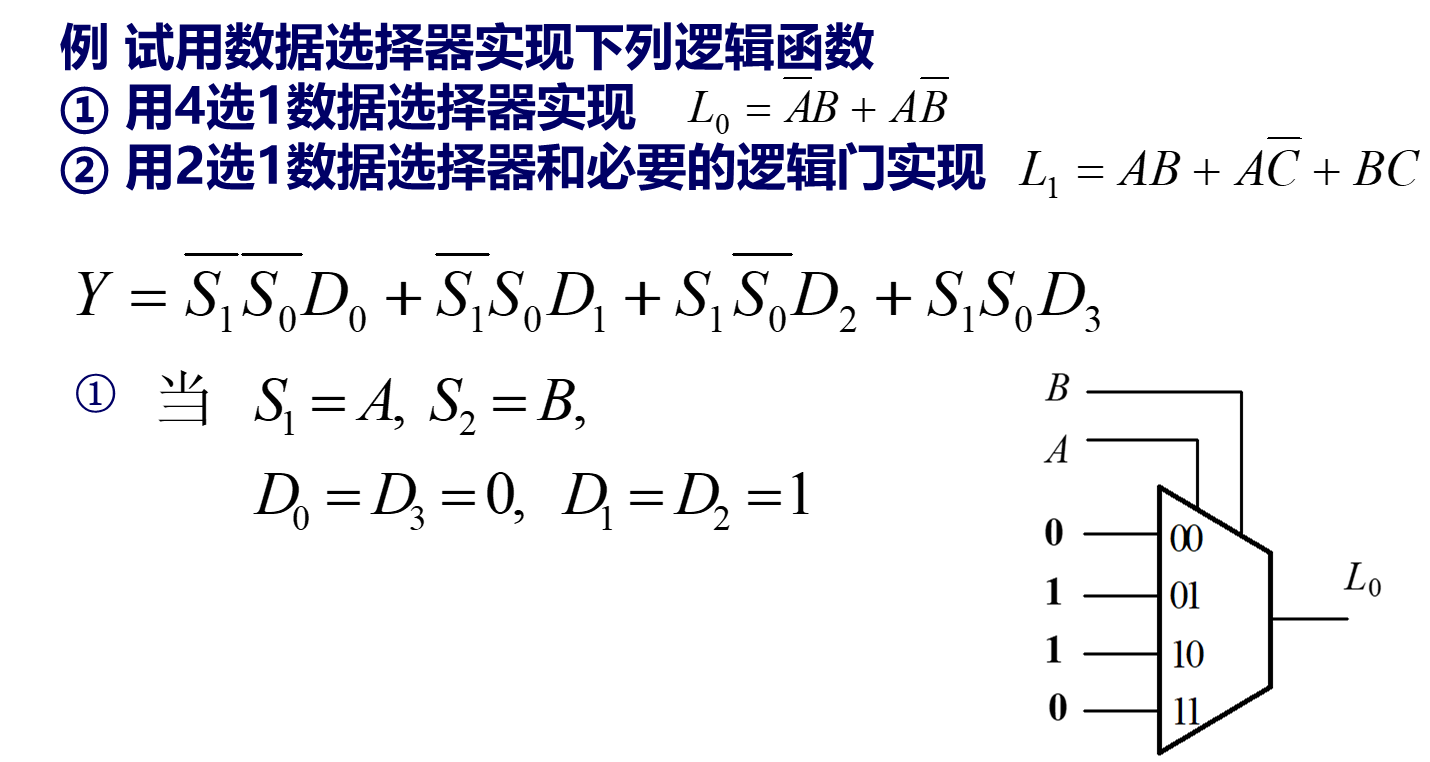

4选1数据选择器

由3个2选1数据选择器构成4选1数据选择器。

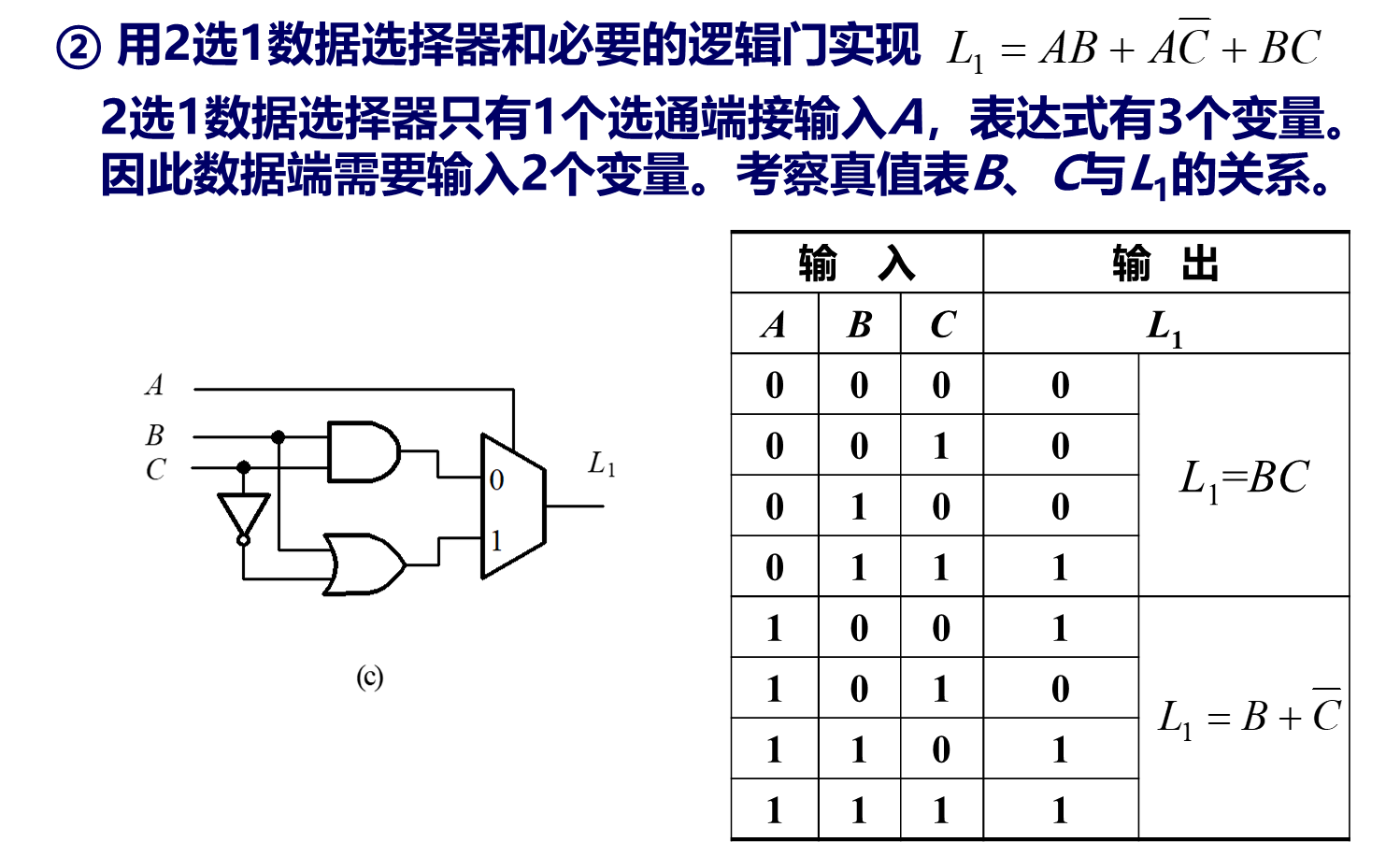

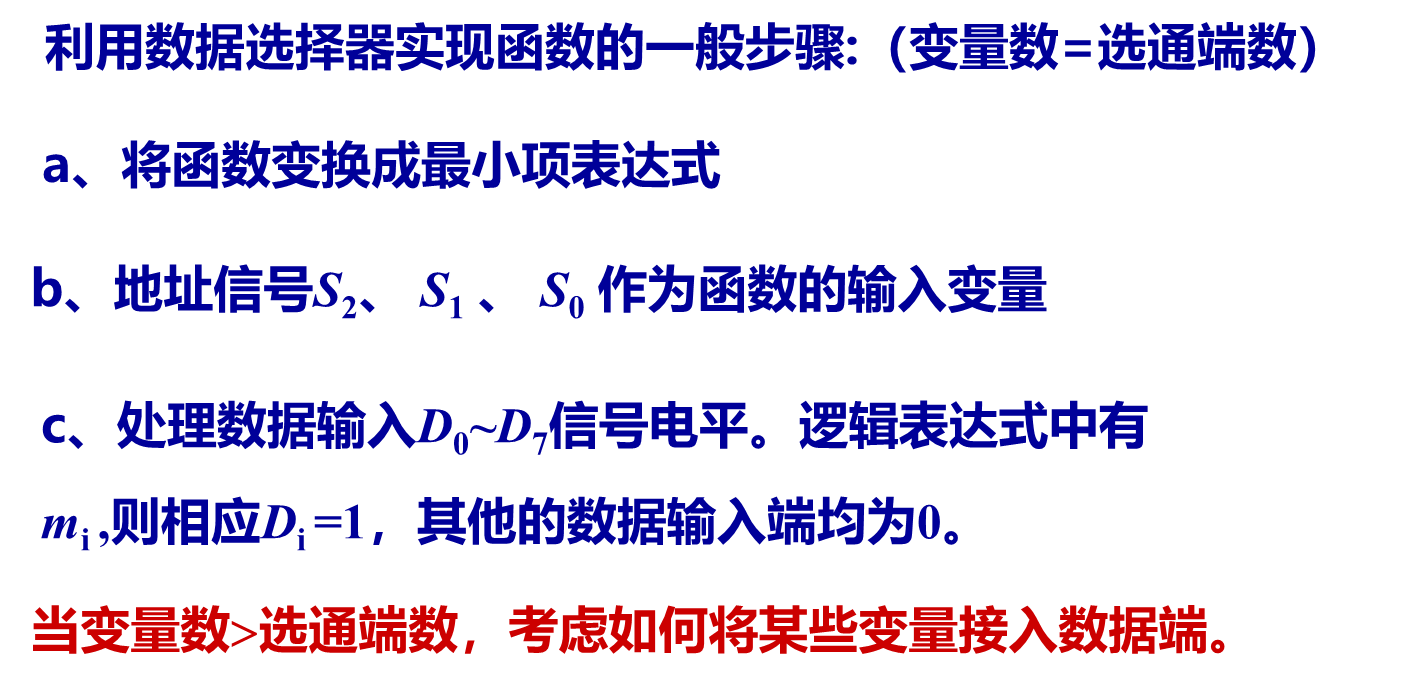

数据选择器实现逻辑函数

总结:

b. 数据选择器的扩展应用

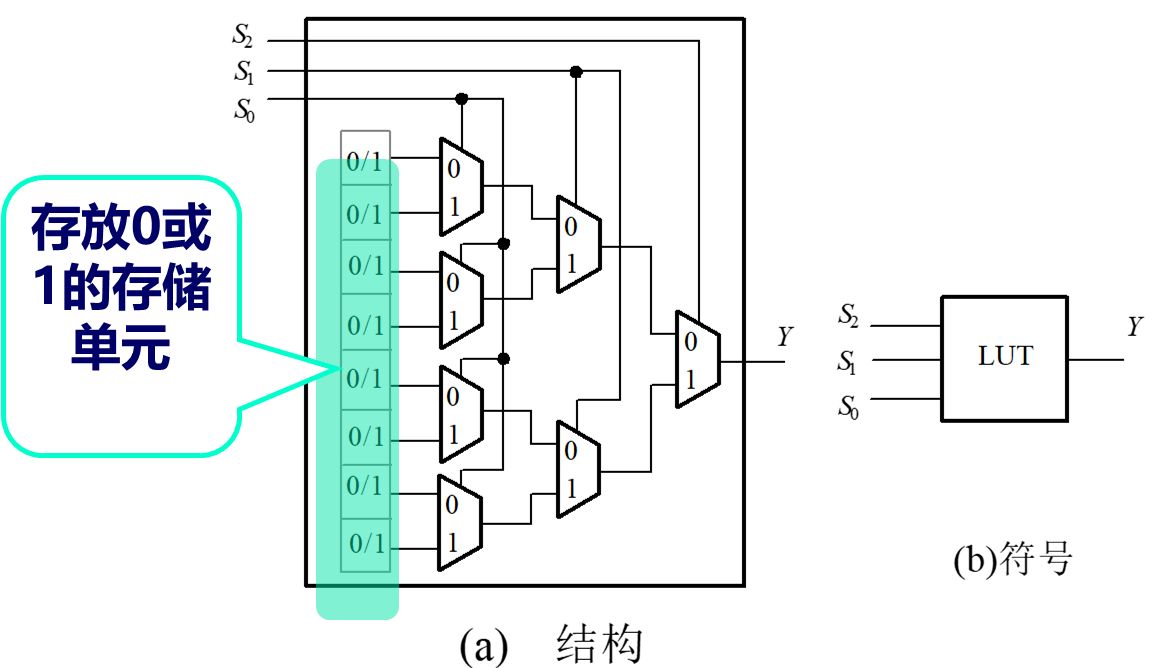

数据选择器构成查找表LUT

构成FPGA基本单元的逻辑块主要是查找表LUT。LUT实质是一个小规模的存储器,以真值表的形式实现给定的逻辑函数。3输入LUT的结构及逻辑符号如图。

用查找表LUT实现逻辑函数

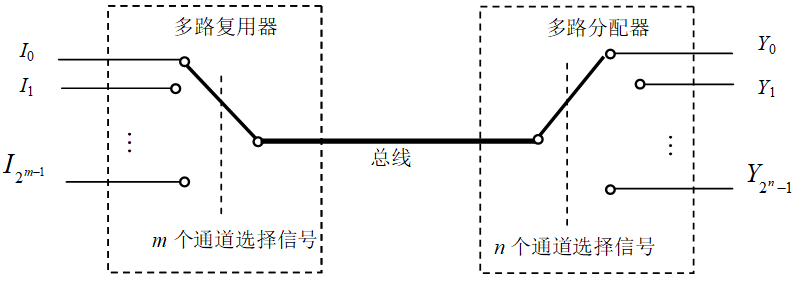

数据选择器、数据分配器与总线的连接

集成电路数据选择器

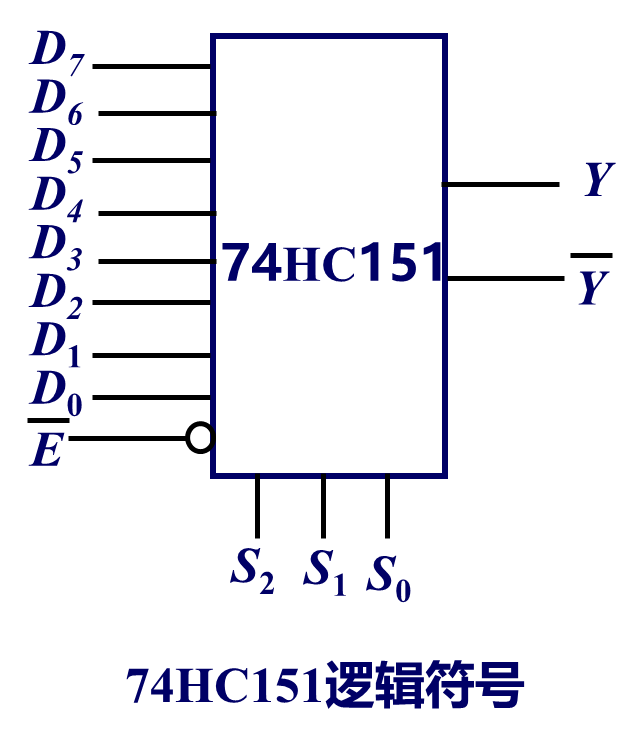

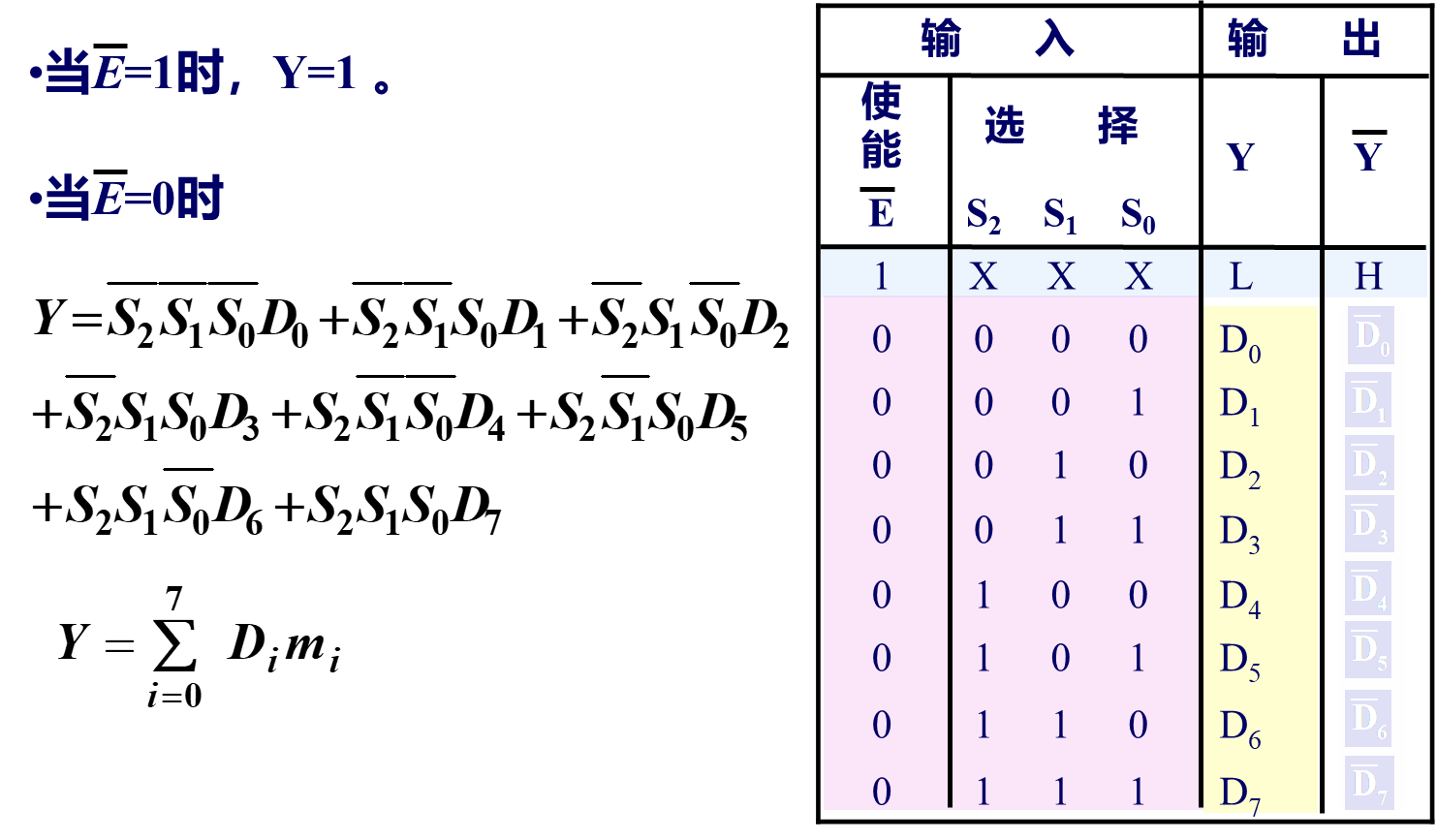

8选1数据选择器74HC151

74HC151的功能表

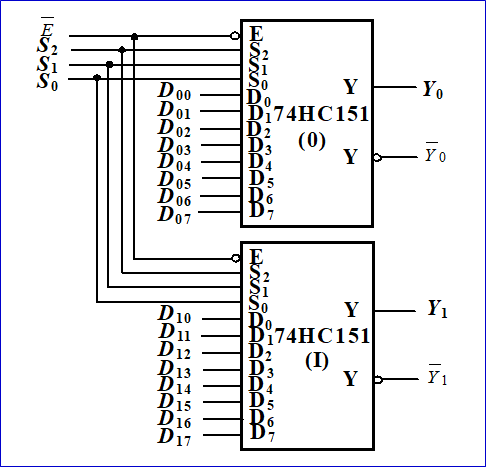

数据选择器的扩展位的扩展

例如:用两片74151组成二位八选一的数据选择器

数据选择器的扩展字的扩展

4)数值比较器

数值比较器:对两个一位数字进行比较(A、B),以判断其大小的逻辑电路。

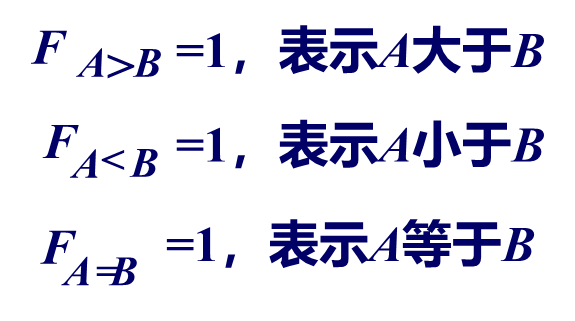

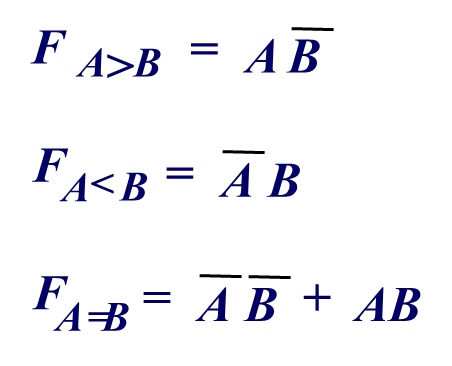

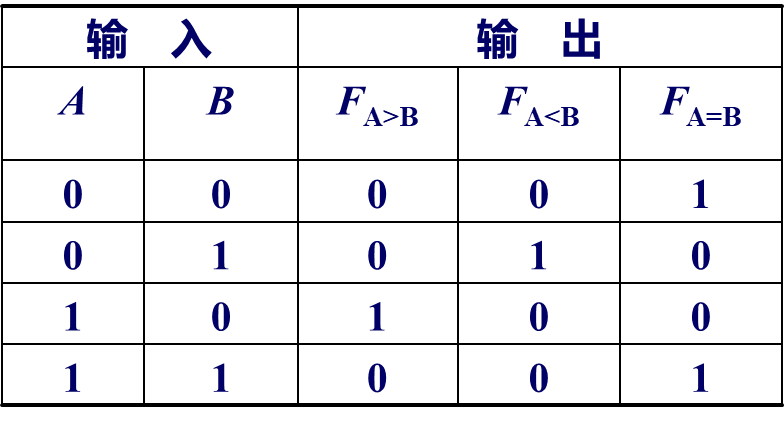

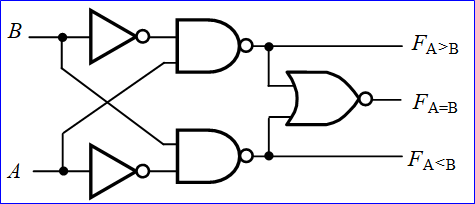

a. 1位数值比较器(设计)

输入:两个一位二进制数A、B。

输出:

一位数字比较器真值表:

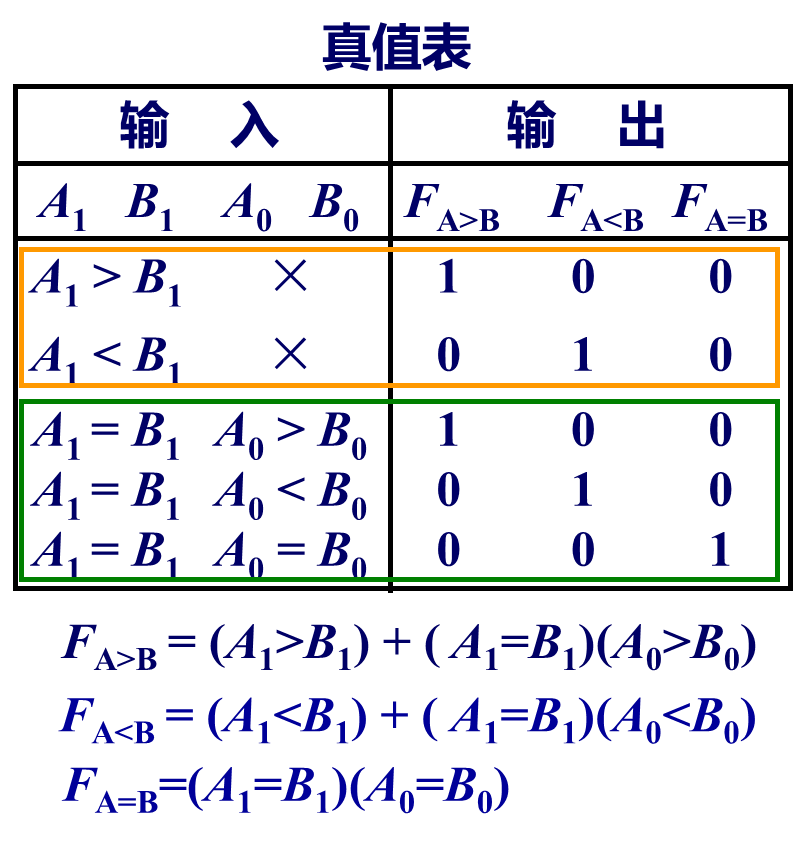

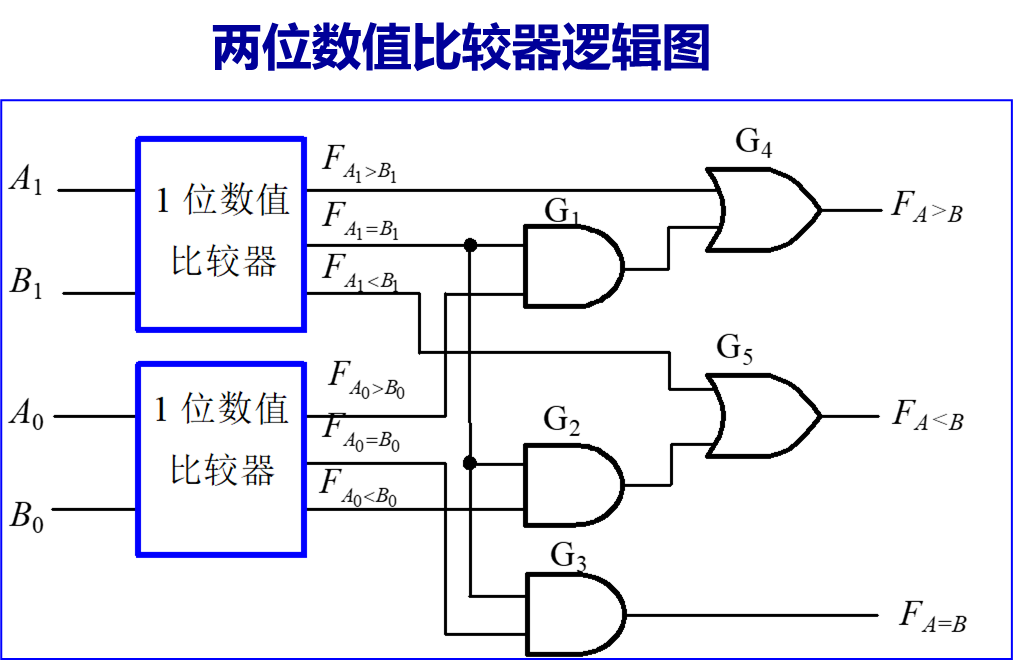

b. 2位数值比较器

比较两个2位二进制数的大小的电路

输入:两个二位二进制数 A=A1 A0 、B=B1 B0

可以用1位数值比较器设计两位数值比较器

用一位数值比较器设计多位数值比较器的原则如下:当高位(A1、B1)不相等时,无需比较低位(A0、B0),高位比较的结果就是两个数的比较结果。当高位相等时,两数的比较结果由低位比较的结果决定。

注意:上述不是真正的逻辑函数表达式,只示意逻辑关系。

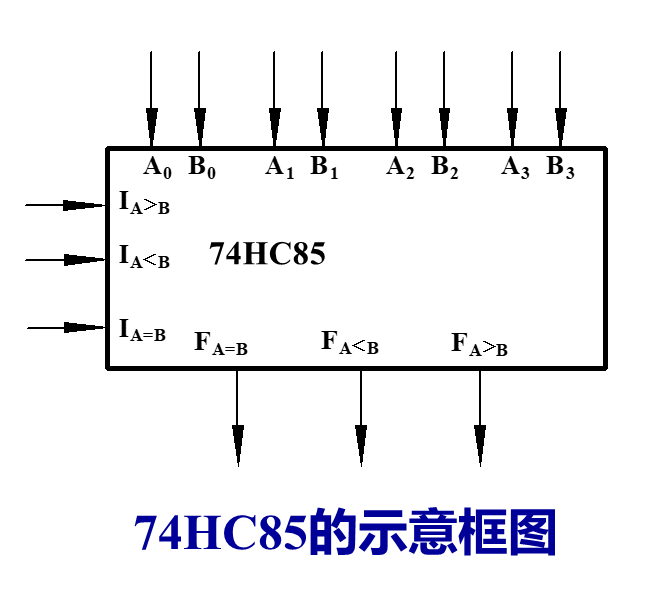

c. 集成数值比较器

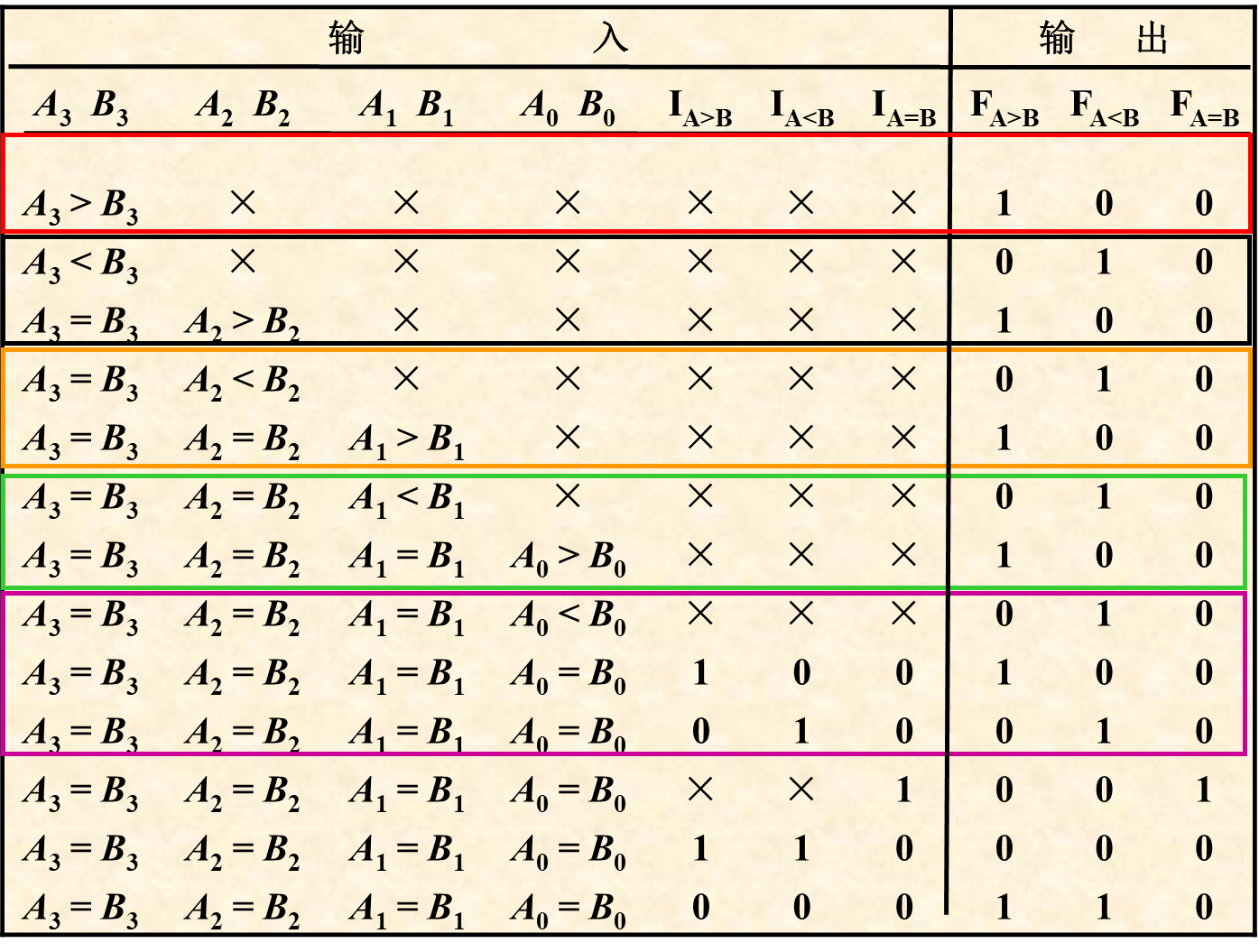

集成数值比较器74HC85的功能:为四位数值比较器,工作原理和两位数值比较器相同。

4位数值比较器74HC85的功能表

d. 集成数值比较器的位数扩展

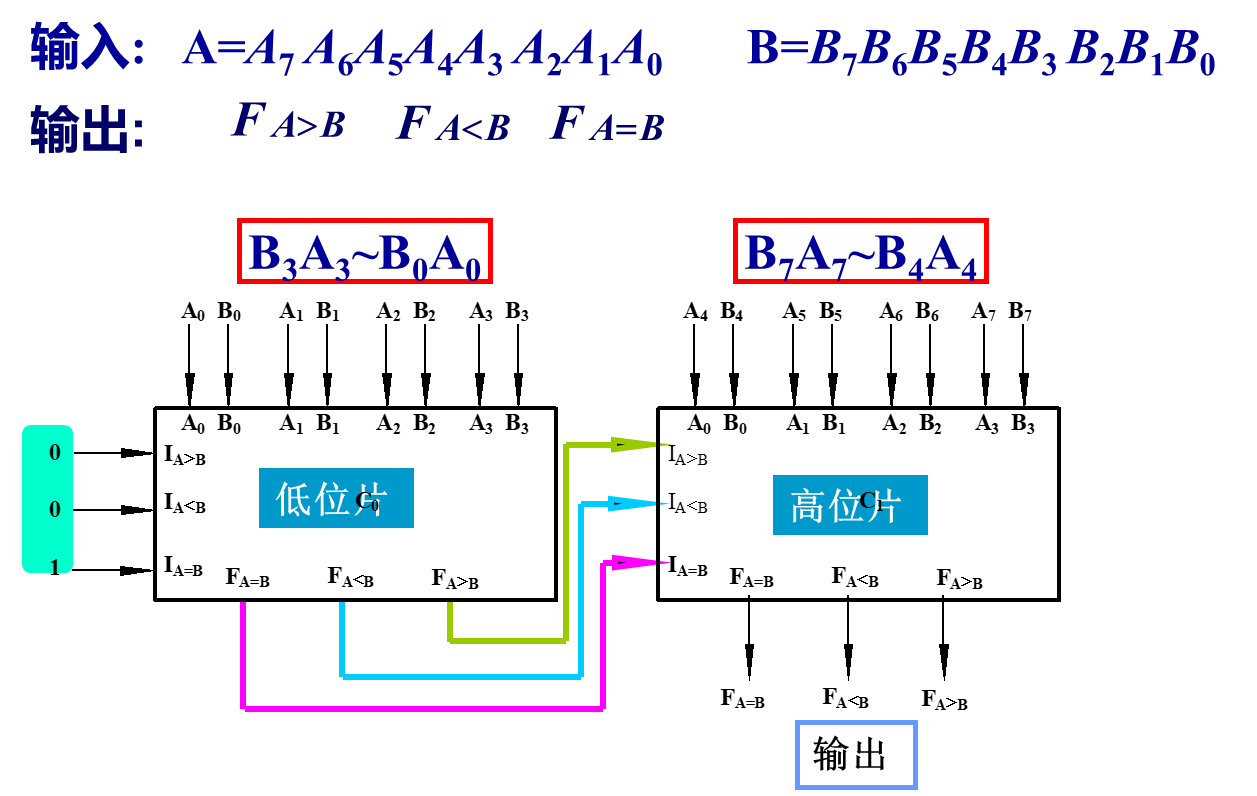

用两片74HC85组成8位数值比较器(串联扩展方式)。

用两片74HC85组成16位数值比较器(串联扩展方式)。

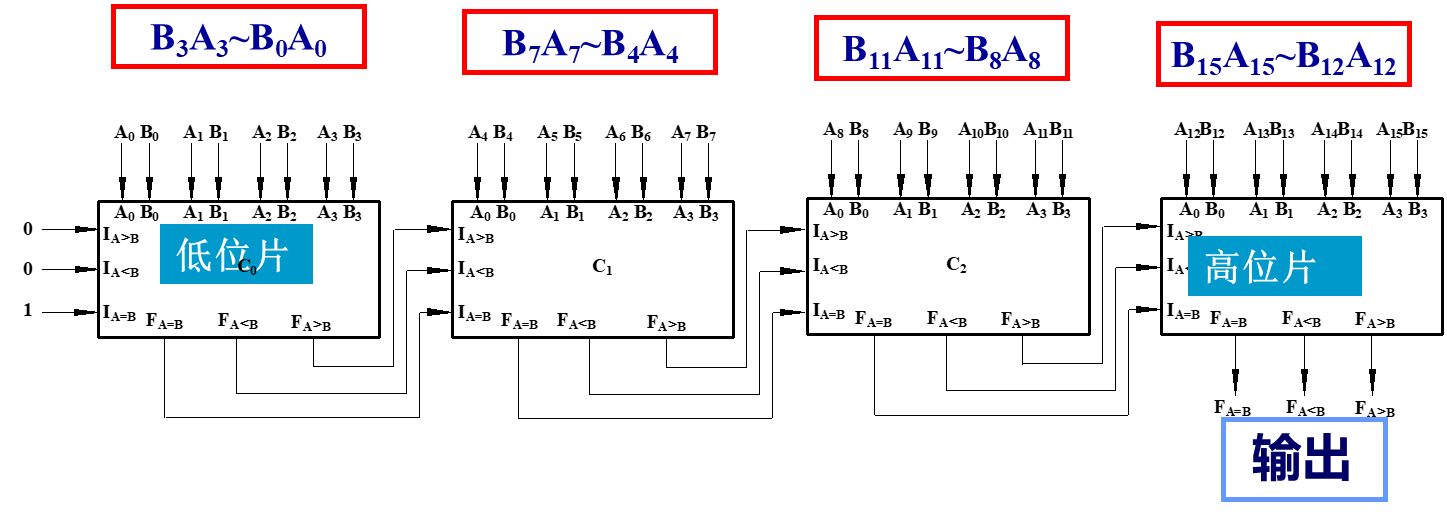

用74HC85组成16位数值比较器的并联扩展方式。

5)算术运算电路

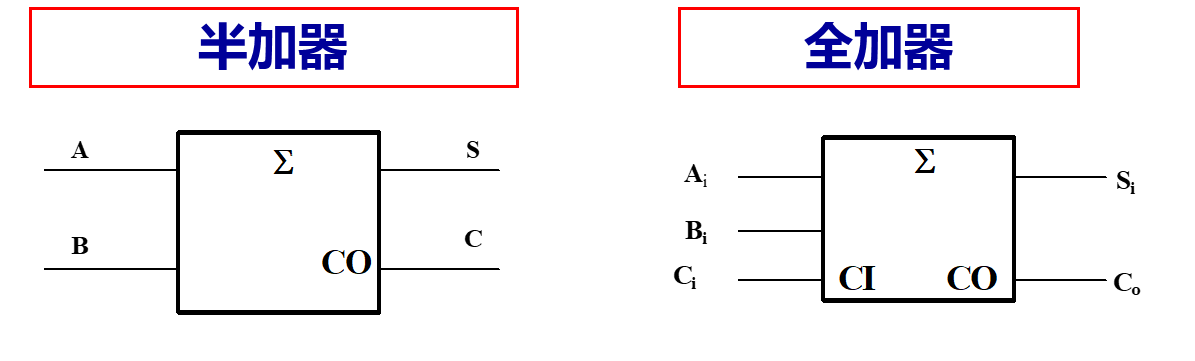

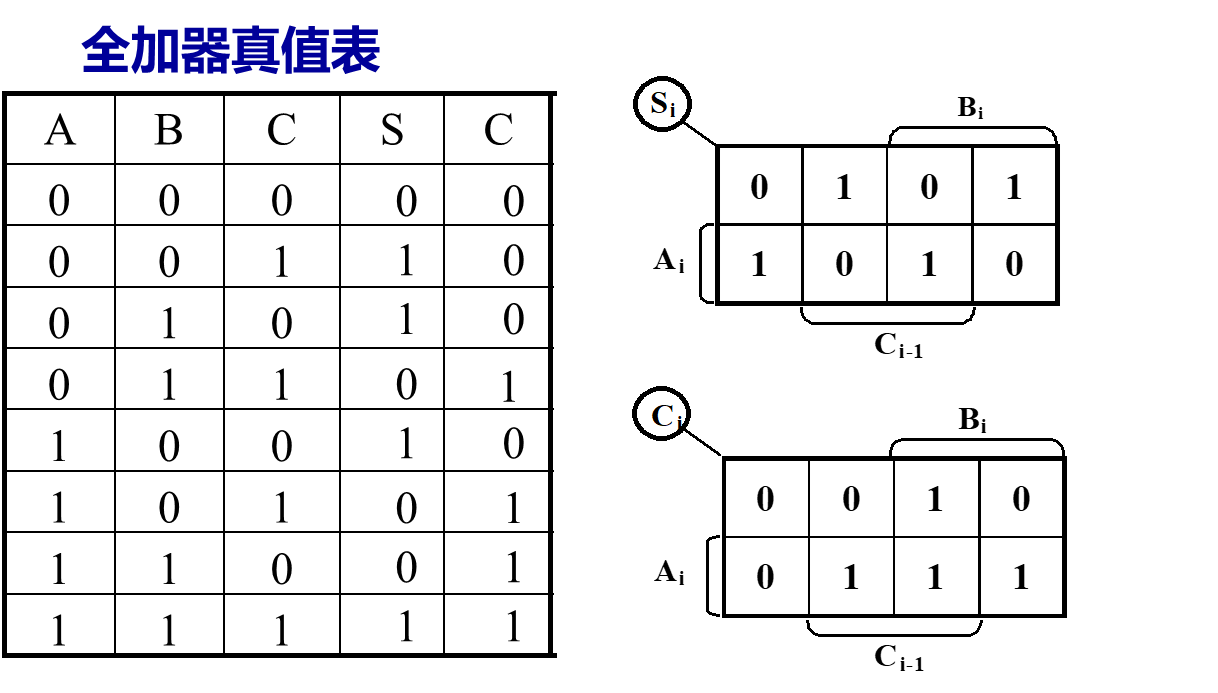

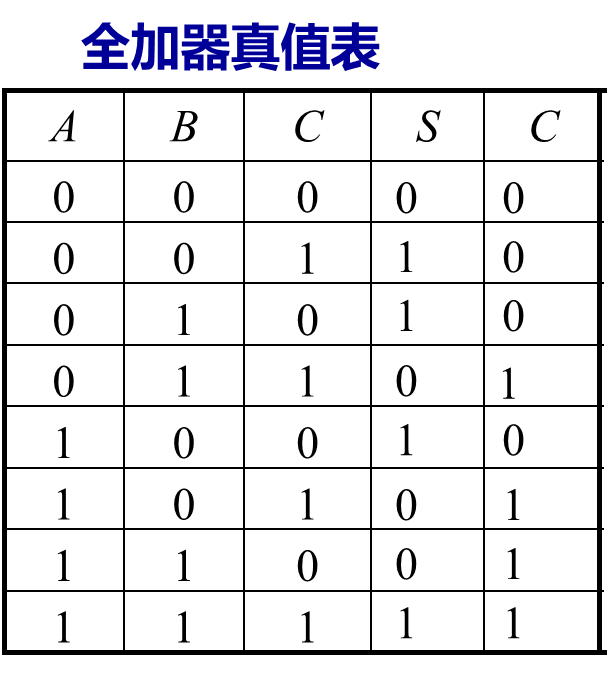

a. 半加器和全加器

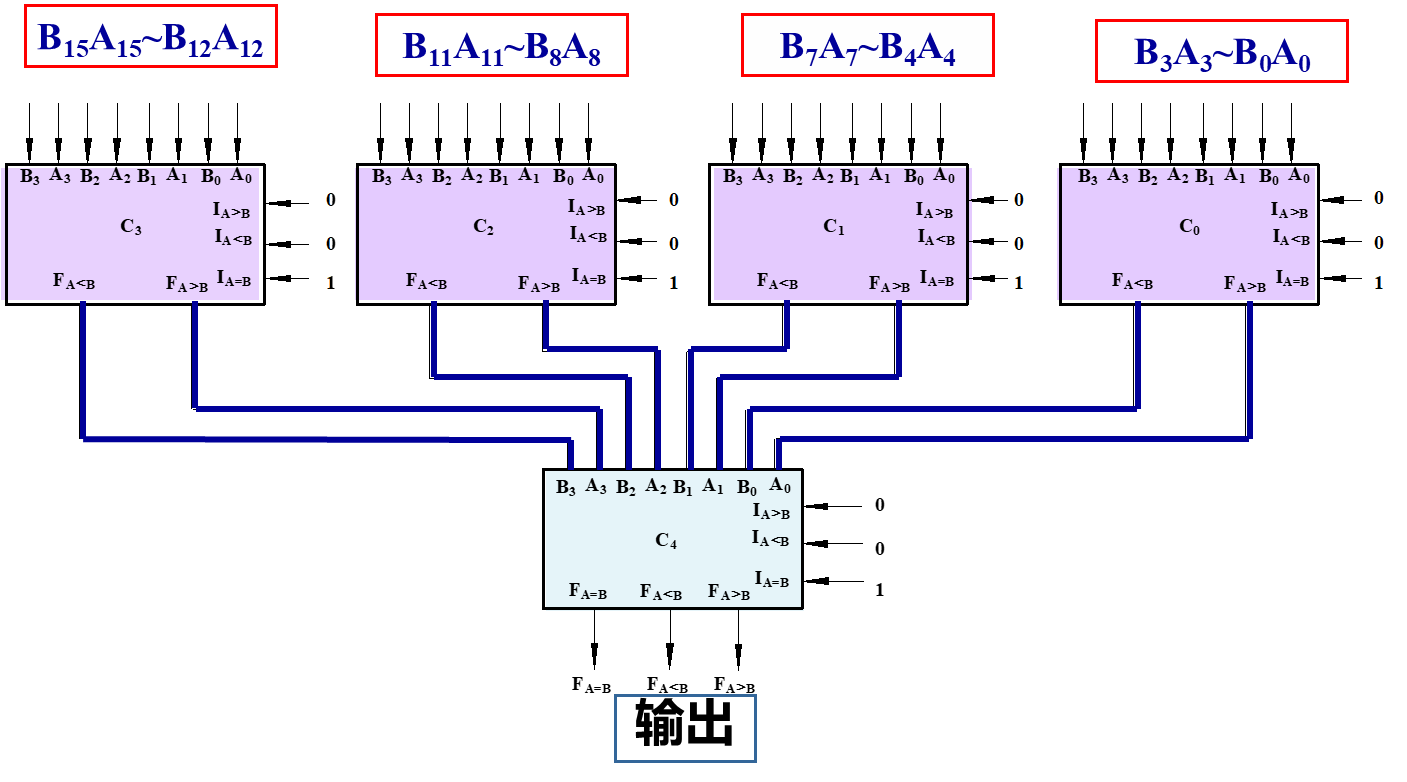

半加器:两个1位二进制数相加时,不考虑低位来的进位的加法

全加器:在两个1位二进制数相加时,考虑低位进位的加法

1位半加器:不考虑低位进位,将两个1位二进制数A、B相加的器件。

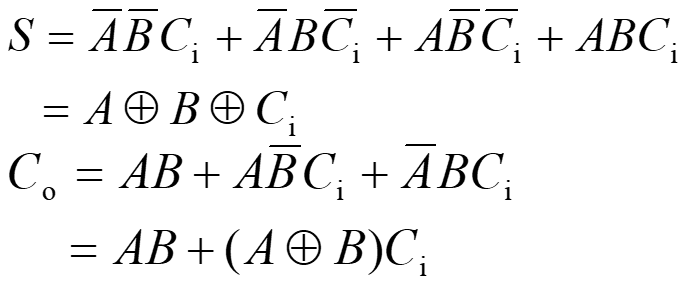

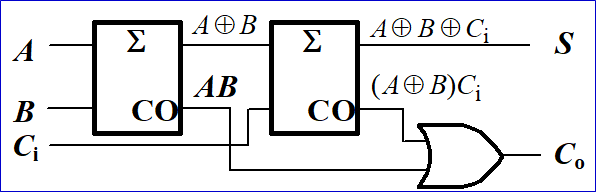

全加器:能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。

于是,全加器的逻辑表达式为

逻辑图如下:

b. 加法器的应用

观察全加器真值表,ABC有奇数个1时S为1;ABC 有偶数个1和全为0时,S为0。可以考虑用全加器组成三位二进制代码奇偶校验器。此外还可以考虑构成多位数加法器。

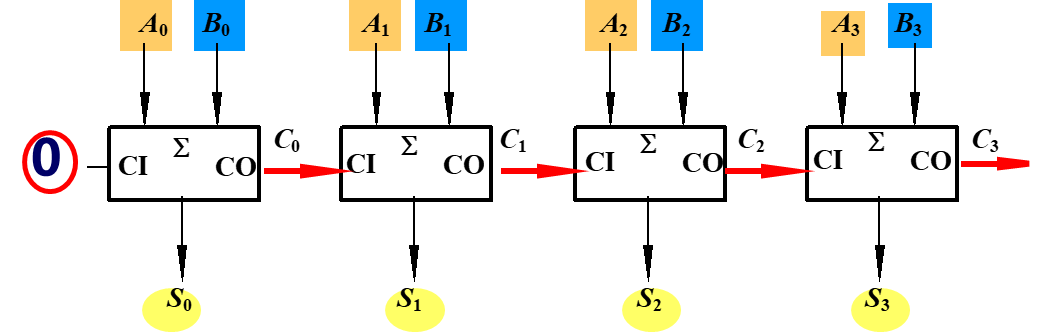

多位数加法器:

如何用1位全加器实现两个四位二进制数相加? A3 A2 A1 A0 + B3 B2 B1 B0 =?

串位进行加法器:低位的进位信号送给邻近高位作为输入信号,采用串行进位加法器运算速度不高。

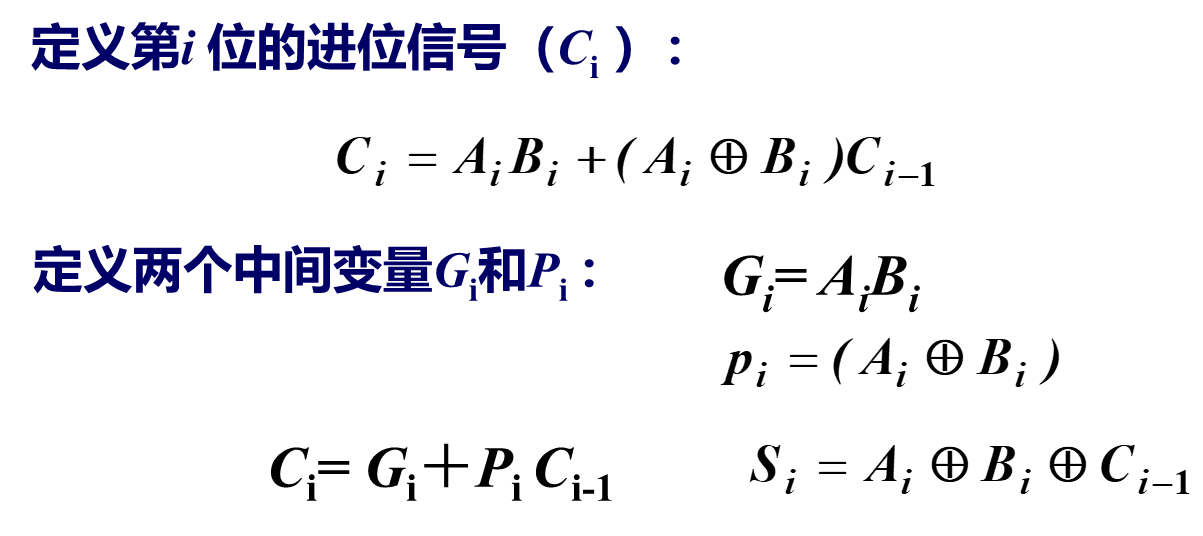

超前进位加法器:

提高运算速度的基本思想:设计进位信号产生电路,在输入每位的加数和被加数时,同时获得该位全加的进位信号,而无需等待最低位的进位信号。

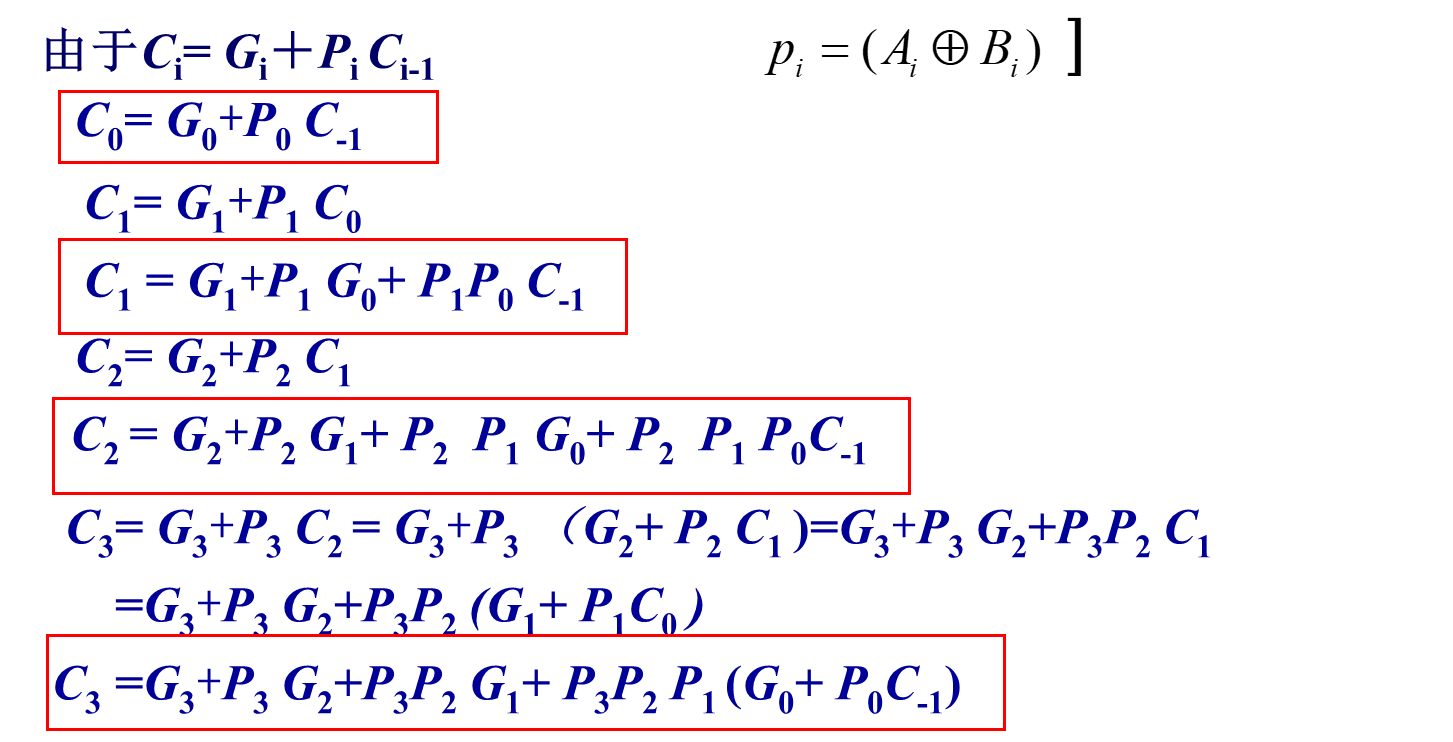

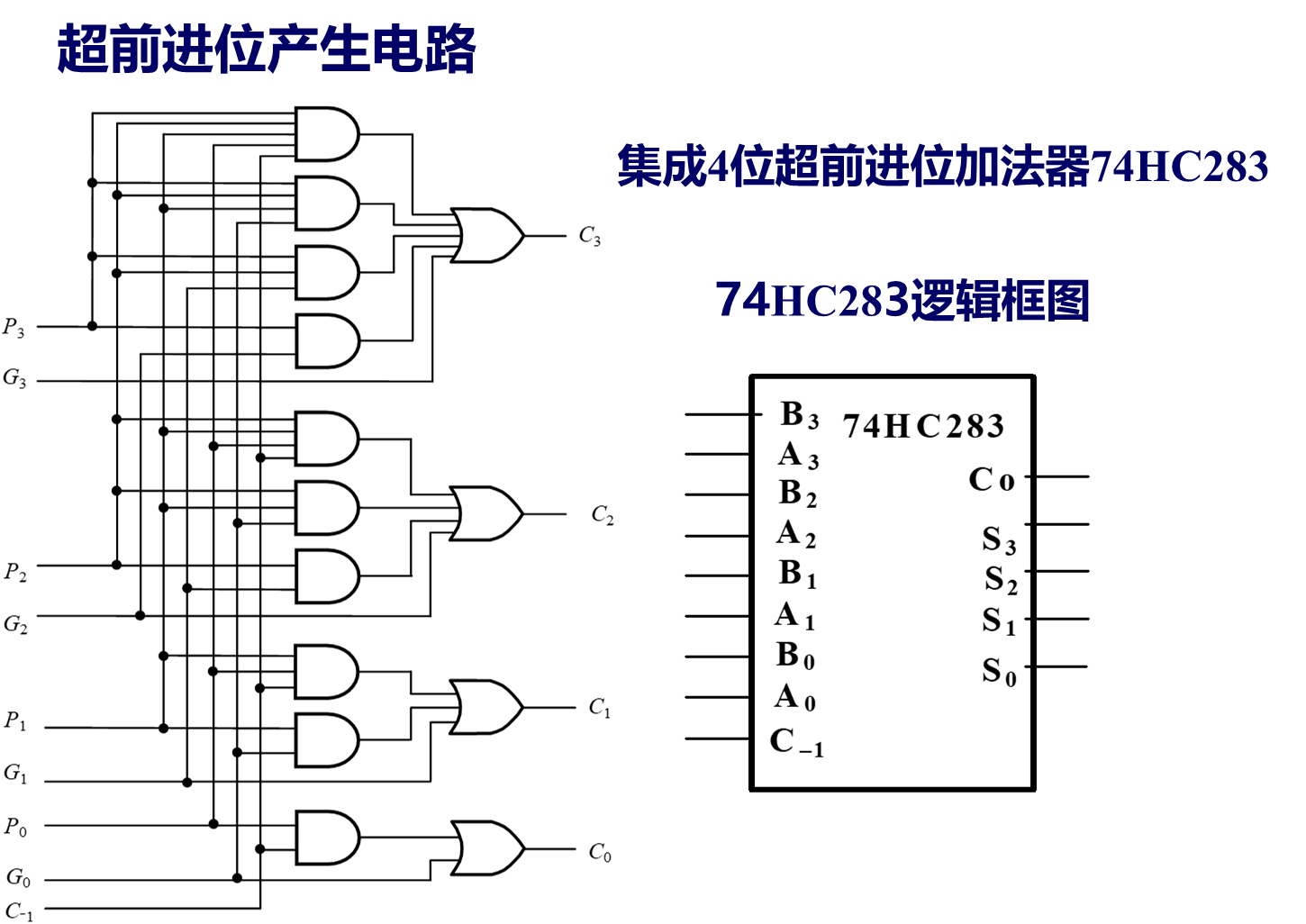

4位全加器进位信号的产生:

进位信号只由被加数、加数和C-1决定,而与其它低位的进位无关。提高了速度,但位数增加时,进位电路复杂度增加。

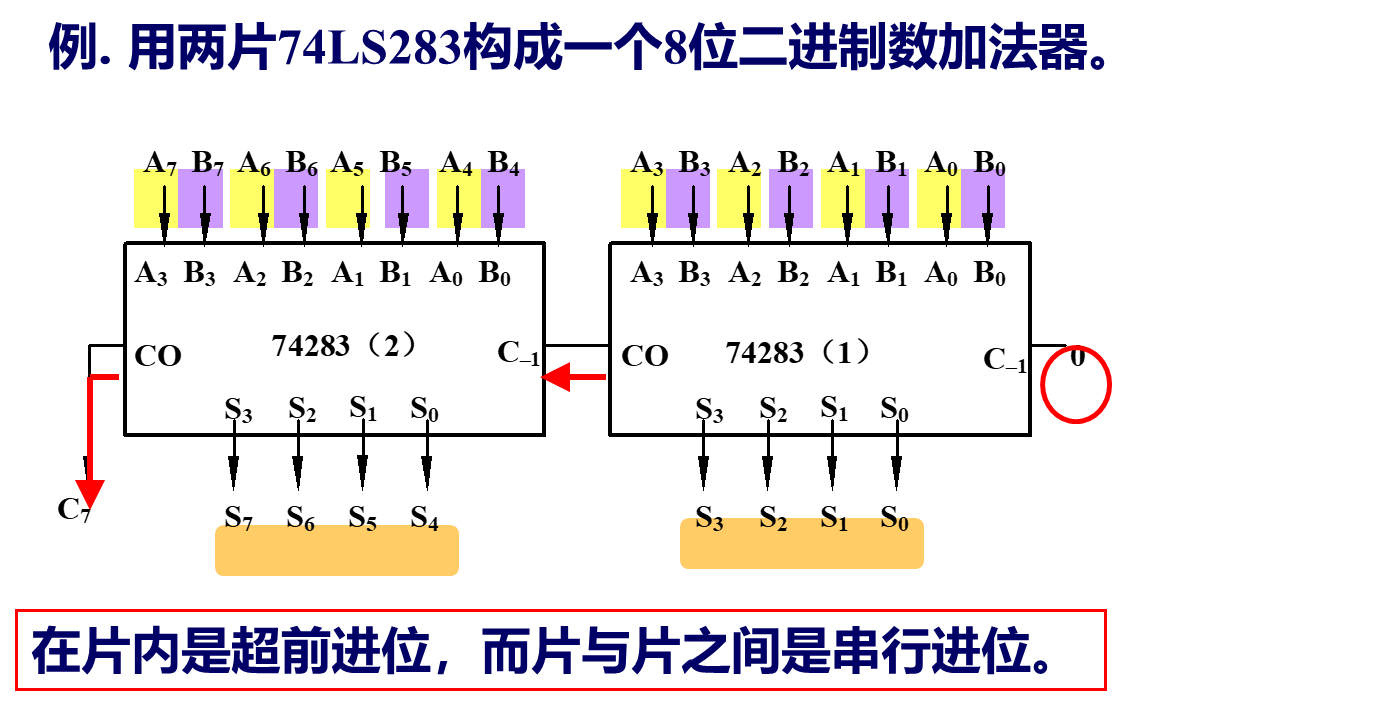

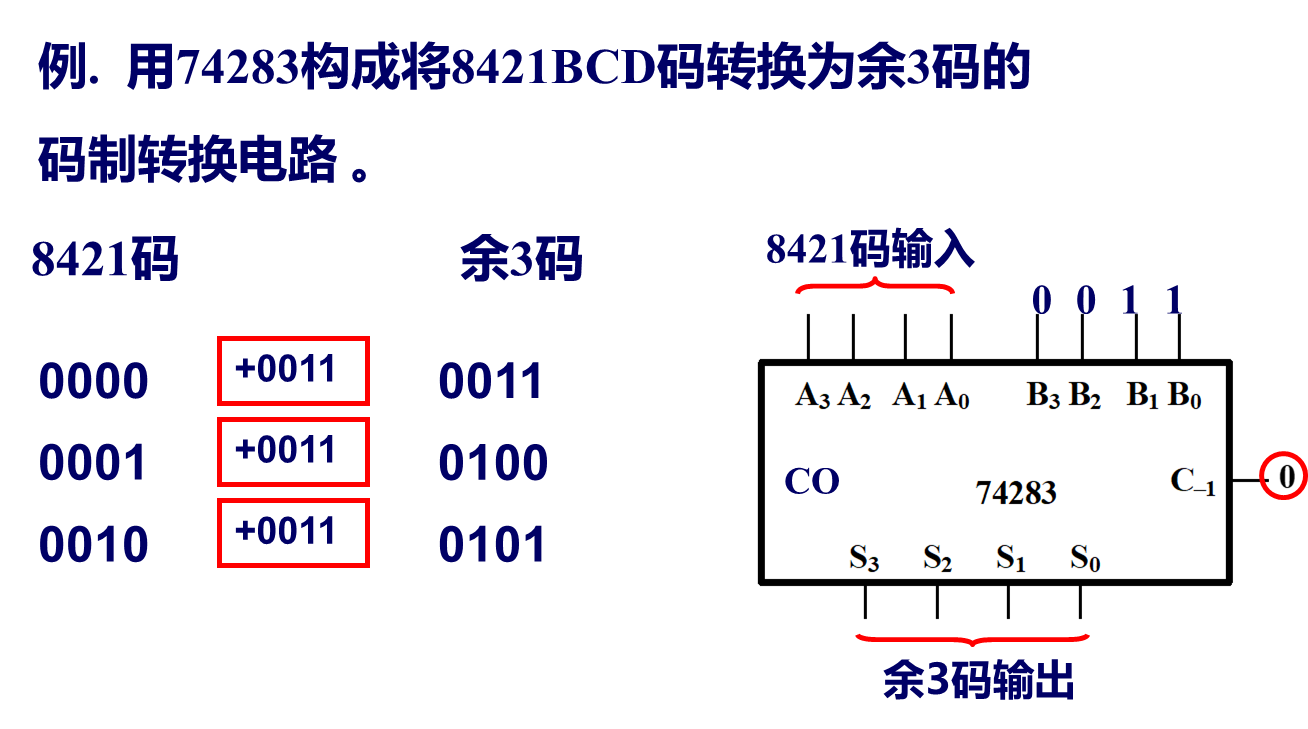

超前进位加法器74LS283的应用

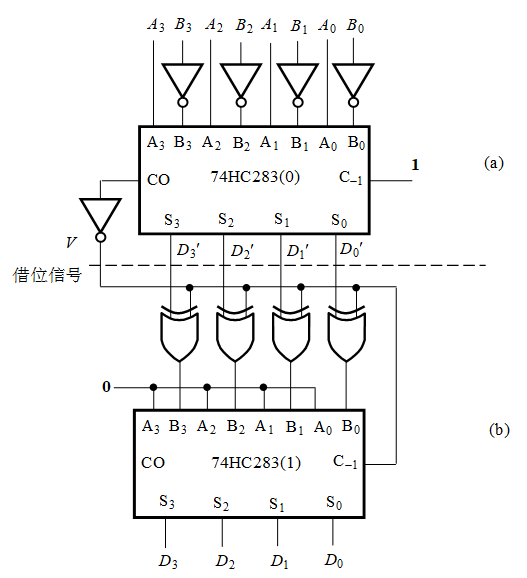

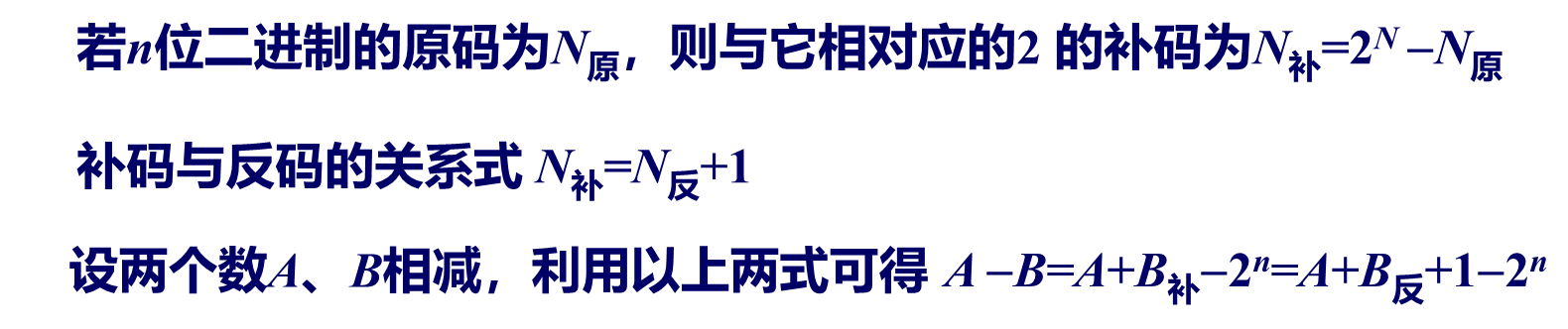

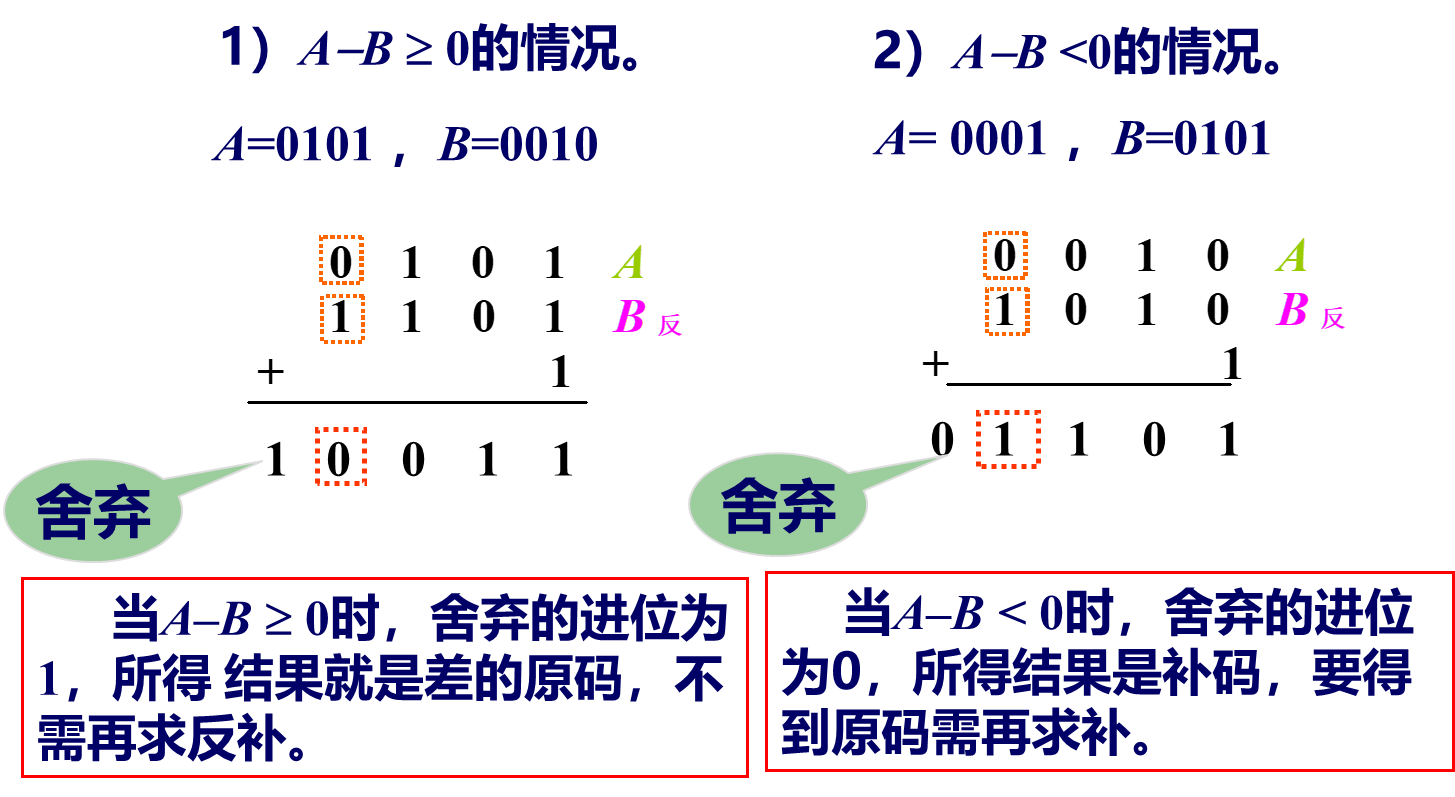

c. 减法运算

在实际应用中,通常是将减法运算变为加法运算来处理,即采用加补码的方法完成减法运算。

输出为原码的4位减法运算逻辑图