DFT的几点理解(二)

1 概述

一款芯片奔着量产的芯片从最开始就应该考虑芯片的design for test(DFT),作为芯片设计前端的人员不仅要懂设计,也需要了解甚至懂点DFT,因为DFT不是只在中后端进行,在前端也需要做相应的设计。此仅以此笔记记录该此的项目总结,如有后续或修改补充,后续进行……

2 芯片设计中DFT的基本分类

芯片设计包括数字设计和模拟设计,DFT设计是针对数字设计部分;数字部分中又可以分为logic部分和存储部分,分为scan和mbist测试。相关的介绍可参考如下链接:

DFT中的SCAN、BIST、ATPG基本概念-CSDN博客

3 DFT在设计时的注意事项

3.1 在芯片设计之初需要考虑端口、时钟、电源的结构

在做scan设计时有一部分是要在设计里完成的,DFT的端口的定义和复用是需要考虑仔细的。关于端口的定义首先需要清楚测试在哪个阶段,是cp阶段(量产芯片封装前)还是ft阶段(量产芯片封装后),不同阶段对于芯片可见的端口数量和功能上都是有差异的;其次还需要考虑在具体的那个阶段下可用的端口有哪些,该怎么复用。下表给出了一个数字端口较少情况下的端口复用和模式选择的一种实现选择。

| dft需要的端口 | 芯片数字端口 | |||||

| iterms | scan | mbist | I/O | name | I/O | |

| 1 | scan_clk | tck | input | SCK | input | |

| 2 | scan_se | tms | CSN | |||

| 3 | scan_reset | trst | G0 | |||

| 4 | scan_in | tdi | SDI | |||

| 5 | scan_out | tdo | output | SDO | output | |

| dft功能模式选择通过SPI寄存器来选择,包括dc scan/ac scan/mbist三种模式 | TESTMODE | input | ||||

| RESETN | input | |||||

| 通过TESTMODE引脚选择进入test_mode,通过SPI控制测试模式的选择,实现dc scan/ac scan/mbist的选择,通过RESETN引脚来实现dc scan/ac scan/mbist的复位。(这里会牺牲dft_mode寄存器不能插入链中) | ||||||

如果芯片端口可用的较多,则将mbist的端口和scan的端口分开,这样控制实现简单,减少出错的概率,同时也能减少测试时间。

dft的模式选择、使能、时钟、复位、输入输出也是需要仔细考虑和check的。如果时钟来源于模拟且时钟频率还受寄存器控制,这个需要考虑在scan时对应寄存器变化的情况;如果涉及到电源域有power switch的情况还要考虑在进行测试时不能影响时钟和电源。

关于scan部分可参考如下链接:

RTL可测性设计—DFT_哔哩哔哩_bilibili

关于DFT中几点的理解_芯片dft设计-CSDN博客

3.2 关于mbist的设计和更新优化应该和芯片功能逻辑分开维护

之前遇到过一个项目,它是不同流片的版本在优化迭代更新的,但是第一版为量产增加DFT逻辑时将mbist和function逻辑的代码是混到一起的。后来在下一版时需要换工艺、同时也有function逻辑的增加和优化,而且第一版mbist不是通过标准的生成流程来做的,导致后来的逻辑优化更新和mbist随着function变化的更新都比较难处理。后来咨询过专业做DFT的人,建议是将mbsit逻辑和function逻辑分开维护,这样两者都方便各自的更新优化。

关于mbist的介绍可以参考下面的链接:DFT专题_MBIST_Introduction_哔哩哔哩_bilibili

如下链接提到的文档介绍了mbist和JTAG之渐的关联,有效的提供了结构上的视野。

基于JTAG的MBIST设计实现.pdf - 资料区 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

将mbist逻辑和function逻辑分开维护,可以在综合后的网表中插入mbist逻辑,下面的链接讲了在RTL中和netlist中插入mbist的优劣:

Mbist在RTL和netlist插入的区别??? - 数字IC设计讨论(IC前端|FPGA|ASIC) - EETOP 创芯网论坛 (原名:电子顶级开发网) -

3.3 memory的分组测试

如果芯片中有较多的memory,如果同时测试,则可能使测试功耗大于芯片实际承受的功耗从而造成对良率的评估影响甚至会是芯片的损坏,所以在进行mbist设计时需要考虑功耗问题,即将memory进行分组测试。下面的链接讨论了memory分组测试的考虑:

Mbist 测试功耗问题 - 讨论区 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

关于memory分组既要考虑到测试功耗、测试成本,还需要考虑到实际使用的情况,比如实际有10组memory同时工作,但在测试时最多将5组memory进行同时测试。需要考虑到这样做的利弊是否在项目的考虑中。

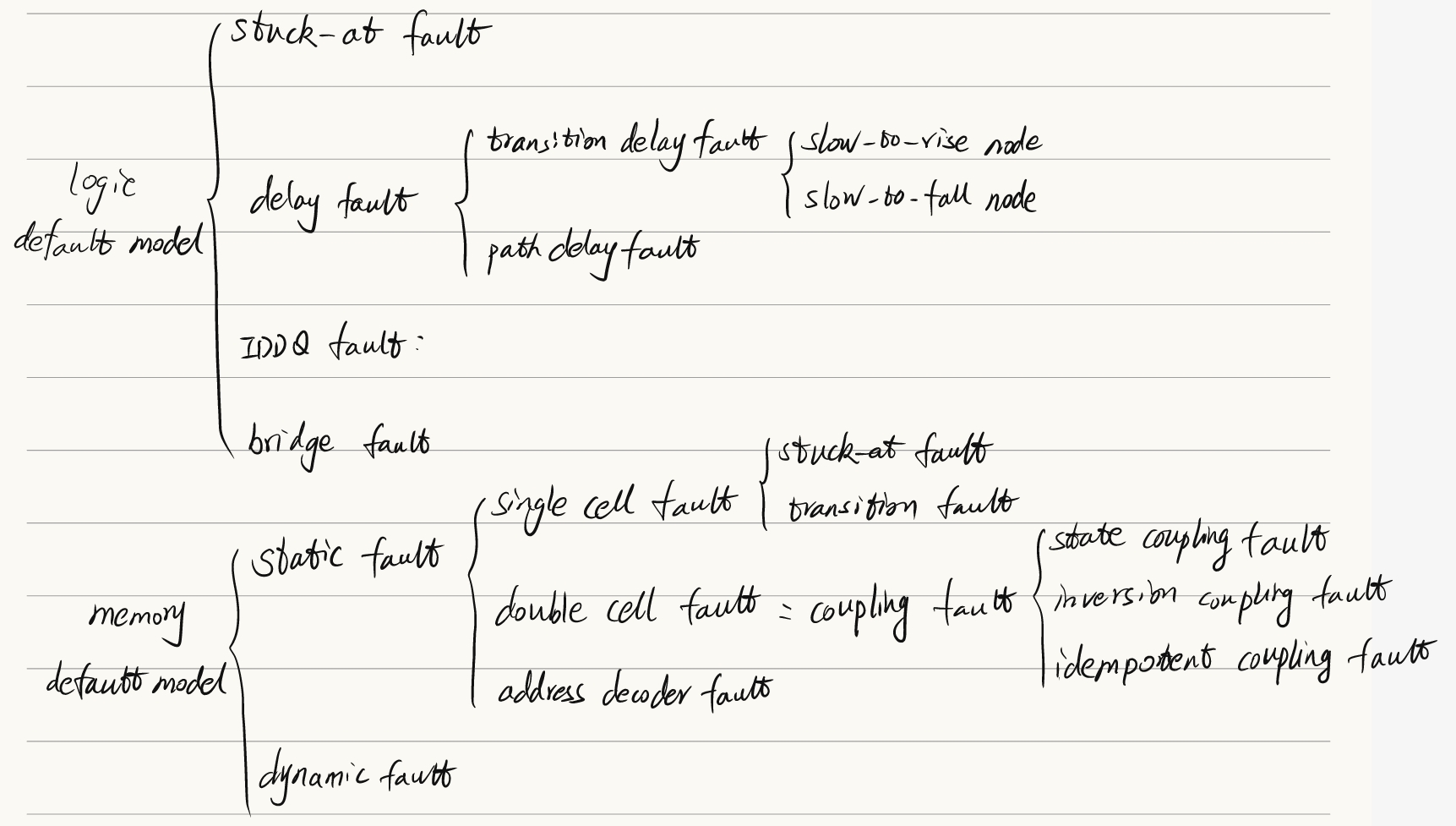

3.4 故障模型和覆盖率

在项目中需要对DFT的覆盖率提出要求,而且在不同的故障模型下对覆盖率的要求也不一样,对于覆盖不到的地方需要衡量对芯片的量产成功的影响,如果关乎芯片命脉,则必须想办法覆盖到。对于故障模型下图简单总结了其分类,具体参看如下链接。

DFT中Fault Model的介绍 - 知乎 (zhihu.com)

3.5 AC SCAN和DC SCAN的区别

AC SCAN和DC SCAN是根据测试频率和测试目的来划分的,AC SCAN又被称为at-speed test,是高速测试fast test,主要测试芯片在正常频率下的transition是否符合要求,越是工艺先进的芯片,工作频率越高的芯片这个是必不可少的。进一步的介绍参考如下链接:

芯片测试的DC/AC/Fast/slow模式_dc测试-CSDN博客

后续有再补充,有错误后续再修改,阅读者请参考,仅供参考……