数字系统设计与verilog hdl第8版王金明

习题1

1.1现代EDA 技术的特点有哪些?

1.2什么是 Top-down 设计方式?

1.3数字系统的实现方式有哪些?各有什么优缺点?

1.4什么是IP复用技术?IP核对EDA技术的应用和发展有什么意义?

1.5基于FPGA/CPLD的数字系统设计流程包括哪些步骤?

1.6什么是综合?常用的综合工具有哪些?

1.7功能仿真与时序仿真有什么区别?

1.8FPGA与ASIC在概念上有什么区别?

习题2

2.1PLA和PAL在结构上有什么区别?

2.2说明GAL的OLMC有什么特点,它如何实现可编程组合电路和时序电路?

2.3简述基于乘积项的可编程逻辑器件的结构特点。

2.4基于查找表的可编程逻辑结构的原理是什么?

2.5基于乘积项和基于查找表的结构各有什么优点?

基于乘积项的优点(CPLD结构):

速度快、延迟固定

由于结构简单,信号路径短且可预测;

非常适合对时序要求严格的控制逻辑。

控制逻辑高效

适合实现有限状态机(FSM)、地址解码器等;

支持异步逻辑设计。

功耗较低

在静态状态下不消耗大量电流;

适用于电池供电设备。

非易失性(有些CPLD)

上电即用,无需外部配置ROM。

�� 基于查找表的优点(FPGA结构):

高度灵活、可重构

任意n位逻辑函数都可以通过LUT实现;

可以实现非常复杂的组合逻辑和算术运算。

适合大规模设计

单片集成数百万逻辑门;

支持嵌入式块RAM、DSP模块、软核处理器等。

并行处理能力强

所有逻辑单元可以同时工作;

非常适合并行计算任务(如图像处理、神经网络推理)。

开发工具成熟

支持高级综合(HLS),可以用C/C++生成硬件逻辑

2.6CPLD和FPGA在结构上有什么明显的区别?各有什么特点?

2.7FPGA器件中的存储器块有何作用?

2.8边界扫描技术有什么优点?

2.9说明JTAG接口有哪些功能

习题4

4.1用 Verilog 设计一个8位十进制加法器,进行综合和仿真。

module decimal_adder ( input [7:0] a, input [7:0] b, output reg [7:0] sum, output reg carry_out );

reg [7:0] temp_sum;

reg [3:0] tens;

always @(*) begin temp_sum = a + b; tens = temp_sum[7:4]; sum = {2'b00, temp_sum[3:0]}; if(tens>=5’d6)sum = sum + 8'd10;tens = tens - 5'd6; end carry_out = (tens > 4'd5);

end endmodule4.2用 verilog设计一个8位二进制加法计数器,带异步复位端口,进行综合和仿真。

module binary_counter (input clk,input rst_n, output reg [7:0] count

);always @(posedge clk or negedge rst_n) beginif (!rst_n) begincount <= 8'b0; end else begincount <= count + 1; end

endendmodule4.3用Verilog设计一个模60的 8421BCD 码计数器,进行综合和仿真。

module bcd_counter (input clk,input rst_n, output reg [7:0] count_bcd

);

reg [3:0] tens;

reg [3:0] units;

always @(posedge clk or negedge rst_n) beginif (!rst_n) begintens <= 4'b0000; units <= 4'b0000; end else beginif (units == 4'd9 && tens == 4'd5) begintens <= 4'b0000;units <= 4'b0000; end else if (units == 4'd9) begintens <= tens + 1; units <= 4'b0000; end else beginunits <= units + 1; endend

end

assign count_bcd = {tens, units};

endmodule

习题5

5.1下列标识符哪些是合法的、哪些是错误的?

Cout,8sum,\ a*b, data, \wait, initial, $latch

5.2下列数字的表示是否正确?

6'd18,'Bx0, 5'b0x110,'da30,10'd2.’hzF

5.3 reg型变量的初始值一般是什么?

5.4定义如下变量和常量:

1)定义一个名为count的整数;

2)定义一个名为ABUS的8位wire 总线;

3)定义一个名为address的16位reg型变量,并将该变量的值赋为十进制数128:

4)定义参数 Delay time,参数值为8;

5)定义一个名为 DELAY的时间变量;

6)定义一个容量为128位、字长为32位的存储器 MYMEM。

5.5在 Verilog的运算符中,哪些运算符的运算结果是一位的?

5.6能否对存储器进行位选择和域选择?

习题6

6.1用持续赋值语句描述一个4选1数据选择器。

module mux_4to1 (input [3:0] data_in, input [1:0] sel, output reg data_out

);

always @(*) begincase (sel)2'b00: data_out = data_in[0];2'b01: data_out = data_in[1];2'b10: data_out = data_in[2];2'b11: data_out = data_in[3];default: data_out = 1'bx; endcase

end

endmodule6.2用行为语句设计一个8位计数器,每次在时钟的上升沿,计数器加1,当计数器溢出时,自动从零开始重新计数,计数器有同步复位端。

module counter_8bit (input clk,input rst, output reg [7:0] count

);

always @(posedge clk) beginif (rst) begincount <= 8'b0; end else begincount <= count + 1;end

end

endmodule

6.3没计一个4位移位寄存器。

module shift_register_4bit (input clk,input rst, input load, input [3:0] data_in, input left_shift, output reg [3:0] q

);

always @(posedge clk) beginif (rst) beginq <= 4'b0000; end else if (load) beginq <= data_in; end else if (left_shift) beginq <= {q[2:0], q[3]}; end else beginq <= {q[0], q[3:1]}; end

end

endmodule6.4initial语句与always 语句的区别是什么?

6.5分别用任务和函数描述一个4选1多路选择器。

任务

module mux_4to1_task (input [3:0] data_in, // Four 1-bit inputsinput [1:0] sel, // 2-bit select signaloutput reg data_out // 1-bit output

);// Task definition

task select_data;input [3:0] din;input [1:0] s;output reg dout;

begincase (s)2'b00: dout = din[0];2'b01: dout = din[1];2'b10: dout = din[2];2'b11: dout = din[3];default: dout = 1'bx; // Undefined behavior for invalid selectionendcase

end

endtask

always @(sel or data_in) beginselect_data(data_in, sel, data_out);

end

endmodule

函数

module mux_4to1_function (input [3:0] data_in, input [1:0] sel, output reg data_out

);

function reg select_data;input [3:0] din;input [1:0] s;

begincase (s)2'b00: select_data = din[0];2'b01: select_data = din[1];2'b10: select_data = din[2];2'b11: select_data = din[3];default: select_data = 1'bx; endcase

end

endfunction

always @(sel or data_in) begindata_out = select_data(data_in, sel);

end

endmodule6.6 在Verilog中,哪些操作是并发执行的?哪些操作是顺序执行的?

6.7 试编写求补码的Verilog程序,输入是带符号的8位二进制数。

6.8试编写两个4位二进制数相减的 Verilog 程序。

module binary_subtractor (input [3:0] a, input [3:0] b, output reg [3:0] diff, output reg borrow

);reg [3:0] temp_diff;

reg [4:0] internal_borrow;always @(*) begininternal_borrow = {1'b1, ~b}; temp_diff = a + internal_borrow[3:0];diff = temp_diff[3:0];borrow = internal_borrow[4];

end

endmodule6.9 有一个比较电路,当输入的一位8421BCD码大于4时,输出为1,否则为0,试编写出 Veilog程序。

6.10用Veriog设计一个类似74138的译码器电路,对设计文件进行综合,观察综合视图。

module decoder_3to8 (input [2:0] addr, input en, output reg [7:0] y

);always @(*) beginif (en) beginy = 8'b11111111; end else begincase (addr)3'b000: y = 8'b00000001;3'b001: y = 8'b00000010;3'b010: y = 8'b00000100;3'b011: y = 8'b00001000;3'b100: y = 8'b00010000;3'b101: y = 8'b00100000;3'b110: y = 8'b01000000;3'b111: y = 8'b10000000;default: y = 8'b11111111; endcaseend

end

endmodule6.11 用Verilog设计一个8位加法器并进行综合和仿真。

习题7

7.1分别用结构描述和行为描述方式设计一个基本的D触发器。在此基础上,采用结构描述的方式用8个D触发器构成一个8位移位寄存器。

7.2 分别用结构描述和行为描述方式设计一个触发器,并进行综合。

module d_ff_behavioral (input clk,input rst, input d,output reg q

);

always @(posedge clk or posedge rst) beginif (rst) beginq <= 0; end else beginq <= d; end

end

endmodule7.3试编写同步模5计数器程序,有进位输出和异步复位端。

module mod5_counter (input clk,input rst_n, output reg [2:0] count,output reg carry_out

);always @(posedge clk or negedge rst_n) beginif (!rst_n) begincount <= 3'b000; carry_out <= 0;end else beginif (count == 3'b100) begin count <= 3'b000; carry_out <= 1; end else begincount <= count + 1; carry_out <= 0; endend

end

endmodule7.4分别编写4位串并转换程序和4位并串转换程序。

7.5 编写4位除法电路程序。

7.6 用 Verilog编写一个用7段数码管交替显示 26 个英文字母的程序,自己定义字符的形状。

7.7 用Verilog编写一个将带符号二进制数的8位原码转换成8位补码的电路,并基于Quartus Pime软件进行综合和仿真。

7.8编写一个8路彩灯控制程序,要求彩灯有以下3种演示花型。

1)8路彩灯同时亮灭;

2)从左至右逐个亮(每次只有1路亮);

3)8路彩灯每次4路灯亮,4路灯灭,且亮灭相间,交替亮灭。

习题8

8.1设计一个 111串行数据检测器。要求:当检测到连续3个或3个以上的1时,输出为1,其他输入诗深下输出为0。

module serial_detector_111 (input clk,input rst_n, input data_in,output reg detect_out

);

reg [2:0] shift_reg;

always @(posedge clk or negedge rst_n) beginif (!rst_n) beginshift_reg <= 3'b000; detect_out <= 0; end else beginshift_reg <= {shift_reg[1:0], data_in}; if (shift_reg == 3'b111) begindetect_out <= 1; end else begindetect_out <= 0; endend

end

endmodule

8.2设计一个1001串行数据检测器。其输入、输出如下。

输入x:000 101 010 010 011 101001 110101

输出z:000 000 000 010 010 000 001 000 000

module serial_detector_1001 (input clk,input rst_n, input data_in,output reg detect_out

);

reg [3:0] shift_reg;

always @(posedge clk or negedge rst_n) beginif (!rst_n) beginshift_reg <= 4'b0000; detect_out <= 0; end else beginshift_reg <= {shift_reg[2:0], data_in}; if (shift_reg == 4'b1001) begindetect_out <= 1; end else begindetect_out <= 0; endend

end

endmodule

8.3设计一个1101序列检测器。

module serial_detector_1101 (input clk,input rst_n, input data_in,output reg detect_out

);

reg [3:0] shift_reg;

always @(posedge clk or negedge rst_n) beginif (!rst_n) beginshift_reg <= 4'b0000; detect_out <= 0; end else beginshift_reg <= {shift_reg[2:0], data_in}; if (shift_reg == 4'b1101) begindetect_out <= 1; end else begindetect_out <= 0; endend

end

endmodule

8.4 编写一个8路彩灯控制程序,要求彩灯有以下3种演示花型:

1)8路彩灯同时亮灭。

2)从左至右逐个亮(每次只有1路亮)。

3)8路彩灯每次4路灯亮、4路灯灭且亮灭相间,交替亮灭,

在演示过程中,仅在一种花型演示完毕时才转向其他演示花型。

8.5用状态机设计交通灯控制器,设计要求:A路和B路中每路都有红、黄、绿3种灯,持续时间为:红灯 45 s,黄灯5s,绿灯 40s。A 路和 B路灯的状态转换是:

1)A红,B绿(持续时间40s)。

2)A红,B黄(持续时间5s)。

3)A绿,B红(持续时间 40s)。

module traffic_light_controller (input clk, input rst_n, output reg [2:0] A_lights, output reg [2:0] B_lights

);

typedef enum reg [1:0] {STATE_AB_GREEN_RED,STATE_AB_YELLOW_RED,STATE_BA_GREEN_RED

} state_t;

state_t current_state, next_state;

always @(posedge clk or negedge rst_n) beginif (!rst_n) begincurrent_state <= STATE_AB_GREEN_RED;end else begincurrent_state <= next_state;end

end

always @(*) begincase (current_state)STATE_AB_GREEN_RED: beginA_lights = 3'b100; B_lights = 3'b001; if ($time % 500 == 400) begin next_state = STATE_AB_YELLOW_RED;end else beginnext_state = STATE_AB_GREEN_RED;endendSTATE_AB_YELLOW_RED: beginA_lights = 3'b010; B_lights = 3'b001; if ($time % 500 == 450) begin next_state = STATE_BA_GREEN_RED;end else beginnext_state = STATE_AB_YELLOW_RED;endendSTATE_BA_GREEN_RED: beginA_lights = 3'b001; B_lights = 3'b100; if ($time % 500 == 400) begin next_state = STATE_AB_GREEN_RED;end else beginnext_state = STATE_BA_GREEN_RED;endenddefault: beginA_lights = 3'b001; B_lights = 3'b001; next_state = STATE_AB_GREEN_RED;endendcase

end

endmodule习 题10

10.1塞赋值与非阻塞赋值有什么本质的区别?在使用中应注意哪些方面?结合自己的设计实践

10.2流水线设计技术为什么能提高数字系统的工作频率?

10.3设计一个加法器,实现sum=a0+a1+a2+a3,a0、a1、a2、a3 宽度都是8位。如果用下面两科方法实现,哪种方法更好一些?

l)sum=((a0+al)+a2)+a3

2) sum =(a0+al)+ (a2+a3)

10.4用流水线技术对习题103中的sum=((a0+al)+a2)+a3的实现方式进行优化,对比其最高工作

10.5在FPGA设计开发中,还有哪些方法可提高设计性能?

习题 11

11.1 写出1位全加器本位和(SUM)的UDP描述

11.2写出4选1多路选择器的 UDP描述。

11.3`timescale 指令的作用是什么?举例说明

11.4编写一个4位的比较器,并对其进行测试

module comparator_4bit (input [3:0] a,input [3:0] b,output reg eq, output reg gt, output reg lt

);

always @(*) beginif (a == b) begineq = 1;gt = 0;lt = 0;end else if (a > b) begineq = 0;gt = 1;lt = 0;end else begineq = 0;gt = 0;lt = 1;end

end

endmodule11.5 编写一个时钟波形产生器,产生正脉冲宽度为15ns、负脉冲宽度为10ns的时钟

module clock_generator (input clk, input rst_n, output reg custom_clk

);

typedef enum reg [1:0] {STATE_HIGH,STATE_LOW

} state_t;

state_t current_state, next_state;

reg [3:0] counter;

always @(posedge clk or negedge rst_n) beginif (!rst_n) begincurrent_state <= STATE_HIGH;counter <= 0;custom_clk <= 1;end else begincurrent_state <= next_state;case (current_state)STATE_HIGH: beginif (counter < 15) begincounter <= counter + 1;custom_clk <= 1;end else begincounter <= 0;custom_clk <= 0;next_state <= STATE_LOW;endendSTATE_LOW: beginif (counter < 10) begincounter <= counter + 1;custom_clk <= 0;end else begincounter <= 0;custom_clk <= 1;next_state <= STATE_HIGH;endenddefault: begincounter <= 0;custom_clk <= 1;next_state <= STATE_HIGH;endendcaseend

end

endmodule11.6 编写一个测试程序,对D触发器的逻辑功能进行测试。

补充

- 试用 Verilog HDL描述一个带进位输入、输出的8位全加器。端口:A、B为加数,CI为进位输入,S为和,CO为进位输出

- 2设计一个4位4输入最大数值检测电路,其中,a、b、c和d为4位二进制数,输出为max。

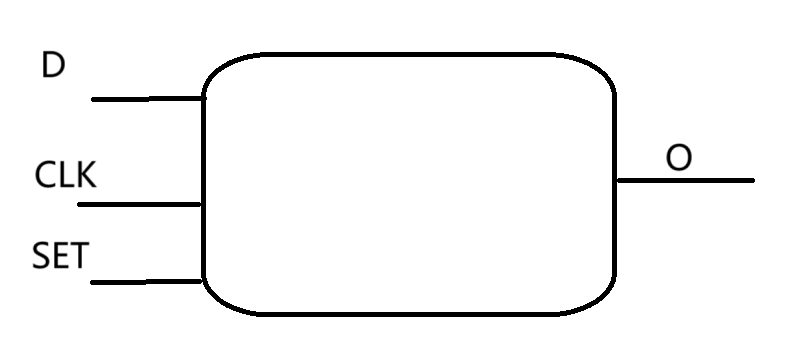

- 编写一个带异步清零、异步置位的 D 触发器。端口: CLK 为时钟,D为输入,CLK为清零输入端,SET为置位输入端; O输出端。

- 设计一个带有异步复位控制端和时钟使能控制端的 10进制计数器。端口设定如下:输入端口:CLK:时钟,RST:复位端,EN:时钟使能端、LOAD:置位控制端,DIN:置位数据端;输出端口:COUT:进位输出端,DOUT计数输出端

- 编写一个4位加法计数器VHDL程序的进程(不必写整个结构框架),要求复位信号reset低电平时计数器清零,变高后,在上升沿开始工作;输入时钟信号为ck,输出为

- 填写完成一个8-3线编码器的真值表(5分),并写出其verilog程序

- 用IF语句编写一个四选一电路,要求输入d0~d3,s为选择端,输出y

- 现有输入信号是一个占空比位50%的方波,用VHDL设计一个时钟的5分频电路,输出为占空比位20%,写出VHDL代码。

- 现有输入信号是一个占空比位50%的方波,用VHDL设计一个时钟的5分频电路,输出为占空比位50%,写出VHDL代码

- 试用 verilog 语言描述:图示为一个4位移位寄存器,是由四个 D 触发器(分别设为 U1、U2、 U3、 U4)构成的。其中 seri in 是这个移位寄存器的串行输入;clk 为移位时脉冲输入;cr为清零控制信号输入;Q[1]~Q[3]则为移位寄存器的并行输出。

- 设计一个带复位端且对输入时钟 clk 进行二分频模块,并画出仿真波形。

- 设计一带异步复位端、异步置数段(低电平有效)的四位加法计数器,时钟clk上升沿有效),复位信号 clr,置数信号 load、输入数据 data、输出 qout。并画出仿真波形。

- 试设计一个 3/8 译码器,规定模块定义为 module Decoder(Out.In.En),其中Out为译码器输出,In为译码器输入,En为译码使能输入。要求:写出3/8 译码器 Verilog HDL设计程序并注释;