微机原理与接口技术,期末冲刺复习资料(四)

接续上文:微机原理与接口技术,期末冲刺复习资料(三)-CSDN博客

点关注不迷路哟。你的点赞、收藏,一键三连,是我持续更新的动力哟!!!

持续关注我~~~主页,查看更多内容哟(希望你能在这里有所收获🤭)。点关注,不迷路,哈哈哈!~~~

主页:一位搞嵌入式的 genius-CSDN博客![]() https://blog.csdn.net/m0_73589512?spm=1000.2115.3001.5343

https://blog.csdn.net/m0_73589512?spm=1000.2115.3001.5343

目录

接续上文:微机原理与接口技术,期末冲刺复习资料(三)-CSDN博客

点关注不迷路哟。你的点赞、收藏,一键三连,是我持续更新的动力哟!!!

5. 半导体存储器

5.1 概述

5.1.1 存储器系统

5.1.2 半导体存储器

5.1.3 主要技术指标

5.2 随机存取存储器

5.2.1 静态存储器(SRAM)

5.2.2 动态随机存储器DRAM

5.3 只读存储器(ROM)

5.3.1 EPROM

5.3.2 EEPROM

5.3.2.1 闪速存储器Flash

5.4 存储器扩展技术(内存储器设计)

5.5 高速缓存(了解)

5.5.1 Cache 的基本概念

5.5.2 设置 Cache 的理由

5.5. 3 程序的局部性原理

5.5.4 Cache 的工作原理

5.5. 5 Cache 的命中率与平均存取速度

5.5.6 Cache 的读写策略

1. 读操作策略

2. 写操作策略

5.5.7 Cache 的分级体系结构

1. 一级缓存(L1 Cache)

2. 二级缓存(L2 Cache)

3. 三级缓存(L3 Cache)(部分高性能处理器中有)

5.6 主要掌握知识点

5. 半导体存储器

主要内容:

-

存储器系统

-

半导体存储器的分类及其特点

-

半导体存储芯片的外部特性及其与系统的连接

-

存储器接口设计(存储器扩展技术)

-

高速缓存

5.1 概述

主要内容: 存储器系统 半导体存储器的分类及特点 两类半导体存储器的主要区别

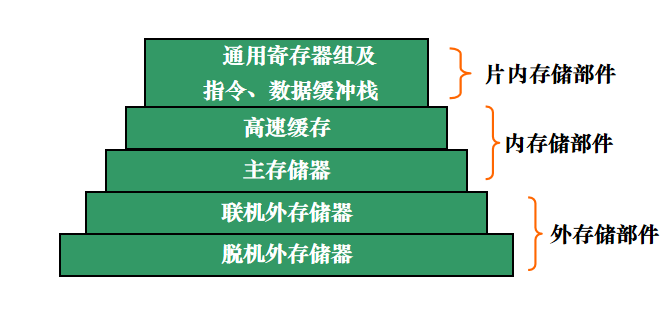

5.1.1 存储器系统

微型机中的存储器总体上包括:内存和外存

二者在速度、容量、材料等有所差别

| 内 存 | 外 存 | |

|---|---|---|

| 速度 | 快 | 慢 |

| 容量 | 小 | 大 |

| 单位容量价格 | 高 | 低 |

| 制造材料 | 半导体 | 磁性材料 |

存储器分类:

-

内存:主存、高速缓冲存储器

-

外存:联机外存、脱机外存

-

虚拟存储器

具体内容:

-

微型计算机中的存储系统主要有:

-

Cache存储器系统

-

虚拟存储器系统

-

-

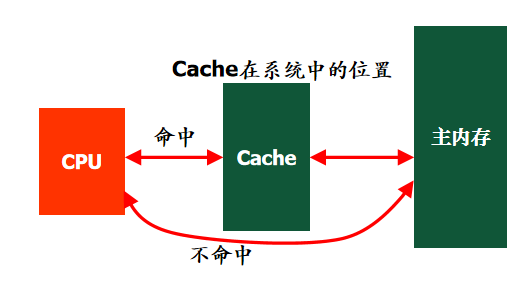

Cache存储器系统:

由高速缓冲存储器(Cache)和主内存一起构成,来管理硬件系统

设计目标:提高CPU访问内存的存取速度

Cache:

-

虚拟存储系统:

主内存和部分硬磁盘构成,由操作系统管理:

设计目标:扩大存储容量

-

系统存取时间= 命中率Cache存取时间+不命中率主存存取时间

T=HT1+(1-H)T2

-

主要性能指标:

-

存储容量(S)

-

存取时间(T)(与系统命中率有关)

-

命中率(H)

-

T=HT1+(1-H)T2

-

-

单位容量价格(C)

-

访问效率(e)

-

5.1.2 半导体存储器

若干存储元(能存放1位二进制数的半导体器件)构成1个存储单元

-

分类:

内存:

-

随机存储器(RAM):

-

静态存储器(SRAM)

-

动态存储器(DRAM)

-

同步动态随机存取内存器(SDRAM)

-

-

只读存储器(ROM):

-

EPROM

-

EEPROM

-

一次性可写ROM

-

掩模ROM(只有这个是不可以写入的)

-

-

-

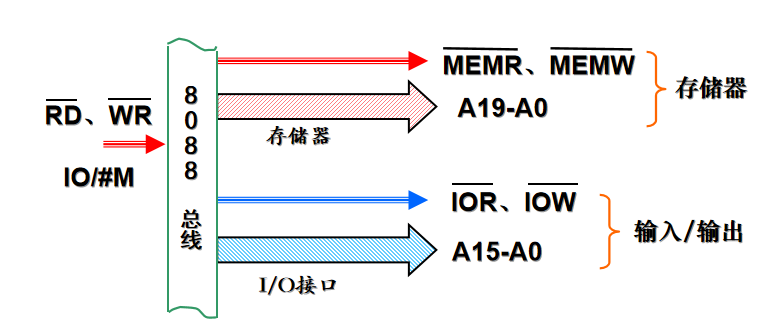

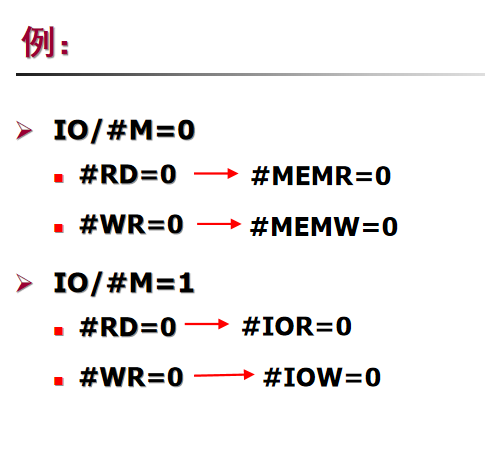

8088总线信号

5.1.3 主要技术指标

存储容量 存储单元个数×每单元的二进制数位数 存取时间 实现一次读/写所需要的时间 存取周期 连续启动两次独立的存储器操作所需间隔的最小时间 可靠性 功耗

5.2 随机存取存储器

掌握:

-

SRAM和DRAM的特点

-

集中常用存储芯片与系统的连接

-

存储器扩展技术

特点:

可以随机读或写操作 掉电后存储内容即丢失

类型:

-

静态存储器(SRAM)

-

动态存储器(DRAM)

5.2.1 静态存储器(SRAM)

特点:由双稳电路构成,存储信息稳定

典型SRAM芯片:

-

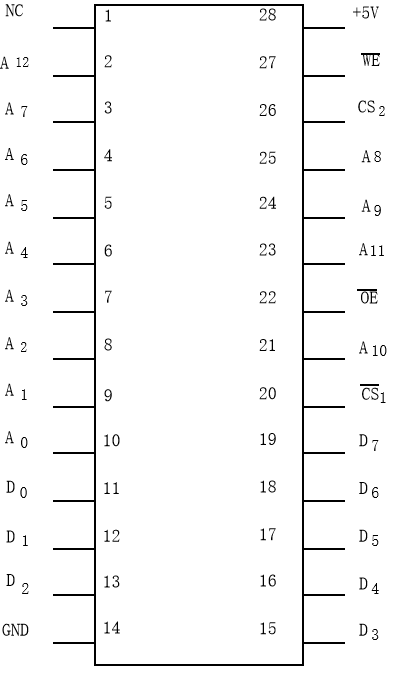

SRAM6264

容量:8K * 8b = 8K * 1B

主要引线(28根):

-

地址线:A0------A12;

-

数据线:D0------D7;

-

输出允许信号:OE;

-

写允许信号:WE;

-

片选信号:CS1,CS2。同时满足条件,才能让芯片工作。

-

-

工作过程

-

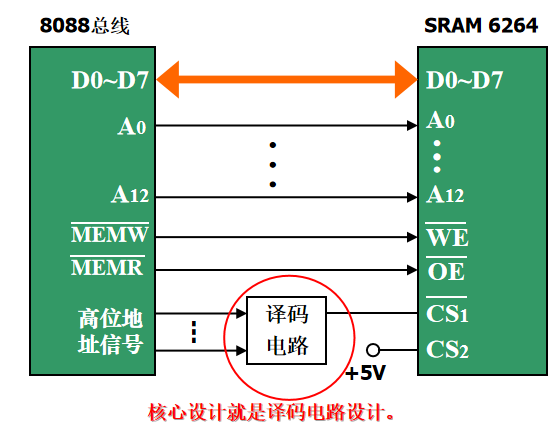

6264芯片与系统连接

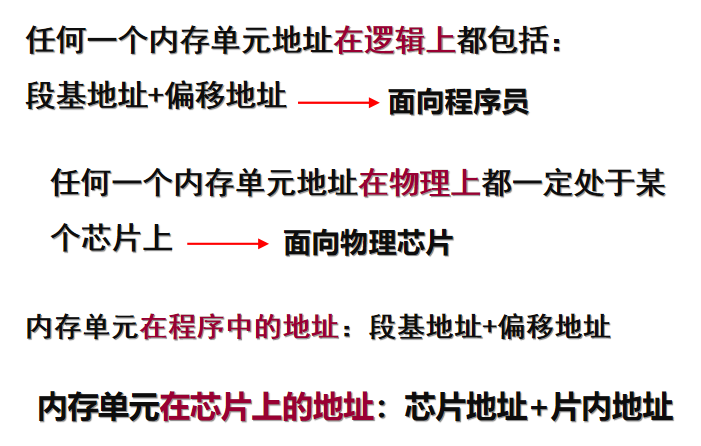

存储器芯片与系统的连接分为两部分: 确定要访问的存储芯片 系统中可能存在多片存储器芯片,要访问的单元只能存在于某一片芯片上。 找到芯片后,寻找该芯片上要访问的单元。 6264芯片上有8K个单元,每个单元在该芯片上有惟一的13位地址码。 每片6264芯片上第一个单元在该芯片上的地址:0 每片6264芯片上最后一个单元在该芯片上的地址:8191

用芯片的13位地址码A0-A12寻址片内的每个单元

-

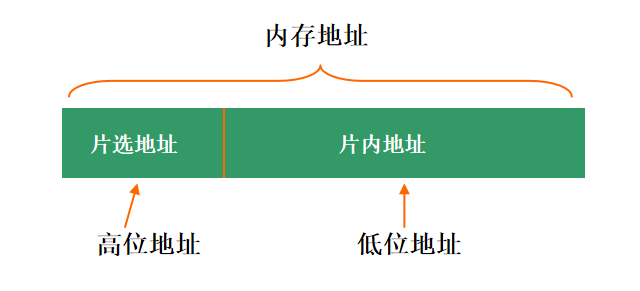

存储器地址

-

6264与系统的连接框架图

-

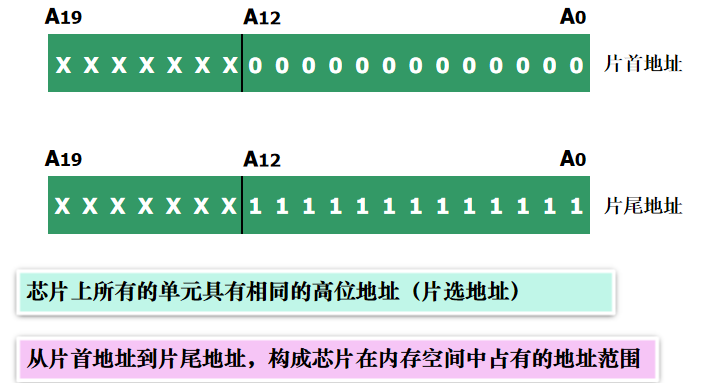

6264芯片的编址

-

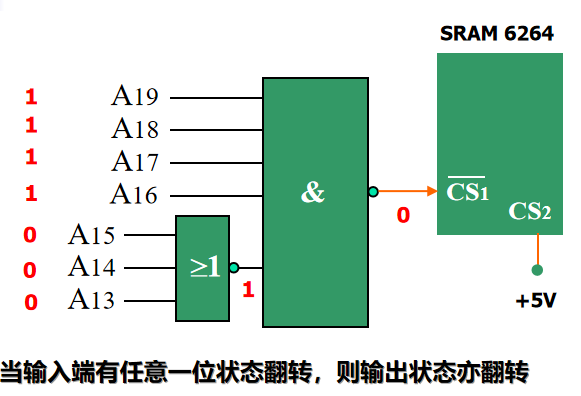

译码电路

将输入的高位地址信号变换成一个有效输出信号,来选择某个存储器芯片,来确定该存储器芯片在内存中的地址范围

译码方式:

-

全地址译码:

用全部的高位地址信号作为译码信号,使得存储器芯片的每一个单元都占据一个唯一的内存地址。

它保证了该芯片在整个空间中具有唯一的地址范围。

好处:任何地址资源

不足:用到的地址“资源”多导致了电路复杂

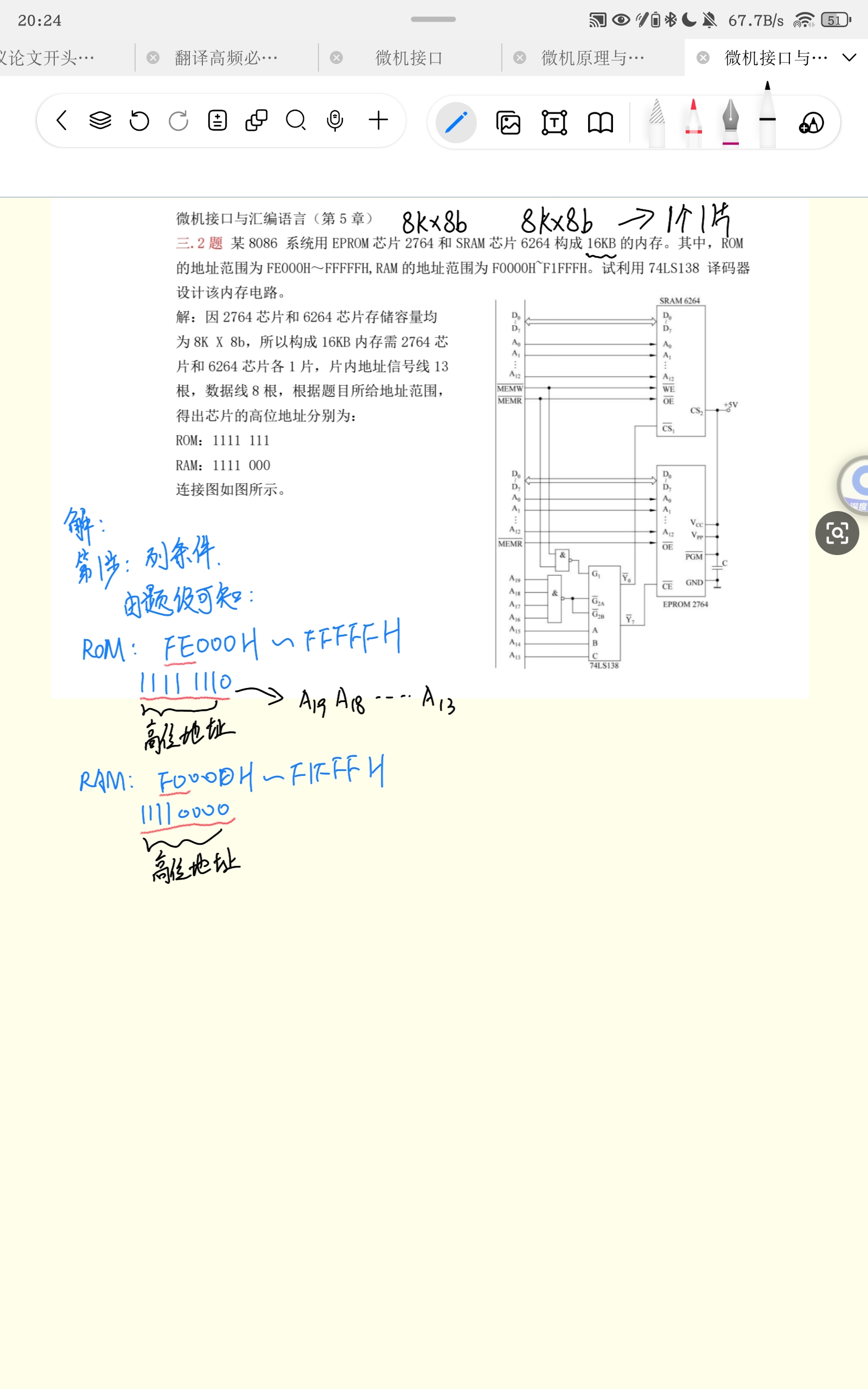

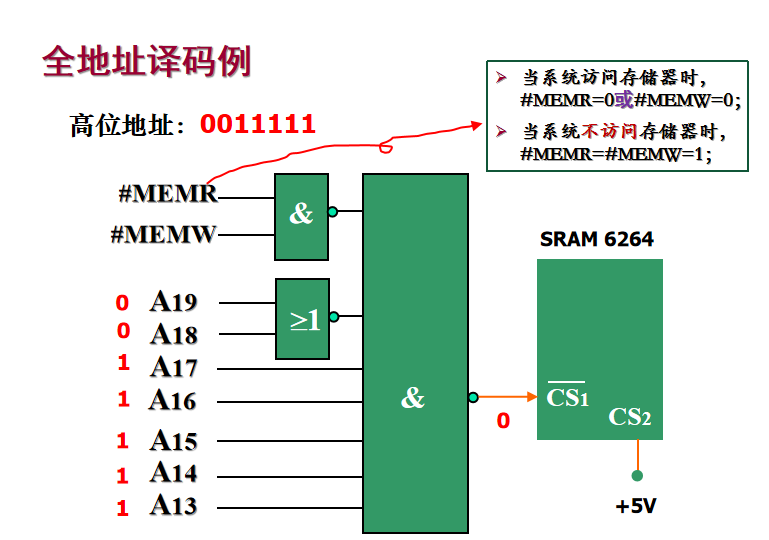

全地址译码实例:

大于等于1表示的就是或运算

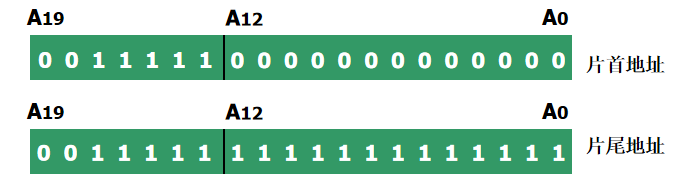

例: 已知某SRAM 6264芯片在内存中的地址为:3E000H~3FFFFH。试画出将该芯片连接到系统的译码电路。 设计步骤: 写出地址范围的二进制表示; 确定各高位地址状态; 设计译码器。

高位地址:0011111

-

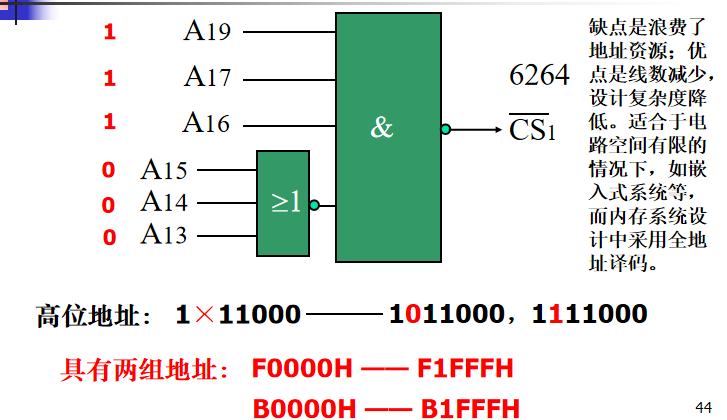

部分地址译码

用部分高位地址信号(而不是全部)作为译码 信号,使得被选中存储器芯片占有几组不同 的地址范围。

如下图所示:

[解释上图] 分析图片内容可知:缺少A18线,所以就存在两个地址,分别为0或1的时候对应的段尾地址

-

例题:

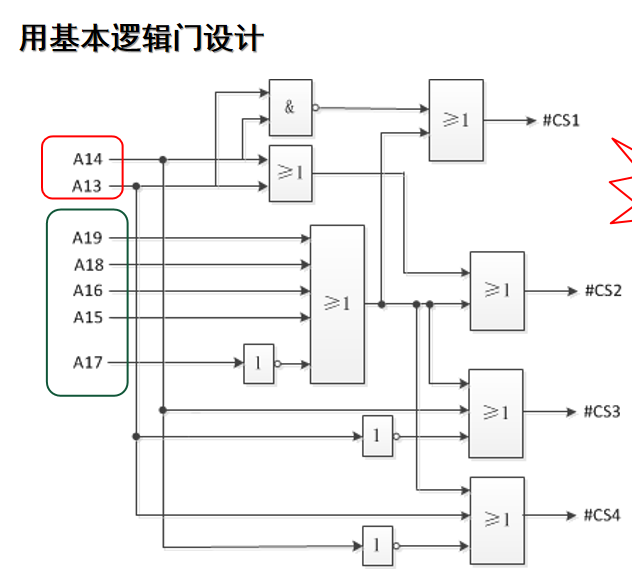

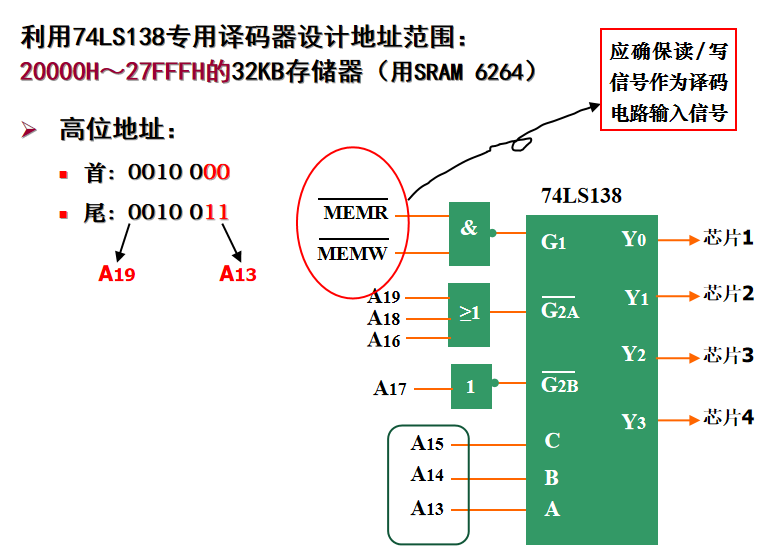

用SRAM 6264芯片构成容量为32KB的存储器。要求存储器的地址范围为: 20000H~27FFFH

解答:

因为6264芯片大小为:8K * 1B,又因为存储器容量为32KB,所以需要4片6264芯片。

采用基本逻辑门电路设计:

-

-

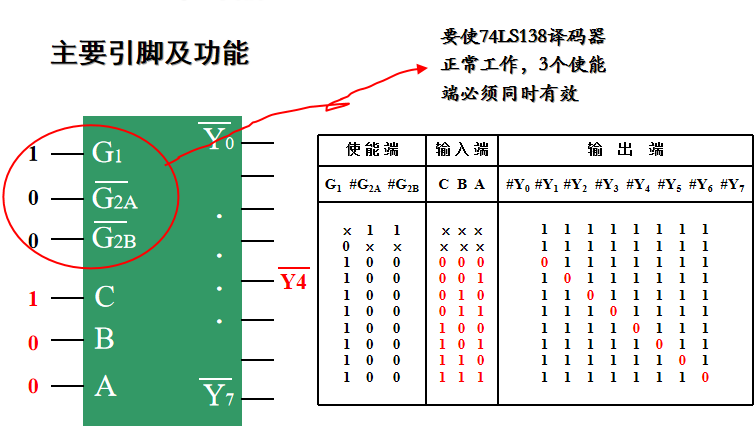

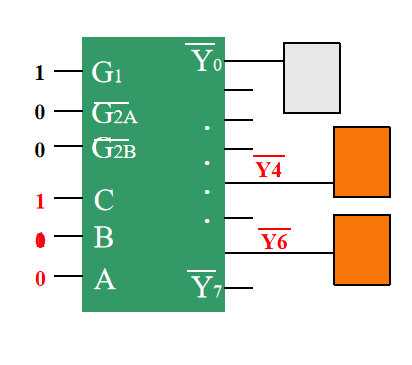

74LS138译码器

图中红圈的3个引脚均有效的时候,才能使得74LS138工作

-

译码器主要功能: 根据输入的不同编码组合,确保其控制的各电路(芯片)在任一时刻只有一路(1个芯片)处于工作状态。

输出控制的某个Yx非。

-

例如:

-

小结

当仅需要将一片存储器芯片连接到系统中时,只需要简单的译码电路。 根据设定地址确定电路设计,由基本逻辑门实现 此时高位地址为一个确定值 当系统中的存储器由多片存储器芯片构成时:

此时高位地址为一个地址范围

为简化设计,可借助专用译码器

5.2.2 动态随机存储器DRAM

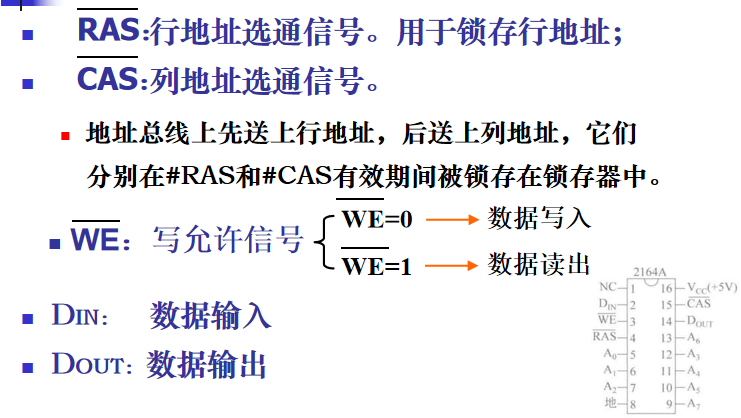

特点:电容组成存储元,需要定时刷新

典型DRAM芯片:

2164A

大小:64K×1bit

以256×256的矩阵形式排列 采用行地址和列地址来确定一个单元;

行列地址分时传送,共用一组地址信号线; 地址信号线的数量仅为同等容量SRAM芯片的一半。

-

主要引线:

地址总线上:先送行,后送列地址。

-

工作原理:

数据读出 数据写入 刷新:将存放于每位中的信息重新读出来后,又写入原位置中

-

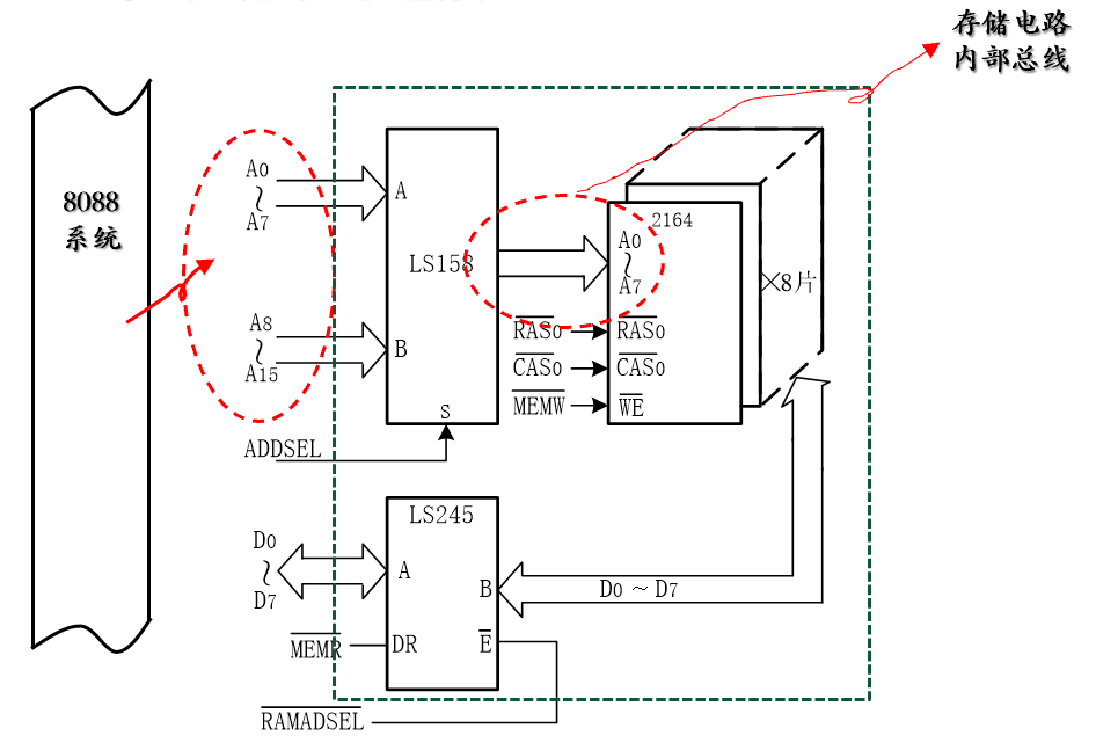

2164A在系统中的连接

DRAM 2164A与系统连接的几点说明: 芯片上的每个单元中只存放1位二进制码,每字节数据分别存放在8片芯片中; 系统的每一次访存操作需同时访问8片2164A芯片,该8片芯片必须具有完全相同的地址; 芯片的地址选择是按行、列分时传送,由系统的低8位送出行地址,高8位送出列地址。 结论: 每8片2164A构成一个存储体(单独一片则无意义); 每个存储体内的所有芯片具有相同的地址(片内地址),应同时被选中,仅有数据信号由各片分别引出。

5.3 只读存储器(ROM)

EPROM(紫外线擦除)、EEPROM(电擦除)、Flash

5.3.1 EPROM

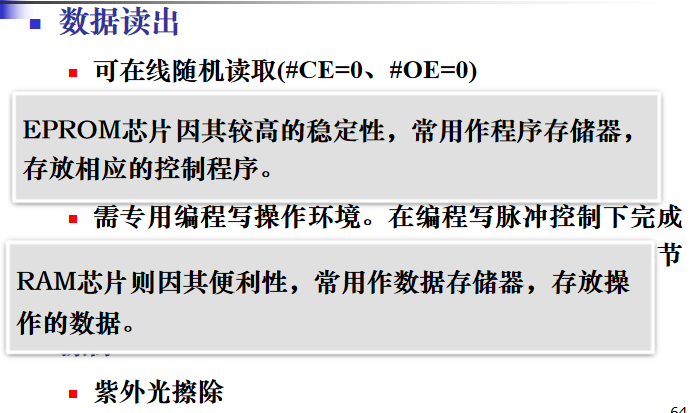

特点:可多次编程写入;掉点后内容不丢失;内容擦除需要“紫外线”

典型芯片:EPROM 2764

8K×8bit芯片 地址信号:A0 —— A12 数据信号:D0 —— D7 输出信号:OE非 片选信号:CE非 编程脉冲输入:PGM非 其引脚与SRAM 6264完全兼容.

2764的工作方式

EPROM 2764的应用

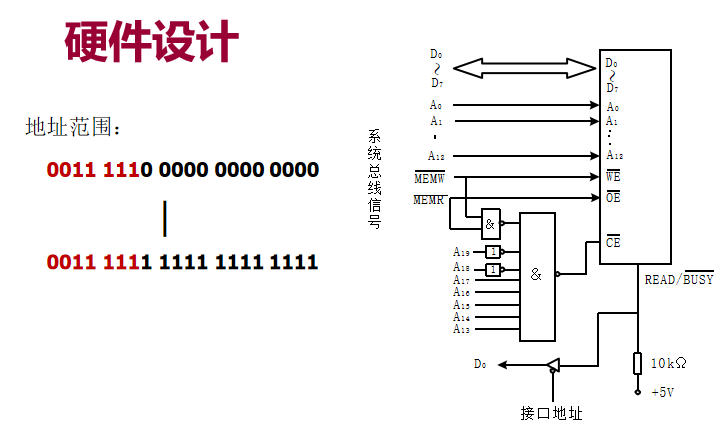

5.3.2 EEPROM

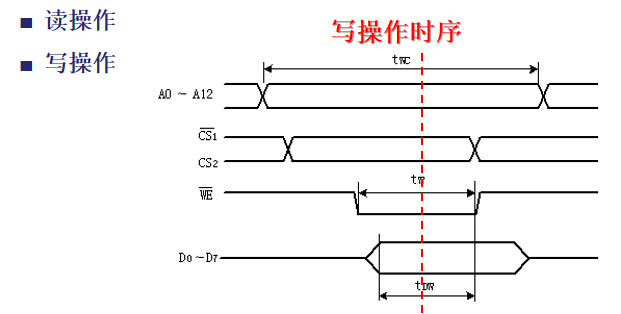

特点:可在线编程写入;掉点后内容不丢失;电擦除

工作方式:

-

数据读出:(#CE=0、#OE=0、#WE=1)

-

编程写入:

-

字节写入:每一次BUSY正脉冲写入1B

-

自动页写入:每一次BUSY正脉冲写入 32B

-

-

擦除:

-

字节擦除:一次擦除一个字节(写入FFH)

-

片擦除:一次擦除整片(保持10ms)

-

典型芯片: EEPROM 98C64

8K×8bit芯片; 13根地址线(A0 —— A12); 8位数据线(D0 —— D7); 输出允许信号(OE); 写允许信号(WE); 选片信号(CE); 状态输出端(READY / BUSY)。

EEPROM 的应用

可通过程序实现对芯片的读写; 仅当READY / BUSY=1时才能进行“写”操作 “写”操作的方法: ① 根据参数定时(延时)写入。100微秒为均值,一般120%。 ② 通过判断(查询)READY / BUSY端的状态进行写入 仅当该端为高电平时才可写入下一个字节。 ③ 中断控制方式 当READY / BUSY端为高电平时,该高电平可作为中断请求信号

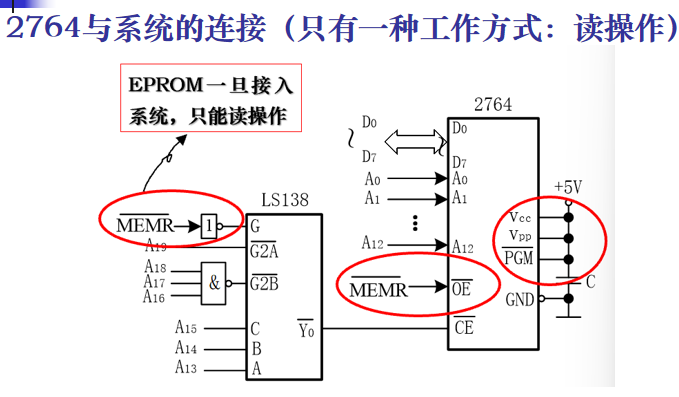

例题:

将一片98C64A接到系统总线上,使其地址范围在3E000H~ 3FFFFH之间。并编程序将芯片的所有存储单元写入66H。

硬件设计:

软件设计:

定时方式进行写入:

START:MOV AX,3E00H MOV DS,AX

MOV SI,0000H

MOV CX,8192 AGAIN:MOV AL,66H MOV [SI],AL CALL TDELAY INC SI LOOP AGAIN HLT

5.3.2.1 闪速存储器Flash

特点:属于EEPROM类型芯片

-

通过写入命令的方式来控制芯片的工作方式

-

通过读状态寄存器的值,获取芯片的当前工作状态

-

与SRAM的区别:

-

在进行写入和擦除的时候需要12V编程电压

-

-

与普通的EEPROM相比的区别:

-

通过读状态寄存器的内容确定是否可以继续写入

-

提高命令字的方式控制芯片处于何种工作模式

-

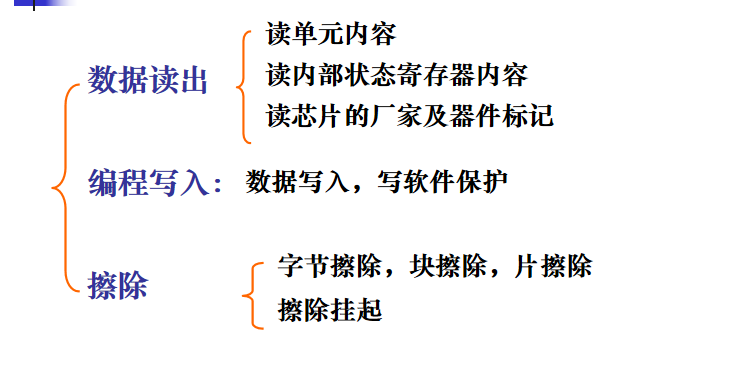

工作方式:

5.4 存储器扩展技术(内存储器设计)

存储器扩展:

-

多片存储芯片拼在一起构成一个我们要求的内存空间。

-

各存储芯片在整个内存中占据不同地址范围。

-

任一时刻仅有1片(或1组)被选中

-

存储器芯片的存储容量等于: 单元数(字节数)×每单元的位数(字长)

存储器扩展方法:

-

位扩展:扩展字长

-

字扩展:扩展单元数

-

字位扩展:既扩展字长又扩展单元数

解释:

-

位扩展:每单元字长的扩展

实例:

DRAM 2164A: 64K×1bit

采用行地址和列地址来确定一 个单元; 行列地址分时传送,共用一组 地址信号线; 地址信号线的数量仅为同等容量 SRAM芯片的一半。

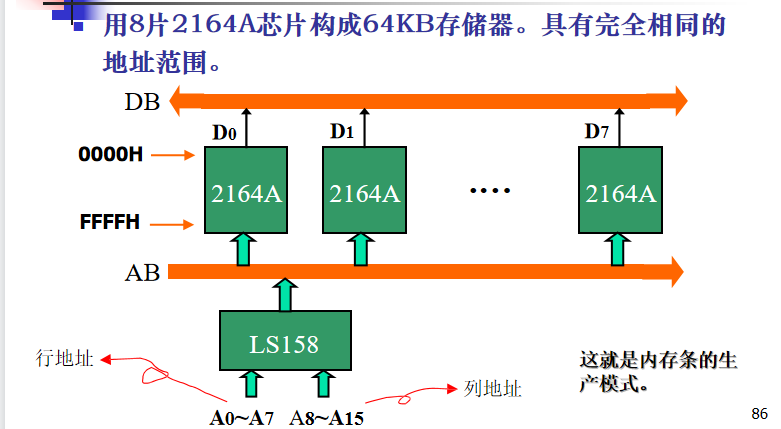

使用:8片2164A构成64KB存储体

这里的8片2164A必须具有完全相同的地址,必须同时被选中或同时不被选中

方法:

位扩展的连线特点: 将每片的地址线、控制线并联,数据线分别引出。 效果: 存储器的单元数不变,位数增加。

注意:确保所有芯片具有完全相同的地址范围。

-

字扩展:

芯片中每个单元的字长满足,但单元数不满足

原则:

-

每个芯片的地址线、数据线、控制线并联

-

片选端分别引出,使得每个芯片有不同的地址范围。

注意:确保所有芯片具有完全不同的地址范围

例题:

用SRAM 6264(8K*8bit)芯片构成容量为32KB的存储器

存储器的地址范围为: 20000H~27FFFH 设计:

由地址范围得: 需4片6264芯片 存储器地址范围: 00100000000000000000~00100111111111111111

-

-

字位扩展:

单元数及每单元字长均不满足要求

设计过程: 根据内存容量及芯片容量确定所需存储芯片数; 进行位扩展以满足字长要求; 进行字扩展以满足容量要求。 若已有存储芯片的容量为L×K,要构成容量为M ×N的存储器,需要的芯片数为: (M / L) ×(N / K)

例题:

首先进行位扩展: 用8片芯片构成32KB存储体 利用A0~A14寻址存储体内32K个单元 所有控制信号线和地址信号线并联引出 再进行字扩展: 用8个32KB存储体构成256KB存储器 寻址8个存储体,至少需要3位高位地址信号

-

5.5 高速缓存(了解)

5.5.1 Cache 的基本概念

Cache(高速缓存)是一种位于 CPU 与主存(RAM)之间的高速存储器,专门用来缓解两者之间访问速度差异的问题。它保存了CPU 最近访问或即将访问的数据块,以减少访问主存的次数,从而提高系统整体性能。

5.5.2 设置 Cache 的理由

-

CPU 与主存速度差距大

-

当前 CPU 的处理速度远高于内存访问速度,若每次都访问主存,将极大浪费 CPU 运算能力。

-

-

高速存储器价格昂贵

-

将高速存储器设置为主存会极大提高成本,因此采用容量小、速度快的 Cache 是权衡成本与性能的优化方案。

-

5.5. 3 程序的局部性原理

Cache 的设置基于程序执行时的局部性原理,分为以下两种类型:

-

时间局部性(Temporal Locality)

-

最近访问的数据项可能在不久的将来被再次访问。

-

如循环体内变量、多次调用的函数等。

-

-

空间局部性(Spatial Locality)

-

被访问的数据项,其邻近地址的数据很可能在短时间内也会被访问。

-

如数组访问、顺序执行指令等。

-

5.5.4 Cache 的工作原理

-

主存与 Cache 区划分

-

主存与 Cache 被划分为固定大小的块(Block),如每块 64 字节;

-

块与块之间存在映射关系。

-

-

访问流程

-

当 CPU 请求某地址的数据时,优先查询 Cache;

-

若 Cache 中命中(Hit),直接返回;

-

若 未命中(Miss),则访问主存并将对应数据块调入 Cache;

-

如果 Cache 满了,则按某种替换策略(如 LRU、FIFO)淘汰某一块,腾出空间。

-

-

地址映射方式

-

直接映射(Direct Mapping)

-

全相联映射(Fully Associative Mapping)

-

组相联映射(Set-Associative Mapping)

-

5.5. 5 Cache 的命中率与平均存取速度

-

命中率(Hit Ratio):CPU 所有访问中,访问命中的 Cache 次数所占比例。

命中率命中次数总访问次数

-

平均存取时间(T_avg):

命中率主存命中率

其中,

-

TCache:Cache 存取时间

-

T主存:主存(RAM)存取时间

-

-

Cache与主存容量比:

-

通常为 1 : 128(即主存是 Cache 的 128 倍)

-

5.5.6 Cache 的读写策略

Cache 的读写策略会直接影响数据一致性和性能,常见策略包括:

1. 读操作策略

-

贯穿读出式(Look-through Read) CPU 读数据时先访问 Cache,若未命中则继续访问主存。

-

旁路读出式(Look-aside Read) CPU 并行查询 Cache 和主存,哪个先返回就使用哪个。

2. 写操作策略

-

写穿式(Write-through) 数据同时写入 Cache 和主存,保持一致性,但写入速度慢。

-

回写式(Write-back) 仅写入 Cache,延迟写入主存,只有当该块被替换时才更新主存,效率高但一致性较难维护。

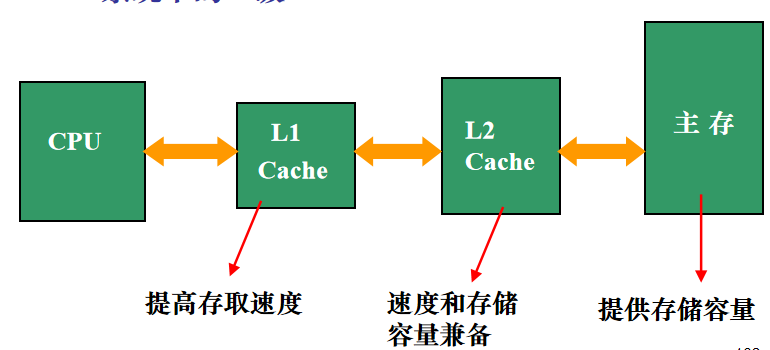

5.5.7 Cache 的分级体系结构

为了进一步提升访问速度与系统性能,现代计算机通常设置多级 Cache。

1. 一级缓存(L1 Cache)

-

位于 CPU 内部,直接与运算核心相连;

-

访问速度最快,但容量较小(如 32KB~128KB);

-

通常分为指令缓存(L1I)*和*数据缓存(L1D)。

2. 二级缓存(L2 Cache)

-

可位于 CPU 内部或外部,容量较 L1 大(如 256KB~1MB);

-

比 L1 慢但比主存快;

-

作为 L1 的后备缓存。

3. 三级缓存(L3 Cache)(部分高性能处理器中有)

-

共享于多个内核之间;

-

容量较大(数 MB 到几十 MB),速度低于 L2;

-

提高多核协同效率。

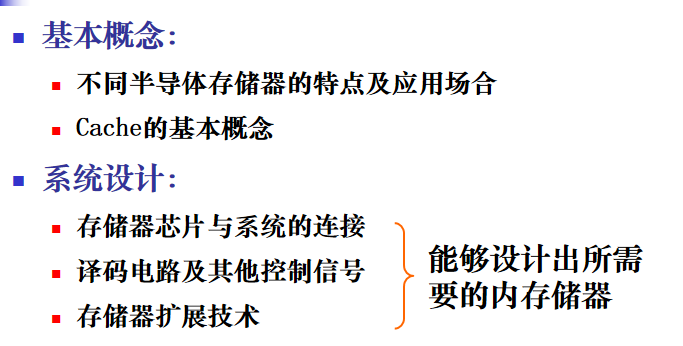

5.6 主要掌握知识点

译码电路设计 半导体存储器系统设计 SRAM存储器系统设计 EPROM和EEPROM与系统的连接及其读操作或读、写操作。

注意:

5.7 重点题型