Verilog状态机异常跳转解析

verilog状态机问题记录

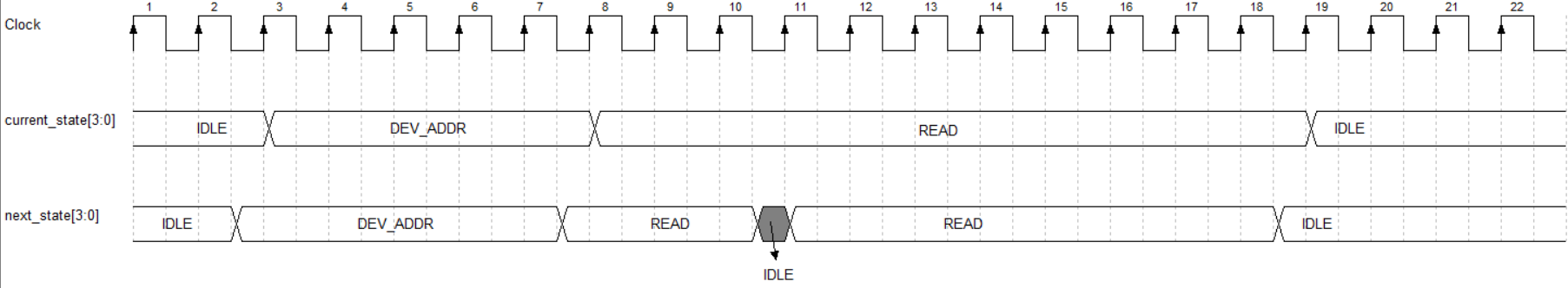

在使用verilog硬件描述语言时,写三段式状态机,使用current_state[3:0]、next_state[3:0]时,current_state正常跳转,next_state跳转异常,存在半周期的异常状态,然后回到正常状态。这种情况为正常代码,无需修改。

举例说明:

parameter IDLE=4'h0;

parameter READ=4'h1;

parameter DEV_ADDR=4'h2;

parameter WRITE=4'h3;

异常状态跳转见下图

next_state中有半个周期的异常状态跳转,IDLE。

这种状态跳转为正常情况,理由:

1、其他控制信号都是根据current_state生成;

2、current_state只在clock上升沿来源于next_state,current_state正常跳转;

综上所述,此种为正常代码,无需修改