DisplayPort 2.0协议介绍(1)

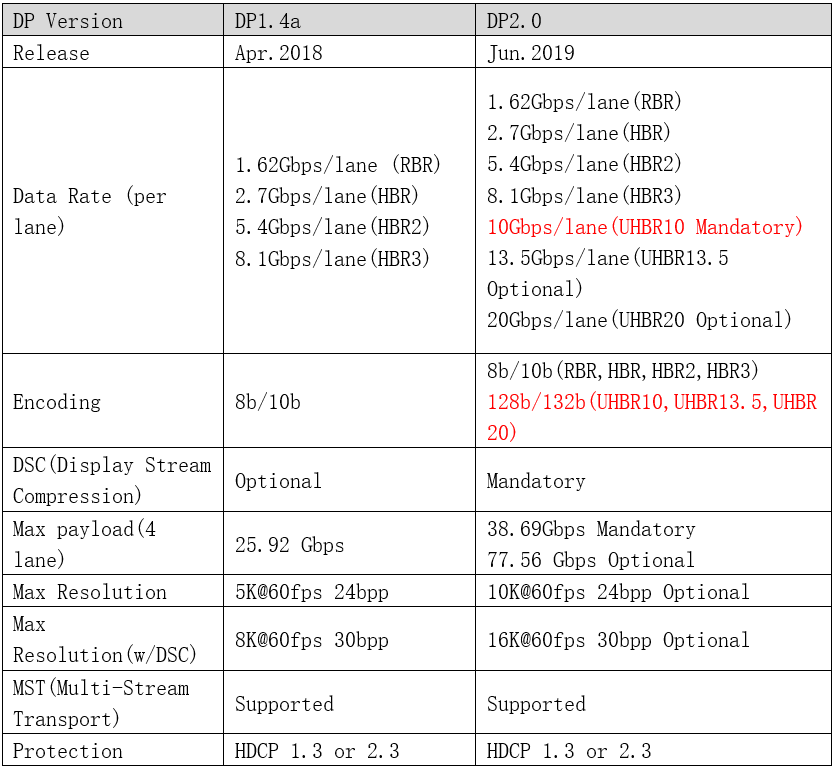

最近开始学习DisplayPort 2.0协议,相比于DP1.4a,最主要的是速率提升到了10Gbps/lane,还有就是128b/132b编码方式的修改。至于速率13.5Gbps和20Gbps还只是可选项,在DP2.1协议才成为必须支持选项。

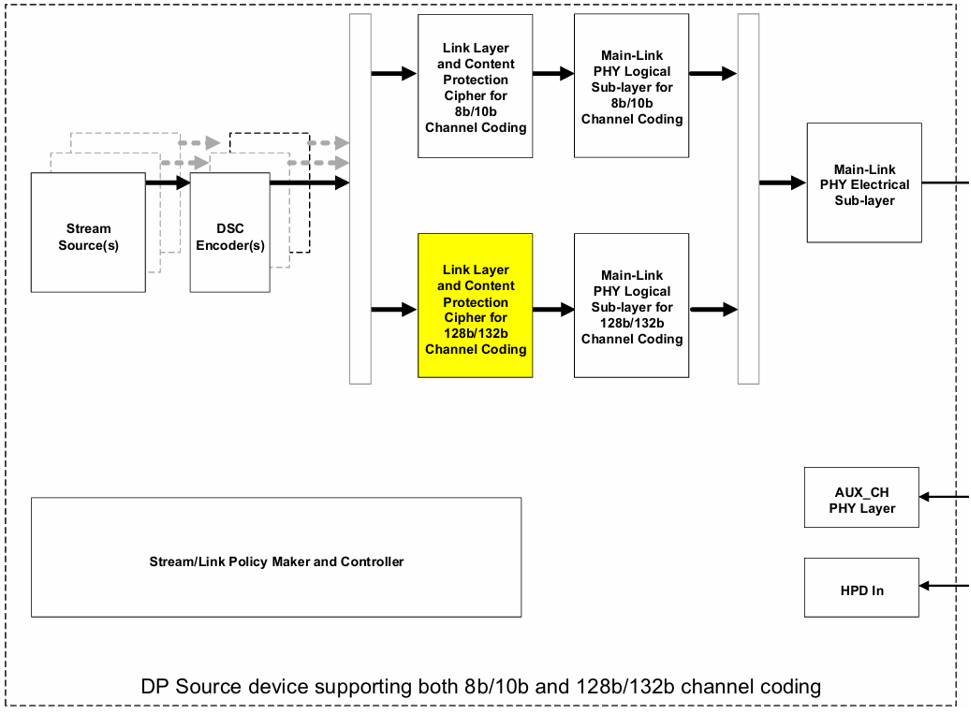

那在实现技术细节上有哪些变化呢?目前正在学习,但感觉相比DP1.4a变动非常大。因为DP2.0引入的128b/132b编码方式,同时又要能向下支持DP1.4a速率,而DP1.4a使用的是8b/10编码,不能共用,所以只能使用2个通路分别来实现。

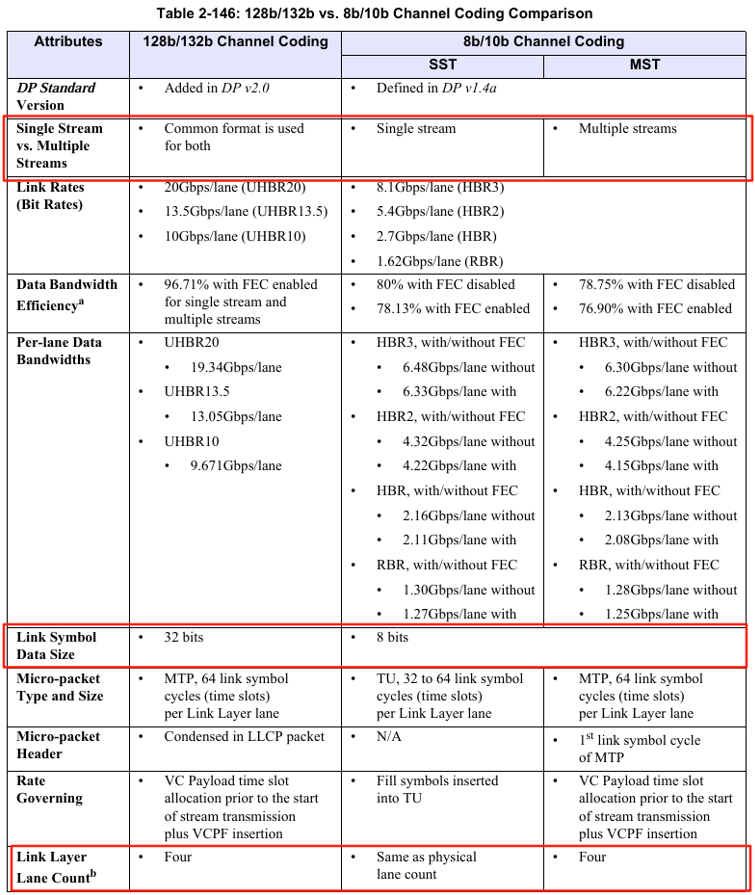

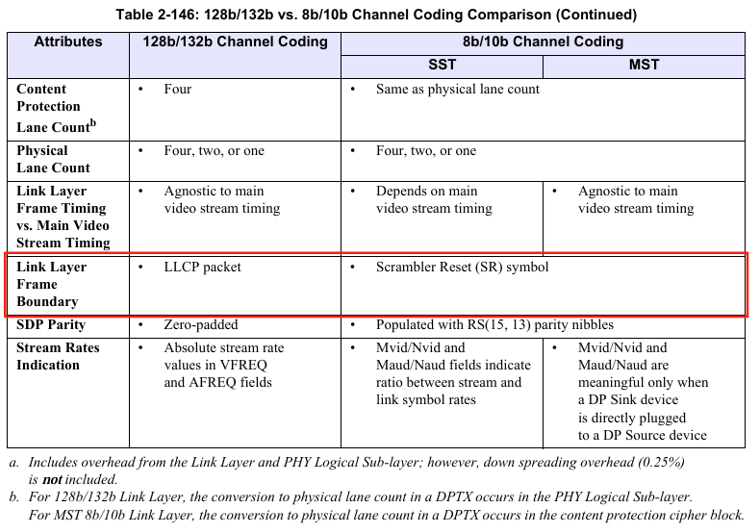

在DP2.0协议手册中列出了128b/132b和8b/10b通道编码的对比。

128b/132b主要带来了这些变化:

(1)统一采用MST传输方式中的MTP包类型,不采用8b/10b编码的SST传输方式中的TU传输单元类型。

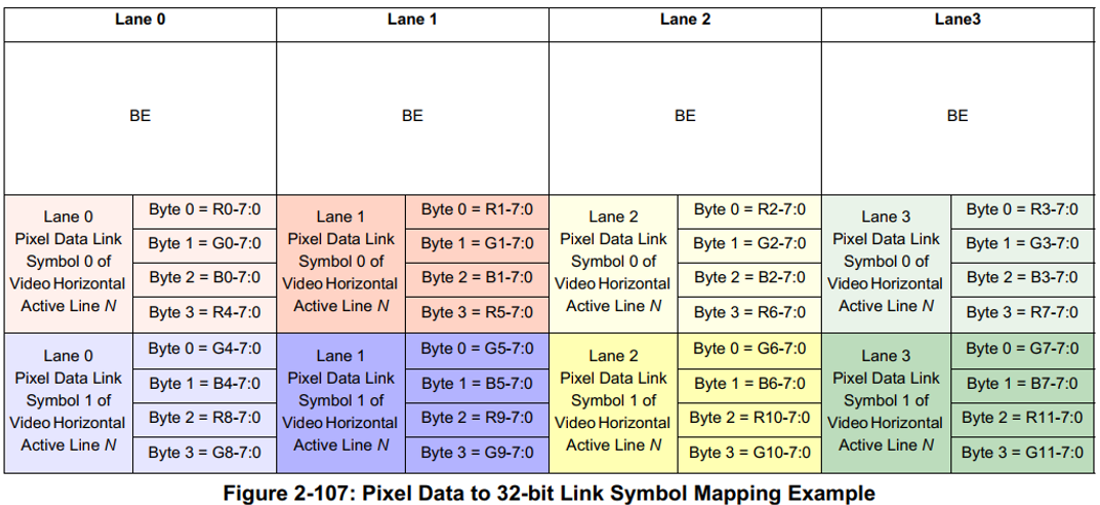

(2)8b/10b编码的Symbol符号是8bit,而128b/132b编码的Symbol符号是32bit。

(3)编码模块又分为link layer链路层和PHY Logical Sub-layer物理逻辑子层,128b/132b编码链路层统一按4lane处理,而物理逻辑子层则根据实际lane数进行映射。

(4)128b/132b编码链路层数据帧以LLCP包为边界,8b/10b编码链路层数据帧以SR扰码复位符号为边界。

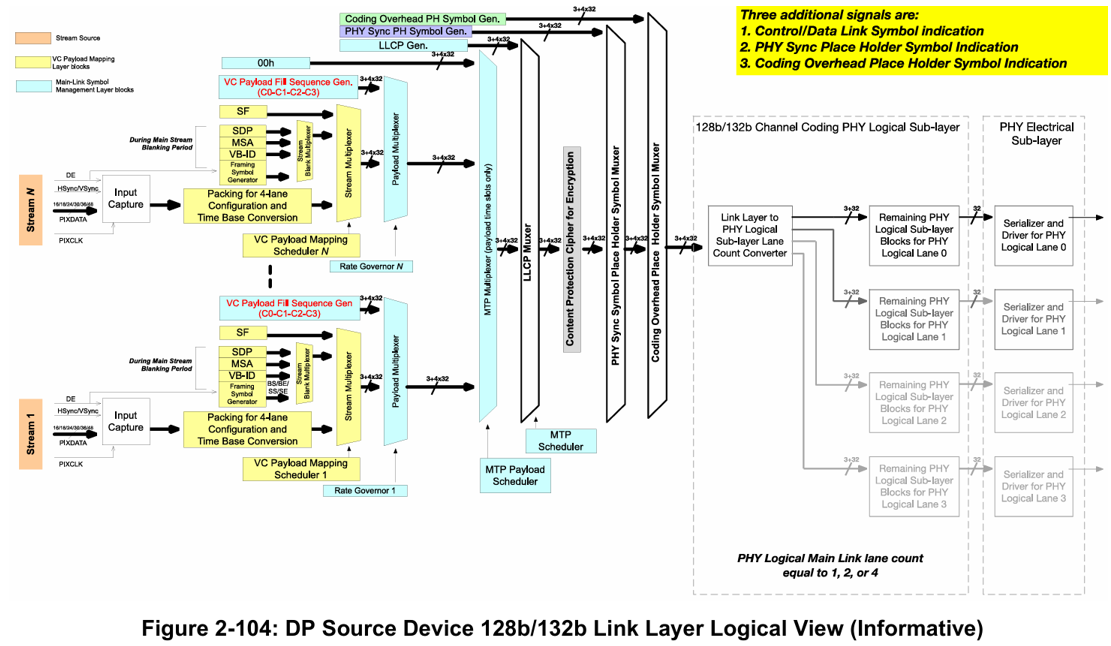

我们先看看link layer链路层有哪些变化。如下图左侧为链路层。

-

128b/132b编码的 Link Layer层link symbol由8bit提升到32bit,并且在Link Layer层总是按4个lane进行处理。

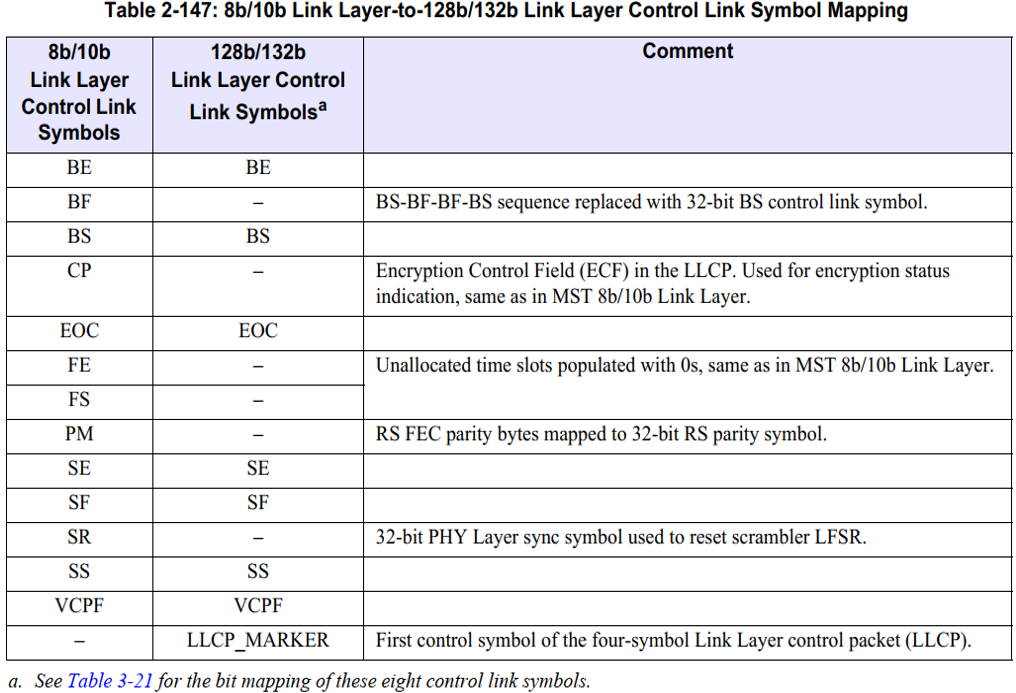

Link symbol可以是data link symbol数据链路符号,也可以是control link symbol控制链路符号。

data link symbol的32bit,低字节是对应8b/10b编码中的优先传输的LSB字节。

-

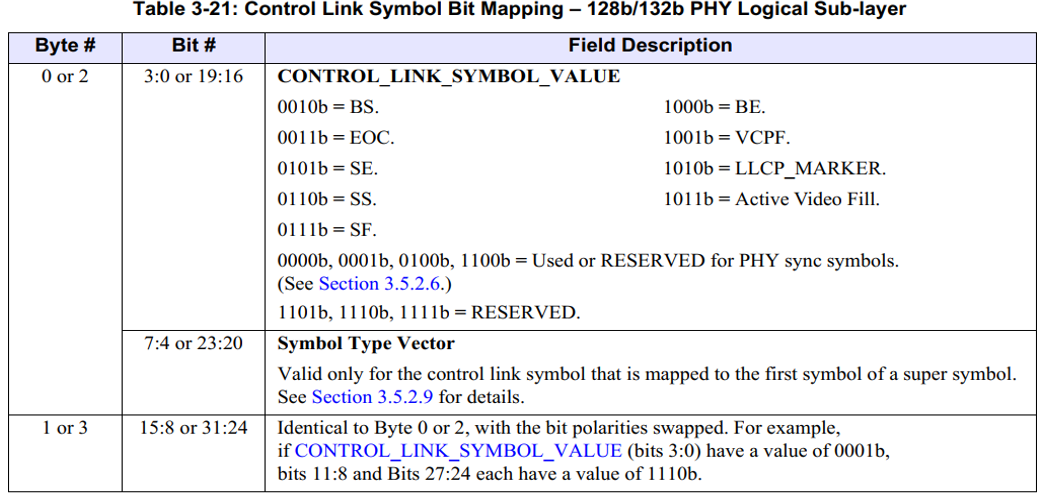

128b/132b Link Layer层control link symbol只有8个,每个symbol的与物理逻辑子层的32bit symbol对应。个人理解在Link Layer层时control link symbol 32bit怎么表示都可以,但在物理逻辑子层就要按对应格式映射。所以一般在Link Layer层就可以按物理逻辑子层的格式表示。

-

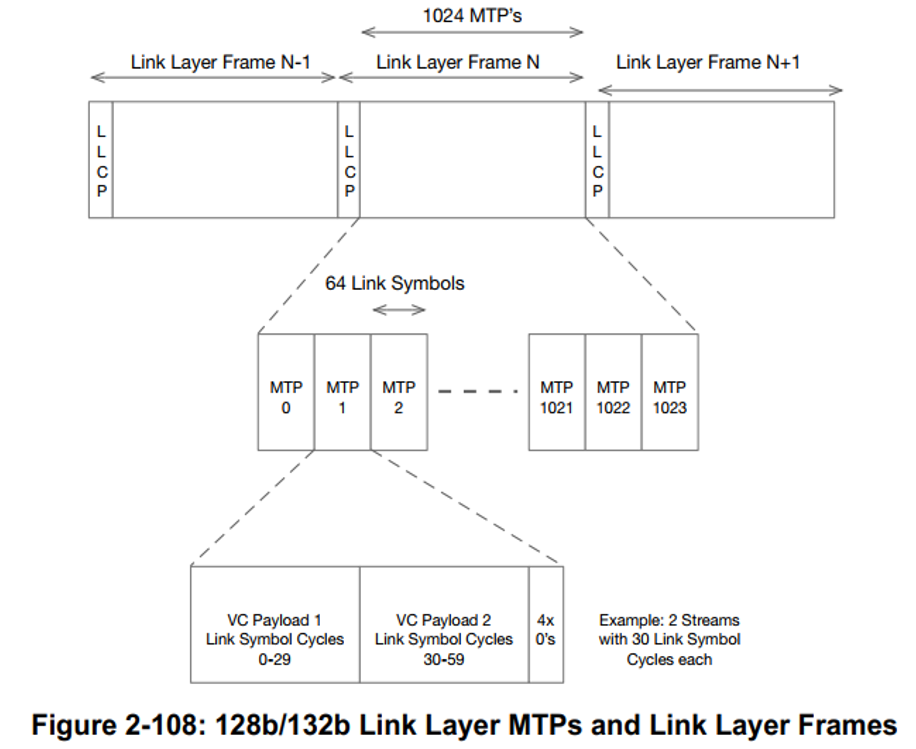

128b/132b采用MST格式,按MTP(Multi-stream Transport Packet)包传输。每个MTP包64个link symbols。每个link symbol cycle是32bit数据。每个link layer帧由1个LLCP包和1024个MTP包组成。

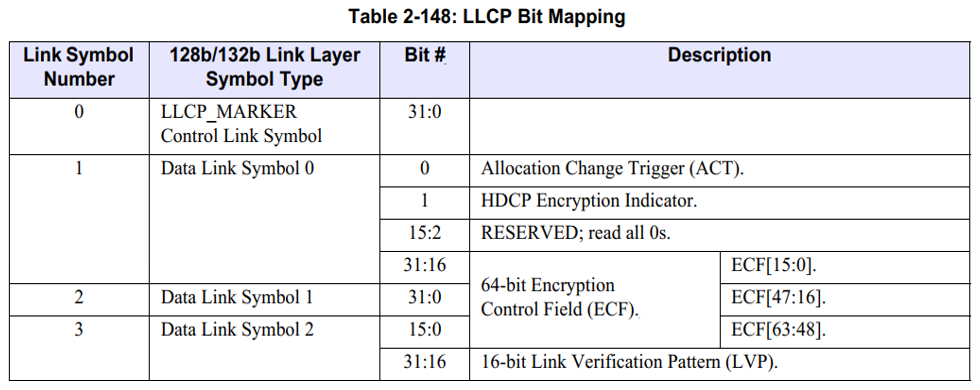

LLCP(Link Layer Control Packet)包格式是128bit,占4个link symbol cycle。第1个32bit是LLCP MARKER control link symbol。

-

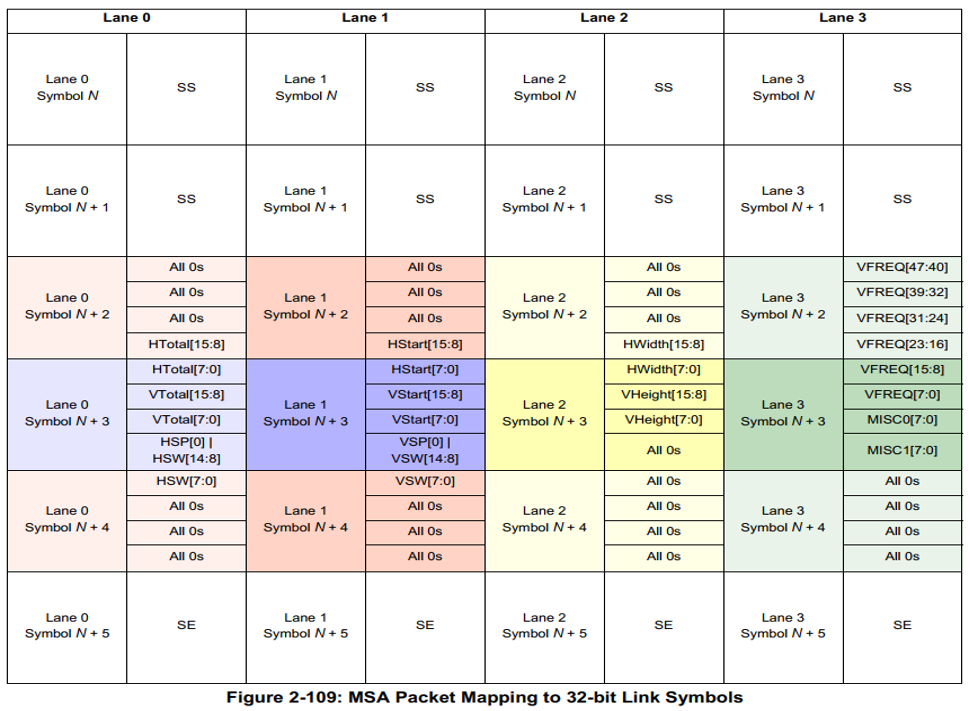

MSA信息仍然用SS,SS和SE symbol识别,但重新映射到32bit symbol。Mvid[23:0] 和Nvid[23:0]用VFREQ[47:0]代替,即pixel clk频率,精度在±1%以内。

-

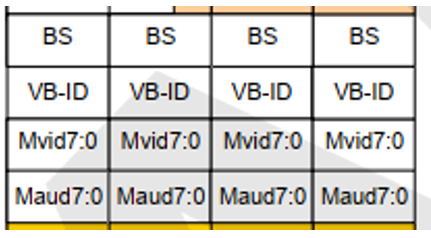

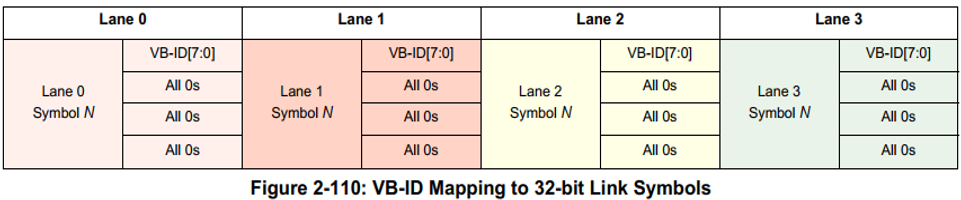

VB-ID也重新映射到32bit symbol,占每个symbol的最低字节。

在8b/10b link layer层,VB-ID后紧跟Mvid[7:0]和Maud[7:0](如下图)。

但在128b/132b link layer层不再使用Mvid[7:0]和Maud[7:0]。

- 链路层映射到物理逻辑子层的方法,是在link layer层插入Place Holder占位符

(另外在DP2.0附录M中还有不插入占位符的方法)

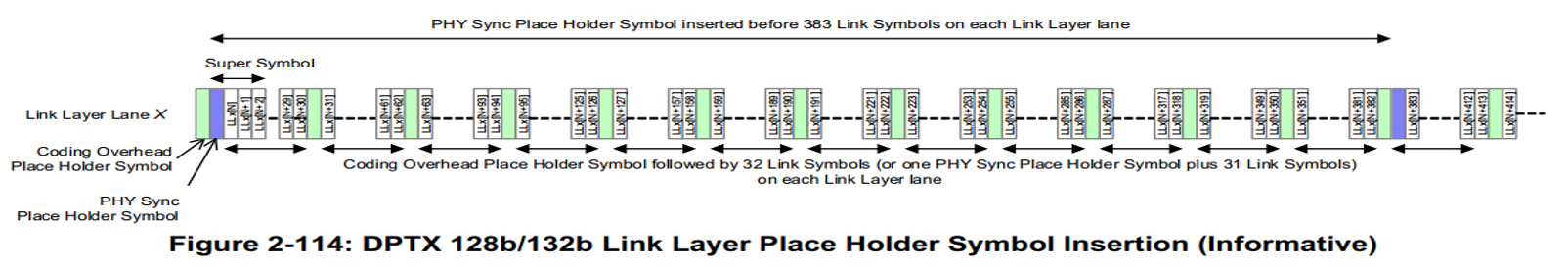

在128b/132b link layer层,Place Holder Symbol占位符插入规则:

• 每383个link symbols插入1个PHY sync占位符

• 为以下情况插入1个coding overhead占位符

• 1个PHY sync占位符和31个link symbols

• 32个link symbols

一共两种占位符:PHY同步占位符和Over heading占位符(开销占位符)

(1)每个PHY同步占位符32bit ,最终替换为LT_SCRAMBLER_RESET, POST_LT_SCRAMBLER_RESET, PHY_SYNC_ONLY符号

(2)每个开销占位符32bit ,最终替换为 CDI bits, RS padding bits, and RS parity symbols 符号

本文先记录DP2.0链路层的一些内容,后续再学习链路层到物理逻辑子层的映射,以及物理逻辑子层的内容。