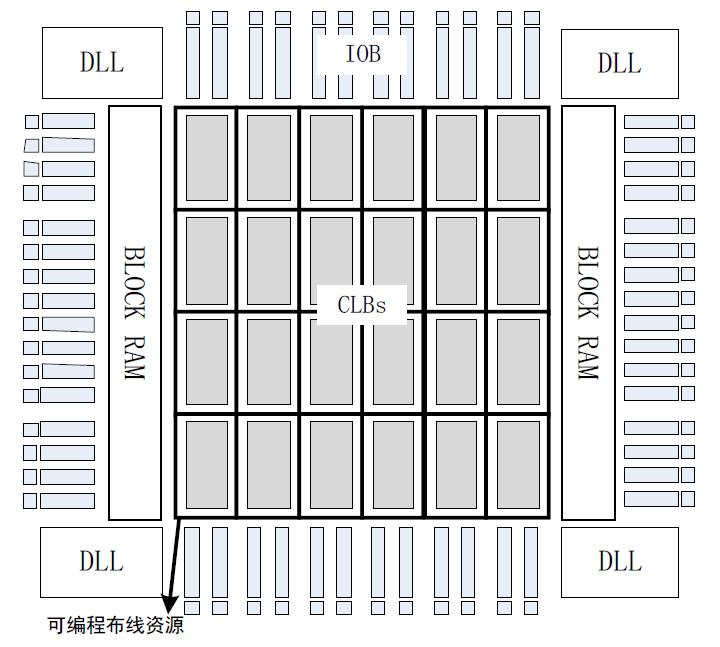

FPGA 的硬件结构

FPGA 的基本结构分为5 部分:可编程逻辑块(CLB)、输入/输出块(IOB)、逻辑块之间的布线资源、内嵌RAM 和内嵌的功能单元。

(1)可编程逻辑块(CLB)

一个基本的可编程逻辑块由一个寄存器(Register)和一个查找表(Look UpTable,LUT)组成。它是FPGA 内部可编程逻辑资源的基本组成。通过配置查找表,可以实现组合逻辑电路的功能。寄存器可以配置为各种触发器和锁存器。查找表和寄存器结合在一起可以实现各种逻辑设计。

(2)输入/输出块(IOB)

输入/输出块是FPGA 外部电路接口,需要满足各种信号的驱动和匹配要求。通过分布在FPGA 芯片边缘的寄存器将输入/输出块设计成可编程单元,可以通过配置文件的配置使FPGA 的接口可以满足各种电气标准和物理特性的需求。

(3)逻辑块间的布线资源

虽然FPGA 内部有着十分丰富的布线资源,但是布局布线的工作一般是由芯片设计厂商提供的设计软件来完成,设计者并不需要进行详细的布局布线设计。设计者不需要做布局布线的设计并不代表布线工作不重要,布局布线的结果直接影响功能设计的运行结果,尤其是时序上的影响。

(4)内嵌RAM 块

设计者可以根据设计需要将内嵌RAM 块配置成各种类型的存储结构。除了使用BRAM 外,还可以将查找表配置成分布式RAM 来满足小容量RAM 的设计需求。

(5)内嵌功能单元

FPGA 一般会嵌入一些比较常用的功能模块,如锁相环、延迟锁定环、CPU和DSP 等。特定型号的FPGA 内部也会有CPU 这种软处理核,这种类型FPGA不仅当作硬件设计平台来使用还可以做一些系统级设计。随着越来越多的设计需求,更多的功能模块会逐步内嵌到FPGA 中。