基于FPGA的DES加解密系统verilog实现,包含testbench和开发板硬件测试

目录

1.课题概述

2.系统测试效果

3.核心程序与模型

4.系统原理简介

5.完整工程文件

1.课题概述

基于FPGA的DES加解密系统verilog实现,包含testbench和开发板硬件测试。输入待加密数据,密钥,输出加密数据,然后通过解密模块输出解密后的原数据。

2.系统测试效果

仿真测试

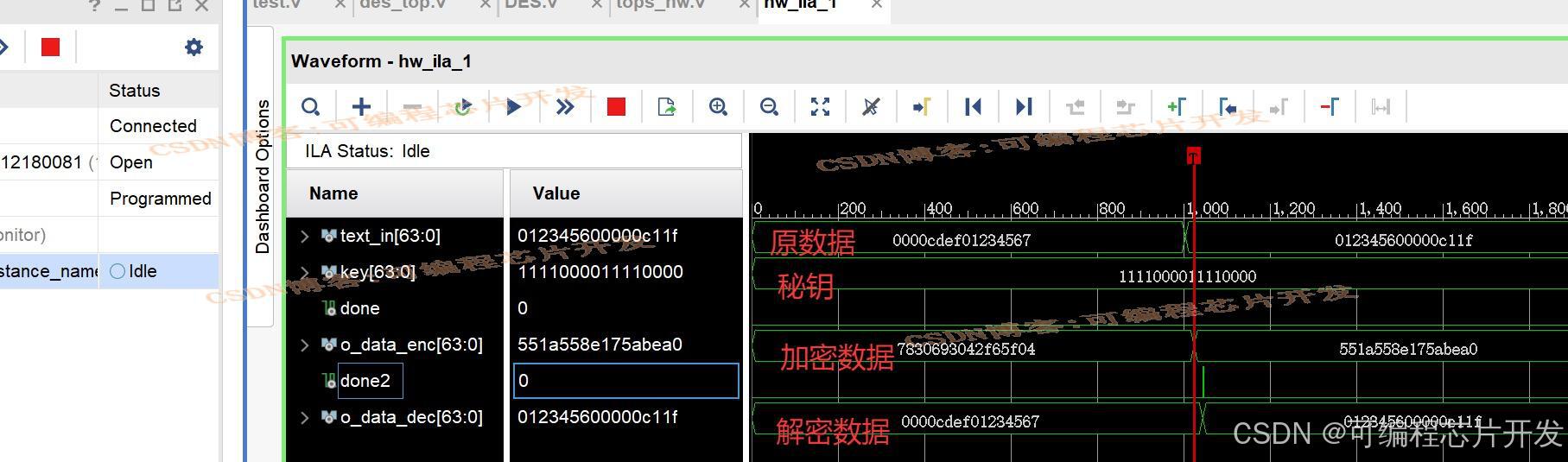

硬件下载测试

在实际测试过程中,如果你的开发板和我的不一样,可以参考本博客置顶文章进行硬件配置修改:

FPGA系统开发板调试过程不同芯片的移植步骤介绍_紫光fpga移植软核的步骤-CSDN博客

通过这个链接的步骤,可以实现不同开发板上的系统调试。

3.核心程序与模型

版本:vivado2022.2

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/05/27 20:41:08

// Design Name:

// Module Name: tops_hw

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tops_hw(

input i_clk,

input i_rst,

output led);reg[15:0]cnt;

always @(posedge i_clk or negedge i_rst)

beginif(~i_rst)begincnt<=16'd0;end elsebeginif(cnt==16'd60000)cnt<=16'd1;elsecnt<=cnt+16'd1;end

endreg start;

reg[63:0]key;

reg[63:0]text_in; always @(posedge i_clk or negedge i_rst)

beginif(~i_rst)beginstart <=1'd0;key <=64'd0;text_in <=64'd0;end elsebeginif(cnt==16'd1 | cnt==16'd20001 | cnt==16'd40001)start <=1'd1;elsestart <=1'd0;if(cnt==16'd1)begintext_in <= 64'h1101_1011_0011_1100;key <= 64'h0001_0002_0003_0004;endif(cnt==16'd20001)begintext_in <= 64'h0000_cdef_0123_4567;key <= 64'h1111_0000_1111_0000;endif(cnt==16'd40001)begintext_in <= 64'h0123_4560_0000_c11f;key <= 64'h1111_0000_1111_0000;endend

endwire done;

wire [63:0] o_data_enc;

wire done2;

wire [63:0] o_data_dec;des_top des_top_jiam (.i_clk(i_clk), .i_rst(i_rst), .i_decrypt(1), .i_data(text_in), .i_key(key), .o_data(o_data_enc), .o_ready(done),.r_enable(),.des_data());des_top des_top_jiem (.i_clk(i_clk), .i_rst(i_rst), .i_decrypt(0), .i_data(o_data_enc), .i_key(key), .o_data(o_data_dec), .o_ready(done2),.r_enable(),.des_data());assign led= 4'b0000;ila_0 your_instance_name (.clk(i_clk), // input wire clk.probe0({text_in,key,o_data_enc,done,o_data_dec,done2}) // input wire [519:0] probe0

);

endmodule

00X6_005m4.系统原理简介

数据加密标准(Data Encryption Standard, DES)是 20 世纪 70 年代由IBM公司开发的一种对称密钥加密算法,1977年被美国国家标准局(NBS)正式采纳为联邦信息处理标准(FIPS PUB 46)。DES作为历史上首个广泛应用的商用加密算法,奠定了现代密码学的基础,尽管其56位密钥长度在如今已被认为不够安全,但其设计思想和技术细节对后续加密算法(如AES)的发展产生了深远影响。

DES是一种分组密码,采用对称密钥体制,即加密和解密使用相同的密钥。其核心设计包括以下特点:

1.分组处理:将明文按64位分组进行加密。

2.密钥长度:名义上密钥为64位,但实际有效密钥长度为56位,其余8位用于奇偶校验。

3.Feistel网络结构:采用16轮Feistel网络迭代,通过交替的置换和替换操作实现混淆与扩散。

4.雪崩效应:输入的微小变化会导致输出的显著变化,增强加密安全性。

DES中的置换(如 IP、PC-1、PC-2、P盒)和替换(S盒)操作构成了其安全基础:

置换操作:通过位置重排实现数据扩散,数学上可表示为置换函数π:π:{1,2,…,n}→{1,2,…,n}

替换操作:通过非线性映射实现数据混淆,如S盒的数学表示为:S:{0,1}6→{0,1}4

异或运算(⊕)是DES中的核心运算,具有以下性质:

交换律:a⊕b=b⊕a

结合律:(a⊕b)⊕c=a⊕(b⊕c)

自反性:a⊕a=0

与1异或取反:a⊕1=¬a

这些性质保证了DES加密和解密过程的对称性。

算法实现步骤总结

密钥生成:从64位密钥生成16个48位子密钥。

初始置换:对64位明文进行初始置换。

16轮Feistel网络:每轮包括扩展置换、子密钥异或、S盒替换、P盒置换。

最终置换:对Feistel网络输出进行最终置换得到密文。

5.完整工程文件

v