PCIe学习笔记(3)链路初始化和训练

PCIe学习系列往期文章

PCIe学习笔记(1)Hot-Plug机制

PCIe学习笔记(2)错误处理和AER/DPC功能

文章目录

- 链路训练概述

- Bit Lock

- Symbol Lock (Gen1/2)

- Block Alignment (Gen3+)

- Lane Polarity Inversion

- Lane Reversal

- Lane-to-Lane De-skew

- Link Width/Link Speed

- Link Speed Change

- Link Width Change

- 链路训练有序集

- Ordered Sets

- Training Sequences

- APN (Alternate Protocol Negotiation)

- LTSSM (Link Training and Status State Machine)

链路训练概述

PCIe链路初始化训练由PL物理层硬件自发启动完成,并通过LTSSM管理,以建立稳定可靠的通信链路。链路训练过程中主要完成一下步骤。

Bit Lock

链路训练期间,接收端的时钟和数据恢复(CDR,Clock and Data Recovery)逻辑通过使用数据比特流作为时钟的参考信号,来重建发送端的时钟。

Symbol Lock (Gen1/2)

完成了Bit Lock后,只能识别出数据流中的0和1,还是不知道发送的内容。Gen1/2采用8b/10b编码,10bit为一个Symbol。当发送端和接收端交换训练有序集 TS1 和 TS2 时(TS1/TS2 以 COM 字符作为开端),接收端在比特流中搜索可识别的数据图样(pattern)。通过识别COM(K28.5)等控制字符来确定每个字符的开始与结束为止,即Symbol Lock。由于COM独一的feature(0011111010或者1100000101)。发送端COM不会被加扰(scrambled)就是为了Rx可以轻松的检测到COM。

Block Alignment (Gen3+)

Gen3后采用128b/130b编码,2bit的同步头和128bit的Payload称为Block。Gen3后不存在COM字符,在链路训练期间,EIEOS(Electrical Idle Exit Ordered Set,电气空闲退出有序集,00h和FFh交替出现)用于定位Block边界。包含三个 Phase:

- Unaligned Phase,Rx 收到 EIOS 后进入,如切速至8GT/s或从低功耗状态退出。在此阶段 Rx 依据 SKPOS 调整块对齐边界,Rx 收到 EIEOS 后进入 Aligned Phase。

- Aligned Phase,Rx 继续监测 EISOS 和依据 SKPOS 调整块对齐。若收到 SDS,进入 Locked Phase。若 Rx 收到未定义的Sync header(00b或11b),退至 Unaligned Phase。

- Locked Phase,为防止数据丢失,Rx 进入此阶段后不再调整块对齐边界,并预期SDS后接数据块。若 Rx 收到未定义的Sync header(00b或11b),退至 Unaligned Phase。

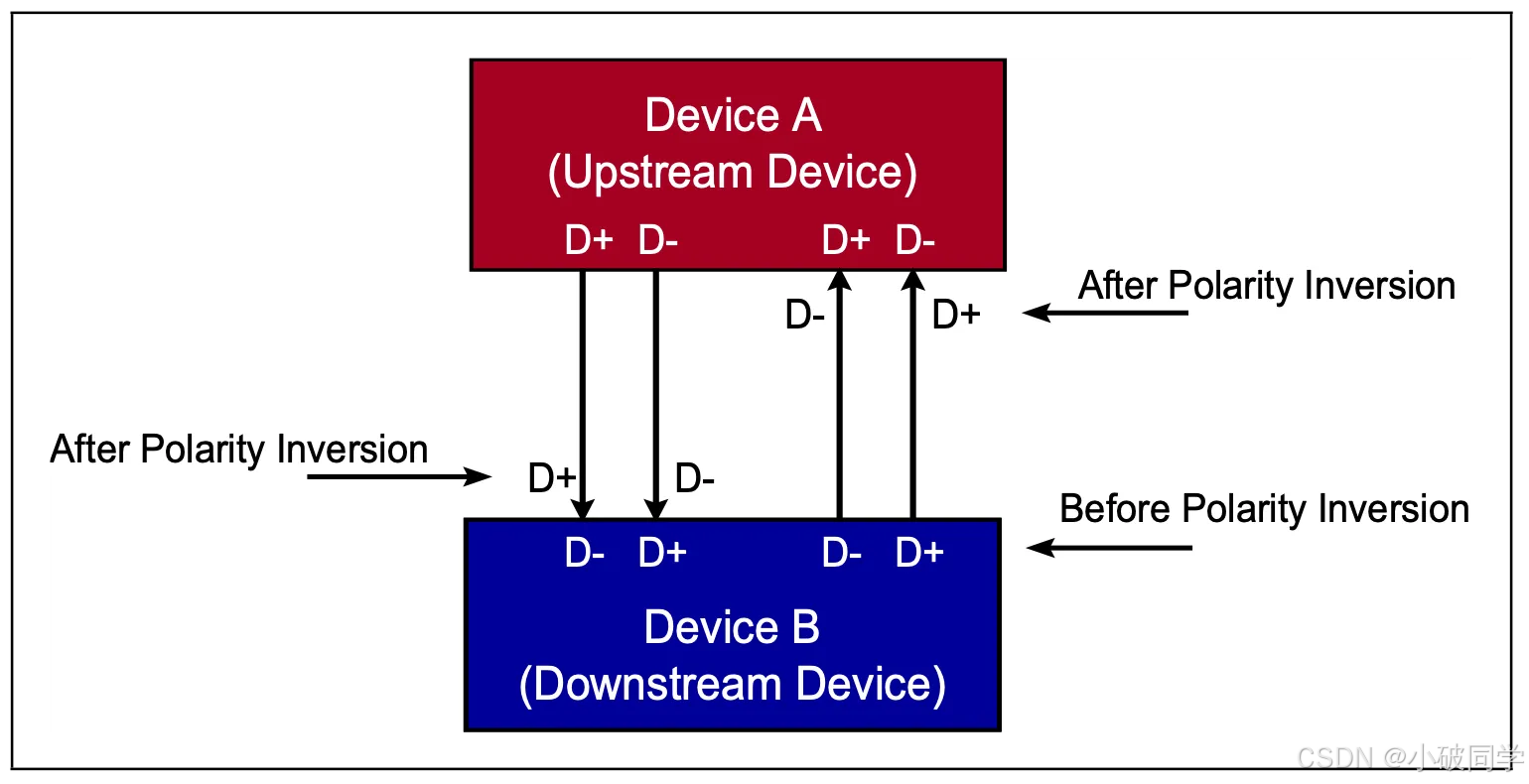

Lane Polarity Inversion

为简化 PCB 布局和连线,PCIe Link 两端设备的对应差分信号极性可以相反的。因此,PCIe允许在链路训练与初始化时,对其进行调整。该功能是所有标准 PCIe设备都应支持的。

接收端在Polling的训练序列中检测输入 TS1 和 TS2 的Symbol 6-15。如果接收端在 TS1 中收到了 D21.5 而不是预期的 D10.2,或者在 TS2 中收到了 D26.5 而不是预期的 D5.2,这代表当前通道差分对极性反转,需要进行校正。

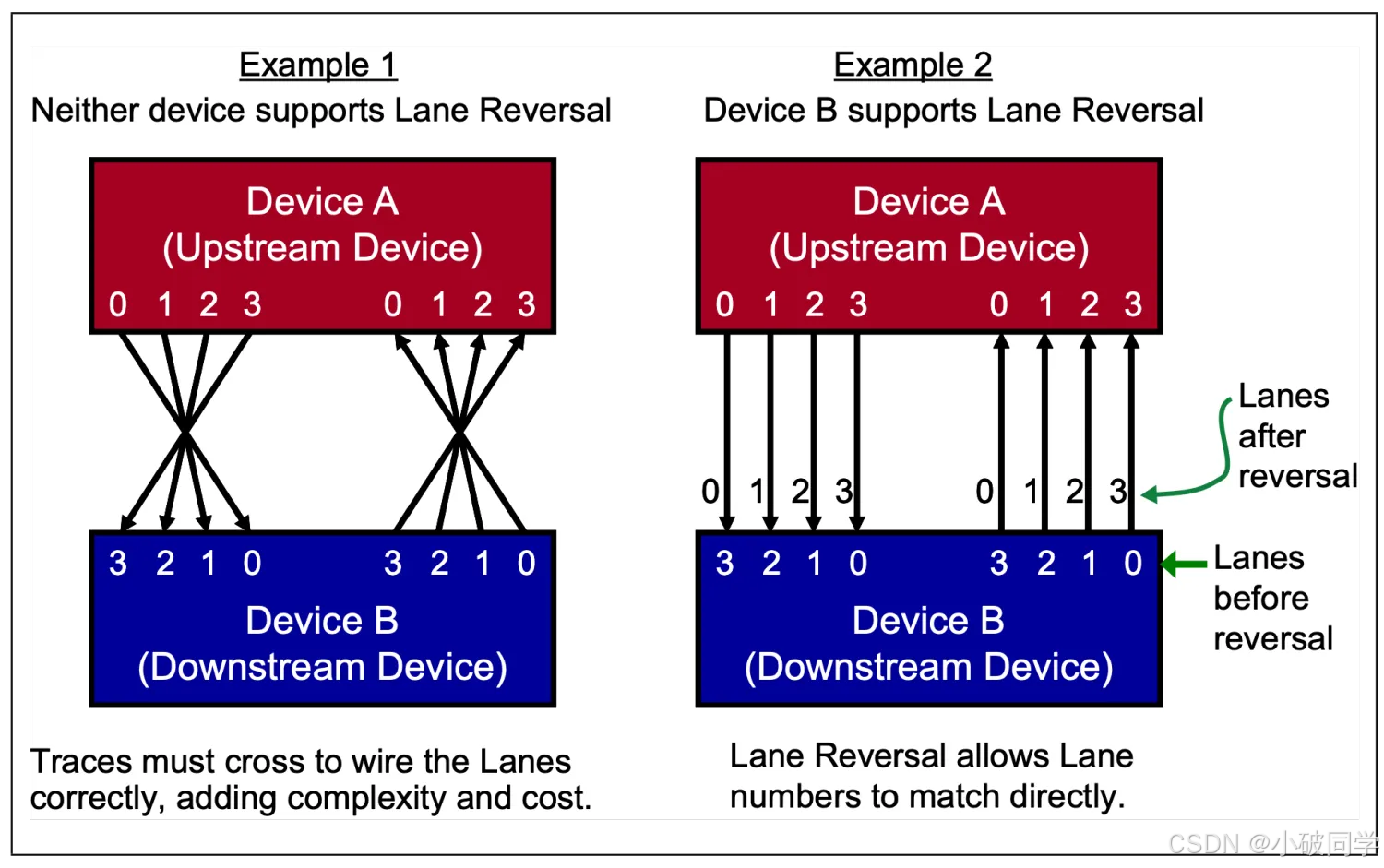

Lane Reversal

有的时候两个 PCIe 设备的通道排列位置可能不太一致, PCIe允许对默认的通道排列位置重新排列,以简化PCB布线。这一功能是可选的。

Lane Reversal还有一种极端的场景,如下图,被称为flipping。该场景分别发生在下述情况下:

● lane由PCle链路或芯片封装引脚的物理布局反转。

● 当将较窄的链路连接到较宽对端的上层lane时。

● lane不可操作(损坏)。

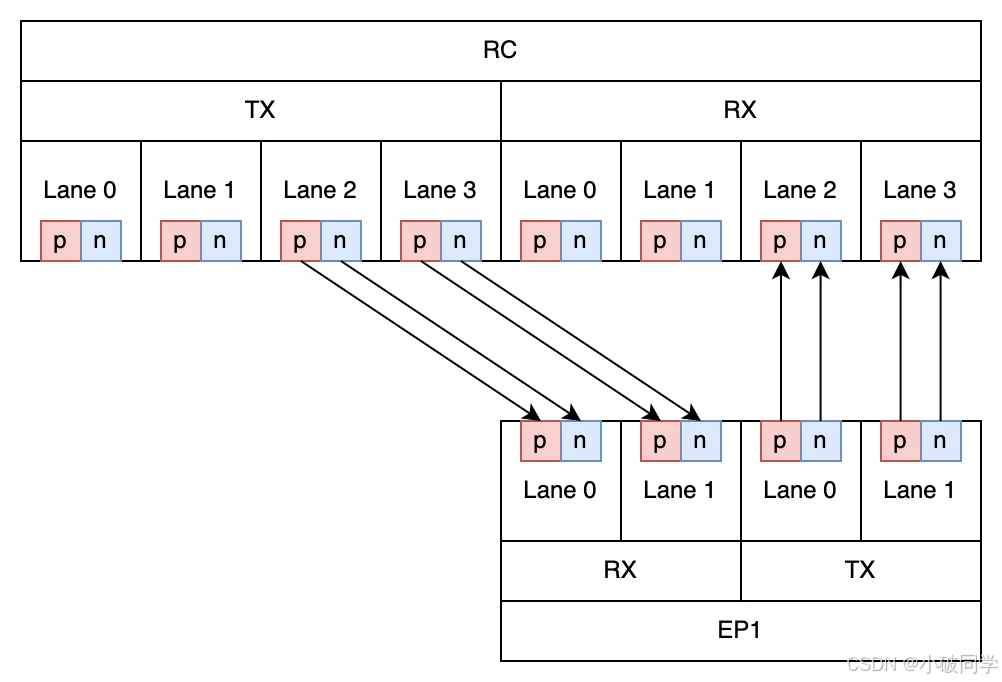

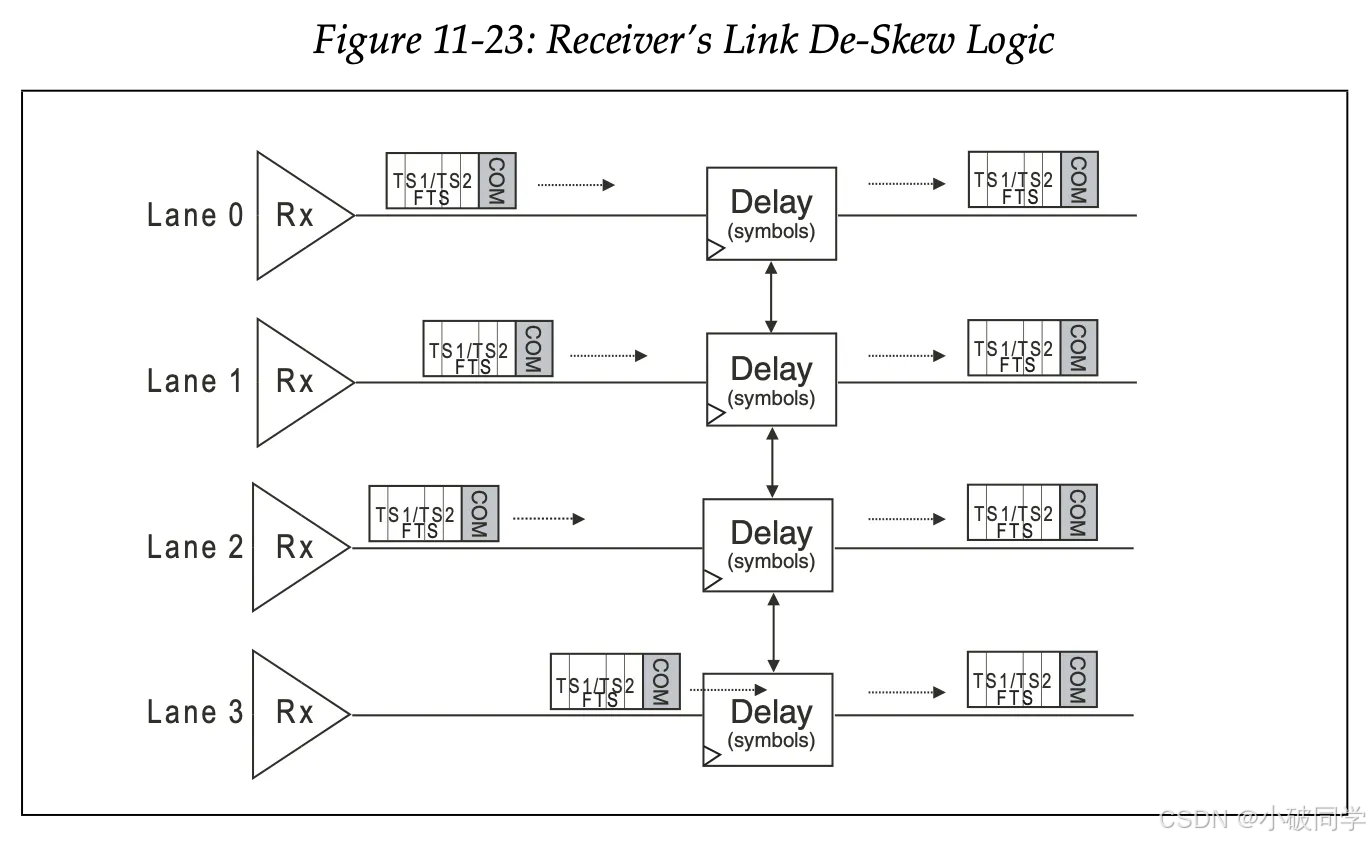

Lane-to-Lane De-skew

各个通道之间的传输线长度差异或者其他因素,会导致多通道链路中原本同时传输的多个并行比特,到达接收方的时间有所差异,这被称之为信号偏斜(signal skew)现象。 接收方需要通过延迟较早到达的通道,以对齐所有通道上的信号的到达时间,补偿通道之间信号传输快慢差异。在协议规定的可允许的信号偏移范围内,(对于 2.5Gbps 速率来说,最大信号偏斜是 20ns),接收方需要能够自动对偏移进行补偿。

Ordered Sets在所有Lane上同时发送,必须在所有通道上同时看到相同的Symbol (COM)/Sync才能执行去偏斜。去偏斜只在 L0s、恢复(Recovery)和配置(Configuration)LTSSM 状态下执行。

Link Width/Link Speed

系统刚复位的时候,链路训练和初始化都是基于 2.5 GT/s 的速率的。如果 Link两端的设备都支持更高的速率,则会自动进入 Recovery 状态,以重新切换速率。

在链路训练与初始化过程中,相邻设备需要相互通信来确定其支持的最大链路宽度。链路内所有通道必须基于相同频率。

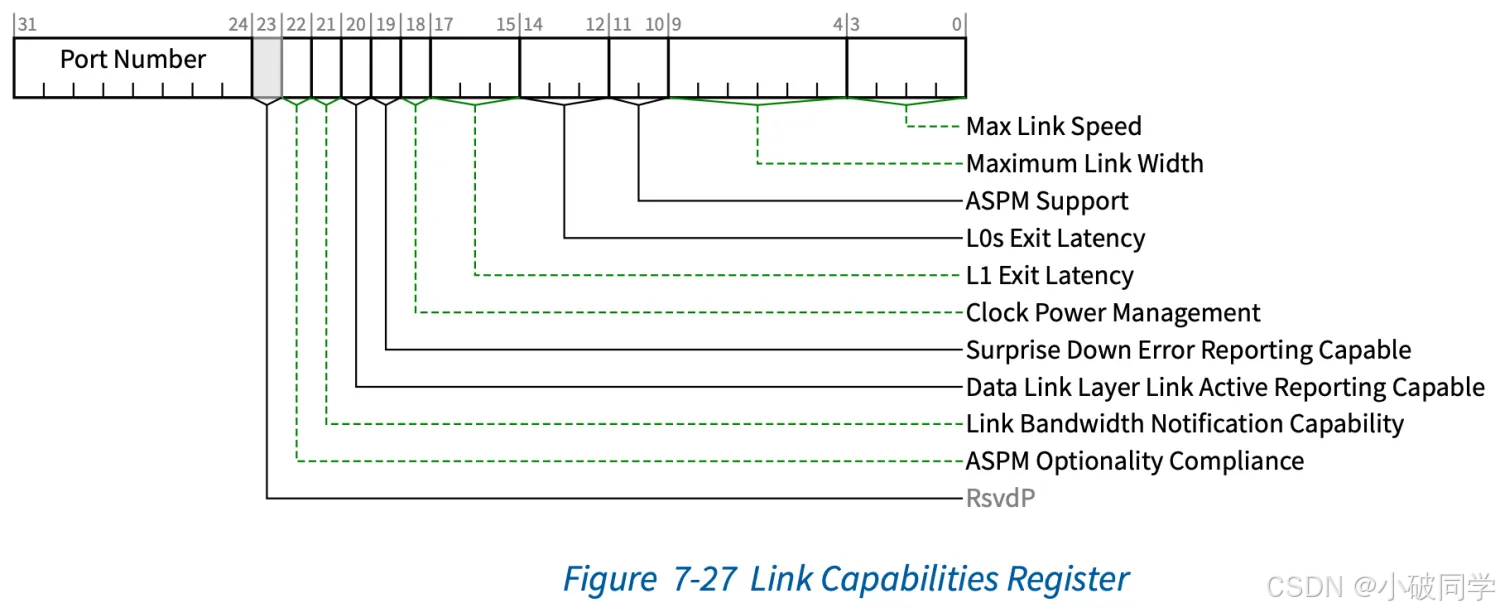

0x7C Link Capabilities Register

[3:0] Max_Link_Speed 链路最高速率,指向Link_Capabilities_2.Supported_Link_Speeds_Vector的指针,RO

[9:4] Maximum Link Width 链路最大宽度,RO

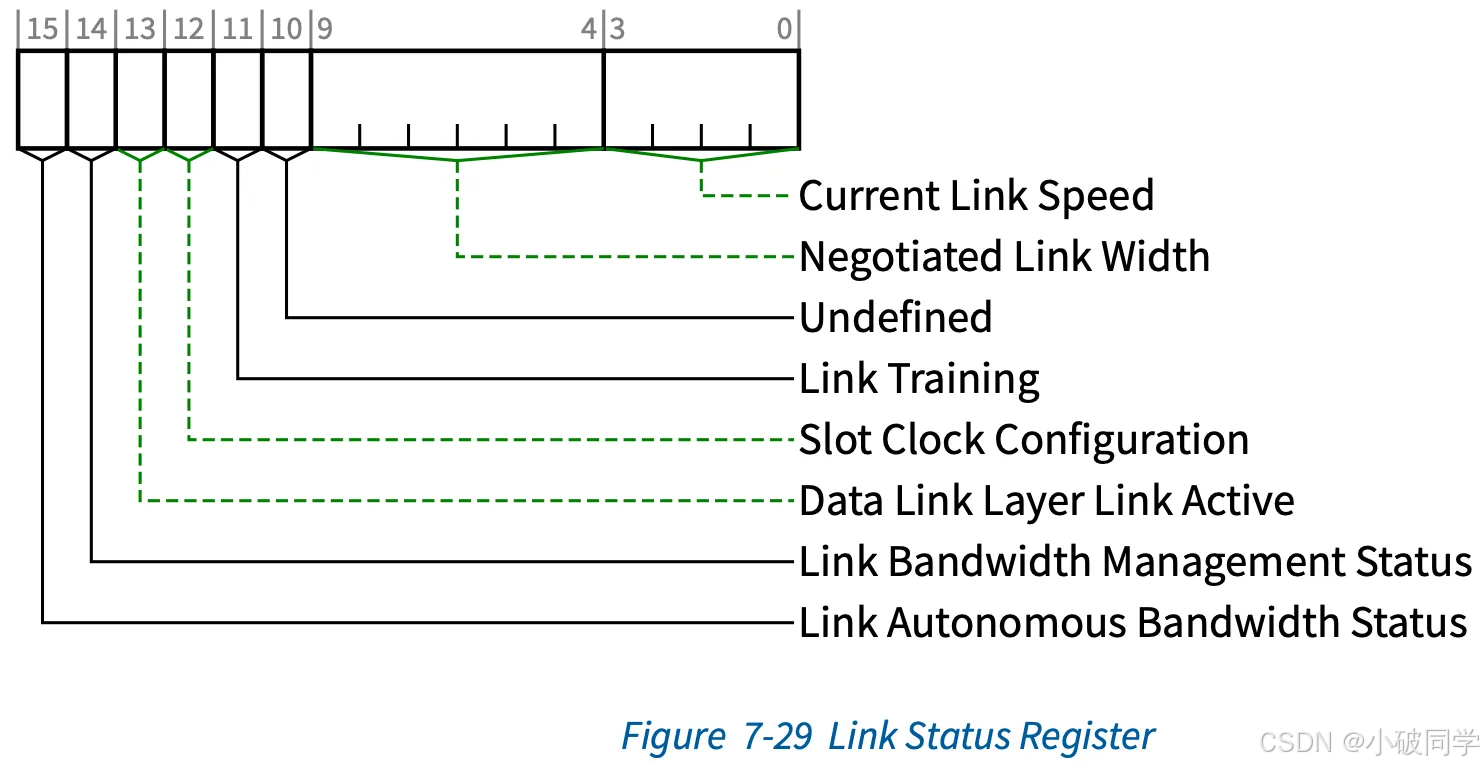

0x82 Link Status Register

[3:0] Current Link Speed 当前链路速度,RO。Link up前为未定义状态。

[9:4] Negotiated Link Width 链路宽度协商的结果,RO。Link up前为未定义状态。

[10] Undefined 当前版本无定义,早前版本用于指示Link Training Error。

[11] Link Training 表示 LTSSM 正处于Configuration或Recovery状态或Link_Control.Retrain_Link = 1,RO。LTSSM退出Configuration或Recovery状态时clear。该比特只对 DP 有意义,对UP保留。

Link Speed Change

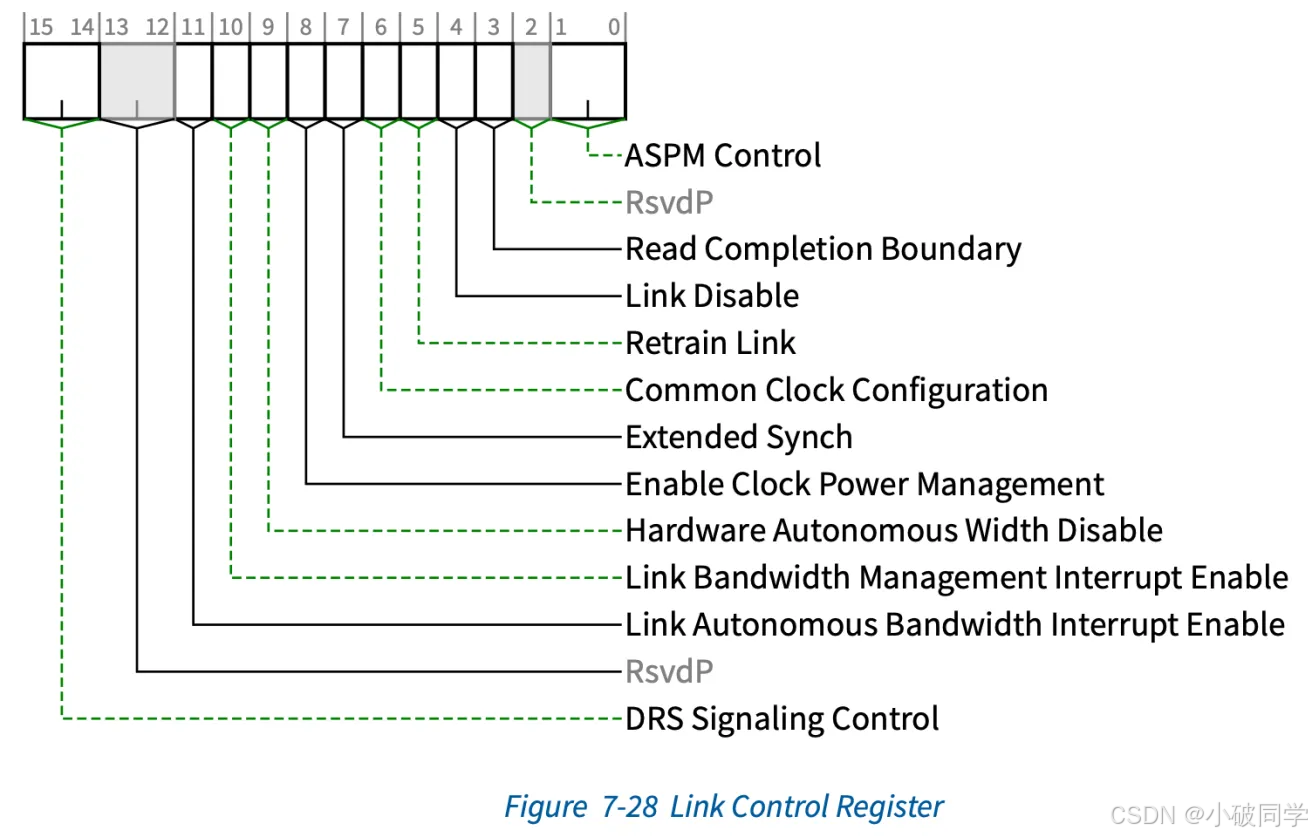

速率改变必须由UP发起,发起后进入Recovery状态。Directed Speed Change = 1,链路会尝试进入双方支持的最搞速率。

当硬件已经决定改变链路速率后,软件无法再控制速率改变流程,但是软件可以限制或者禁止硬件的速率改变行为。

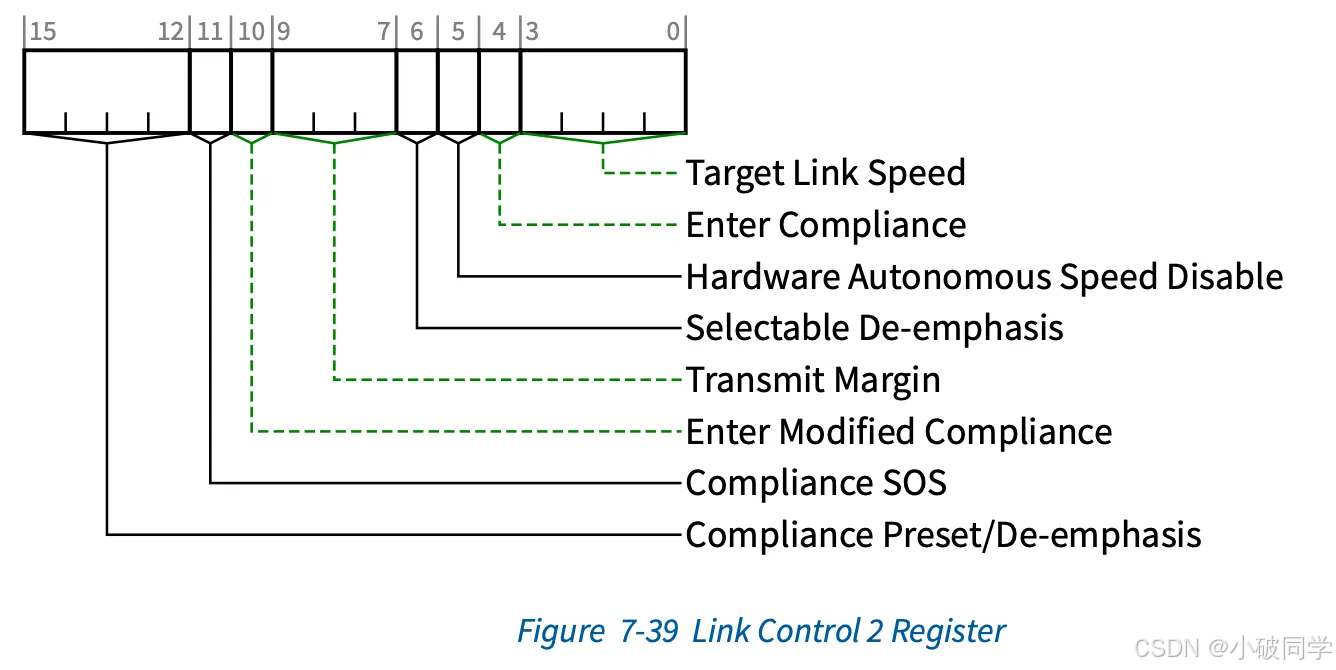

可以修改Link_Control_2.Target_LInk_Speed (Bit3:0),然后置位Link_Control.Retrain_Link发起链路重训练。

可以设置Link_Control_2.Hardware Autonomous Speed Disable (Bit5),关闭USP硬件的自动速率改变功能。

Link Width Change

窄链路恢复宽链路称Link Upconfigure(TS2)。

UP进入Recovery发起链路宽度改变请求(TS1.speed_change = 0)。

软件不能够发起链路宽度改变,但是可以通过设置 Link_Control.Hardware_Autonomous_Width_Disable (Bit10) 禁止硬件发起链路宽度改变。

链路训练有序集

Ordered Sets

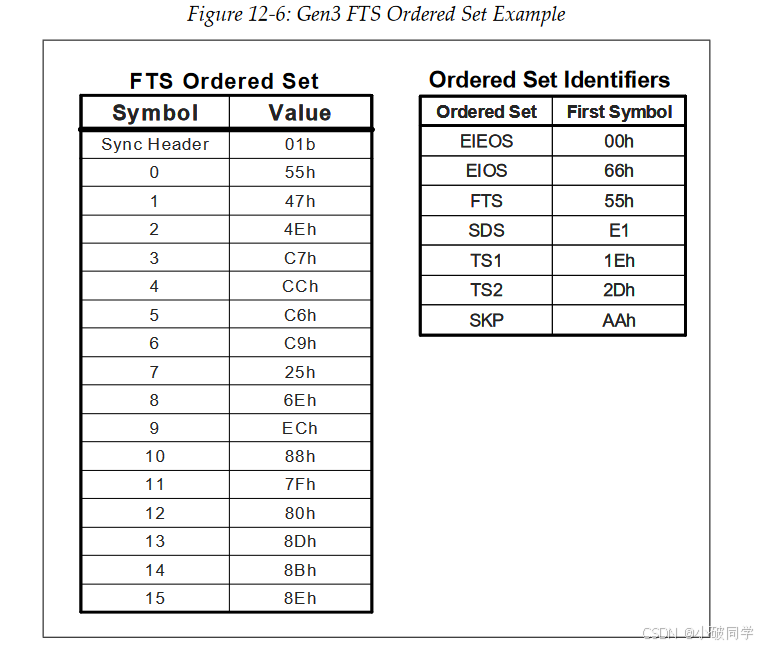

仅由物理层使用。每个Ordered Set Block都以一个Sync Header开始,后跟一个Ordered Set。

Ordered Sets始终4Byte对齐,仅SKP OS为可变长度。

Symbol 0定义类型,多通道链路所有Lane必须同时传输相同类型的Ordered Set(后续Symbol不必相同,Polling.Compliance例外)。

- SOS - SKP Ordered Set:用于补偿链路两端时钟频率差异,8/12/16/20/24byte,只能在Block边界

- EIOS - 电气空闲有序集(Electrical Idle Ordered Set):用于进入电气空闲状态

- EIOSQ (Electrical Idle Ordered Set Sequence),仅在5.0 GT/s由两个EIOS组成

- 8b/10b编码下是COM(K28.5) + 3个IDL(K28.3)

- EIEOS - 电气空闲退出有序集(Electrical Idle Exit Ordered Set):交替的全0和全1信号(模拟低频时钟信号),现用于两个目的:

- 电气空闲退出,这与前几代相同

- 用于指示 8.0 GT/s 速率下的块对齐边界

- TS1 - 训练序列 1 有序集(Training Sequence 1 Ordered Set)

- TS2 - 训练序列 2 有序集(Training Sequence 2 Ordered Set)

- FTS - 快速训练序列有序集(Fast Training Sequence Ordered Set)

- SDS - 数据流开始有序集(Start of Data Stream Ordered Set)Gen3 新增

- TS0 - Gen6新增

Training Sequences

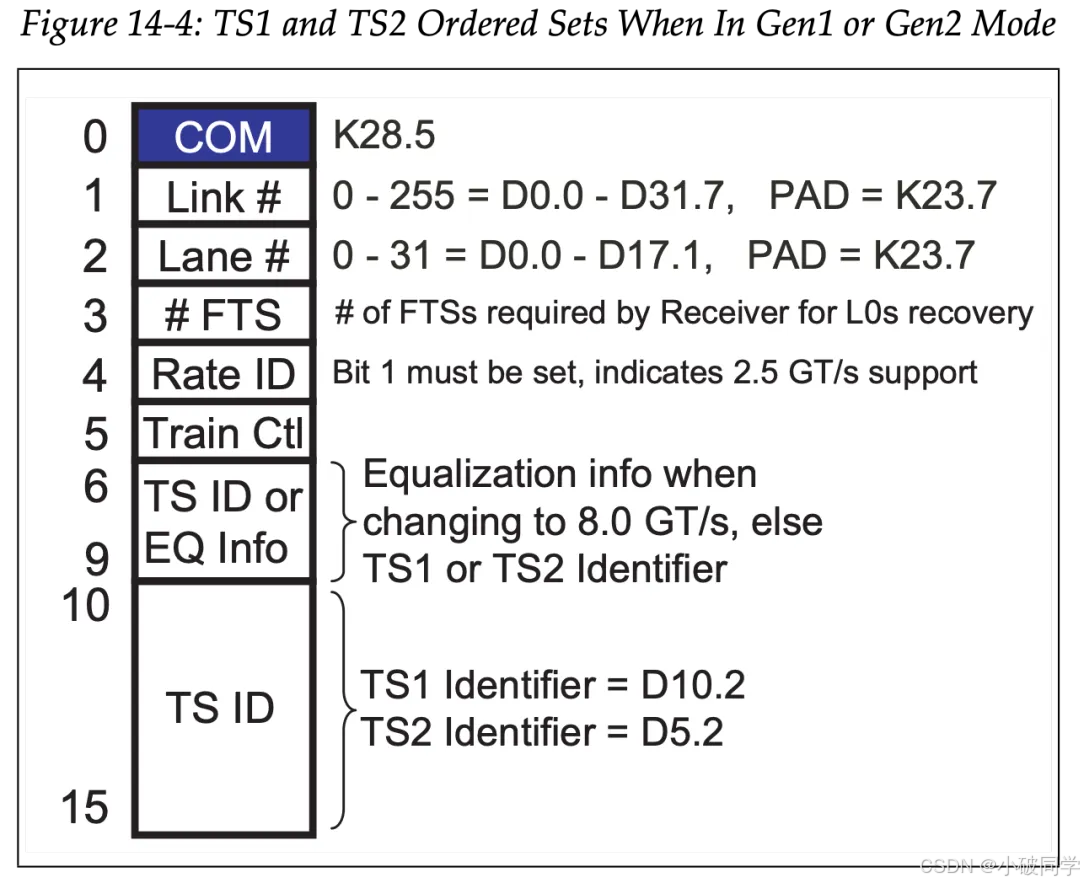

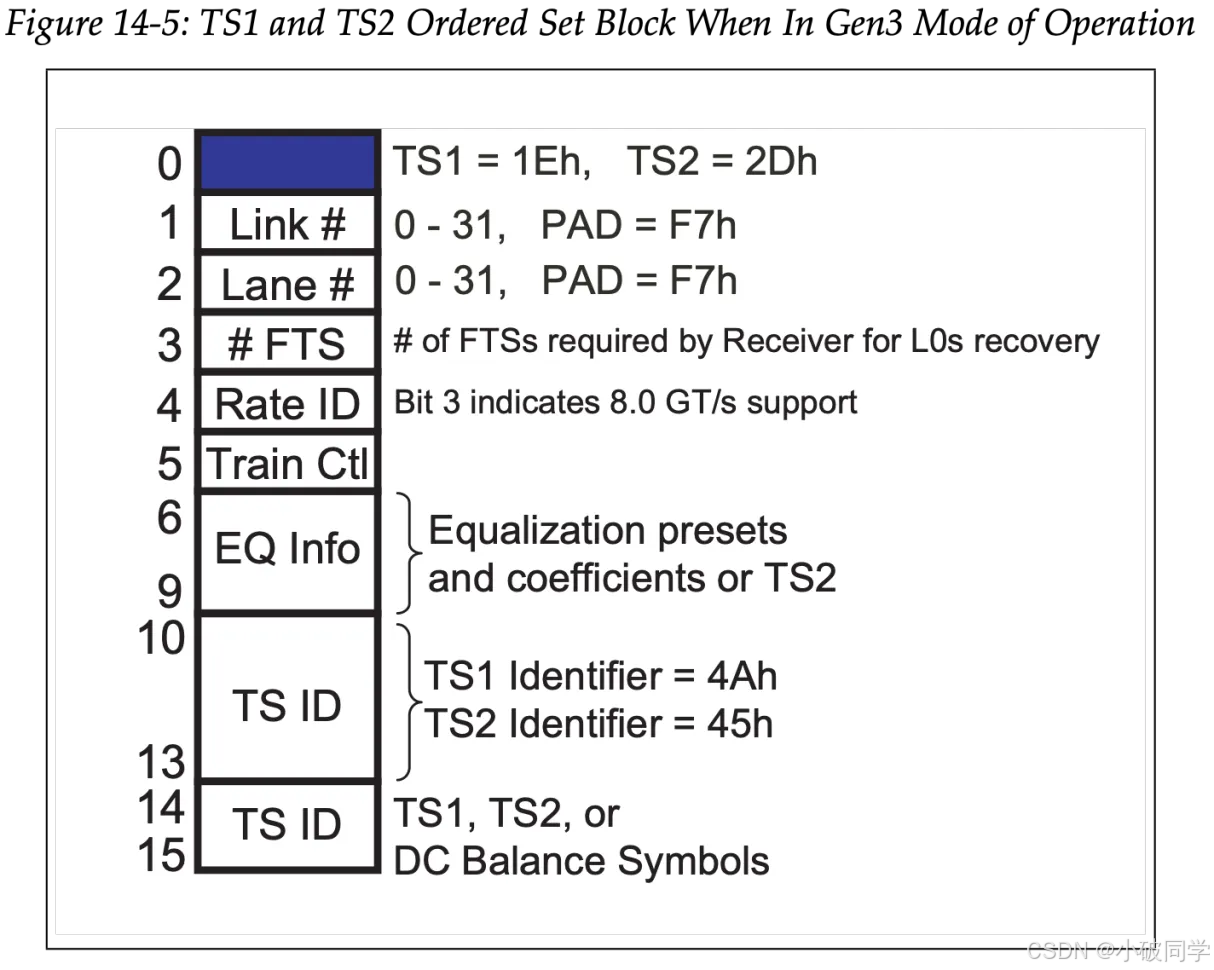

Training Sequence (TS) 是在训练过程中双方交换的一种Ordered Set。TS包含标准TS1/2、EQ TS1/2和Modified TS1/2,由 16 个 Symbol 组成。在 LTSSM 的Polling、Configuration以及Recovery状态中,通信双方会交换TS1/2。TS1/2必须在所有通道上将相应字段(Symbol 3,4,5)设置为相同的值。TS必须连续传递,只可插入SKP,或2.5GT/s以上时可插入EIEOS。

TS2主要用于确认TS1结果和进一步调整链路参数(如EQ)。TS2 是为了使链路两端的设备 LTSSM 同步而设计的握手机制。除非链路两端的设备都准备就绪,双方设备都无法独自进入下一状态。开始发送 TS2 序列是通知对端本方准备就绪的方式。所以一旦设备同时发送(16个)并且接收到(8个) TS2 序列,就代表本方和对端设备都已经就绪,设备可以进入下一状态。

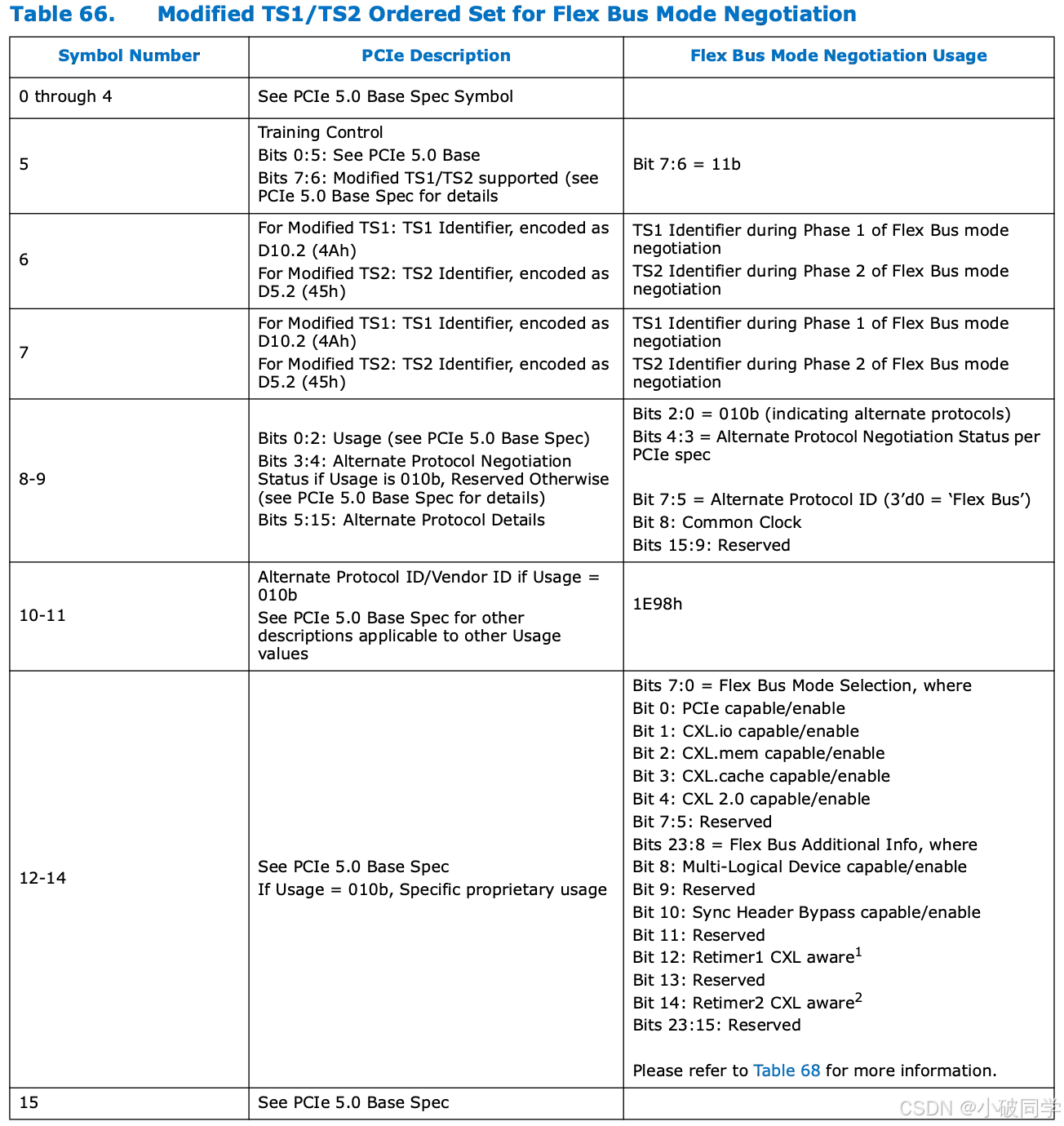

Modified TS用于兼容其他协议如CXL,相比标准TS修改了Symbol6~15。

根据PCIe Gen5/6整理的TS1/2 各Symbol含义如下:

- Symbol 0:

- 2.5 or 5.0 GT/s:COM 字符,接收方通过此实现Symbol lock确认边界,可用于多通道间信号去偏斜。

- 8.0 GT/s or higher: 表示Ordered Set类型,TS1 是 1Eh,TS2 是 2Dh,不加扰。

- Symbol 1 (Link #): 链路编号,在 Polling 状态中使用PAD填充,其他状态中为链路被分配的编号。

- Symbol 2 (Lane #): 通道编号,在 Polling 状态中使用PAD填充,其他状态中为通道被分配的编号。

- Symbol 3 (N_FTS): 表示当前链路速率下,接收方从 L0s 电源状态退出返回 L0 状态所需要接收的快速训练序列(FTS)数量(0-255)。在退出 L0s 状态时,发送方至少会发送 N_FTS 个 FTS。这一过程所需的时间取决于所需 FTS 的数量以及当前的链路速率。发送这么多 FTS 是为了给外部链路观测工具建立比特同步和符号同步留出足够的时间,因为有些外部工具同步所需的时间比较长。

- Symbol 4 (Rate ID): 数据速率标识符。

- Bit 0 - Flit Mode Supported bit (Gen6)

- Bit 5:1 - Data Rates Supported

- 00001b Only 2.5 GT/s supported

- 00011b Only 2.5 and 5.0 GT/s supported

- 00111b Only 2.5, 5.0, and 8.0 GT/s supported

- 01111b Only 2.5, 5.0, 8.0, and 16.0 GT/s supported

- 11111b Only 2.5, 5.0, 8.0, 16.0, and 32.0 GT/s supported

- 10111b 2.5, 5.0, 8.0, 16.0, 32.0, and 64.0 GT/s supported (PCIe Gen6需要协商支持Flit Mode后切换,之前为11111b,即需要先训练到Gen5)

- Others Reserved

- Bit 6 - Autonomous Change(任何带宽改变的请求都是基于电源管理方面的原因而发起)/Selectable De‐emphasis(期望的去加重水平设置)/Link Upconfigure(TS2)/L0p Capability(TS2),区分UP/DP

- Bit 7 - speed_change/SRIS Clocking,区分DP/UP

- Symbol 5 (Training Control): 训练控制字段 ,0 = Deassert,1 = Assert,Bit2:0是互斥的。

- Bit 0 - Hot Reset

- Bit 1 - Disable Link

- Bit 2 - Loopback

- Bit 3 - Disable Scrambling (2.5 or 5.0 GT/s,Gen3后为保留字段)

- Bit 4 - TS1: Compliance Receive (2.5 GT/s 速率可选支持, 其他速率必须支持);TS2: Retimer Present bit

- Bit 5 - TS1: Transmit Modified Compliance Pattern in Loopback (GEN5后用于Loopback,其他情况保留);TS2: Two Retimers Present bit

- Bits 7:6 - Enhanced Link Behavior Control

- 00b: Full Equalization Required

- 01b: Equalization Bypass to Highest NRZ Rate Support

- 10b: No Equalization Needed

- 11b: Modified TS1/TS2 Ordered Sets supported,用于启用Modified TS

- Symbols 6 (Equalization Control):

- 2.5 or 5.0 GT/s,对标准TS1/TS2,为TS1/2标识符;对EQ TS1/TS2(由DSP发送),Bit 7为 1,Bit 6:0包含Transmitter Preset,Receiver Preset Hint等信息。支持 8GT/s 以上速率的端口需要能够接收任意的 TS 类型(包括标准TS 以及 EQ TS),但是如果端口不支持 8GT/s 速率,则不需要接收 EQ TS 的能力。

- 8.0 GT/s or higher,对TS1,Bit 0 为 EC (EQ Ctrl),Bit 1为 Reset EIEOS Interval Count,Bit 6:3表示Tx Preset,Bit 7为Use Prest/EQ Redo。对TS2,Bit 5:4表示EQ Req Date Rate,Bit 7 (Request Equalization) 用于发起EQ,对 USP 也用于申请重新进行均衡,此时,Bit 6 (Quiesce Guarantee) 可能也需要被置起,表示只要重新均衡的速度够快,那么所耗费的时间不会导致如CPL timeout等问题(返回 L0 的时间在 1ms 以内)。

- 32.0 GT/s or higher,对EQ TS,Bit 0 为 Transmitter Precode Request。

- Symbols 7‐9 (Equalization Control):

- 2.5 or 5.0 GT/s,TS1/TS2 的标识符

- 8.0 GT/s or higher,对TS1提供Coefficients值或在EQ Phase 1提供FS/LF。

- Symbols 10‐13 : TS1/TS2 的标识符

- Symbols 14‐15 (DC Balance):

- 2.5 or 5.0 GT/s,TS1/TS2 的标识符,因为 DC 均衡已经由 8b/10b 编码完成。

- 8.0 GT/s or higher,用于本通道上 DC 均衡。发送方必须在每个通道上独立地追踪当前所有正在被发送的加扰后的 TS1/2 的实时 DC 均衡(Running DC Balance)情况。实时 DC balence是指目前发送的 1 和 0 之间的数量差,各个通道必须能够在收发两个方向上追踪 0 和 1 的数量差值,最大支持的差值为 511。这些计数器在记满后保持不变,但是会更新差值减小的变化。举例而言,如果计数器记录到发送的 1 数量比 0 多 511 个,此后无论发送多少个 1,计数值仍然停留在 511。然而,如果发送了 2 个 0,那么计数器会减少到 509。Symbol 14 和 15 的数值由以下算法决定:

- 如果在Symbol 11 结束时,实时DC balance > 31,如果需减少 1 的数量,则Symbol 14 = 20h,Symbol 15 = 08h。如果需减少 0 的数量,那么Symbol 14 = DFh,Symbol 15 = F7h。

- 如果实时DC balance > 15,那么Symbol 14传输正常TS1/2标识符,Symbol 15 = 08h 以减少 1 的数量,或者Symbol 15 = F7h 以减少 0 的数量。

- 如果不需要修改,Symbol 14-15传输TS1/2标识符。

- DC 均衡计数器将在退出电气空闲状态时,或者在一个数据块之后收到 EIEOS 时复位。

- Symbols 14-15将绕过加扰,来保证发送的是预期的Symbol。

- Sync Header和Symbol 0(除EIEOS)的1和0数量一致,不影响DC均衡。

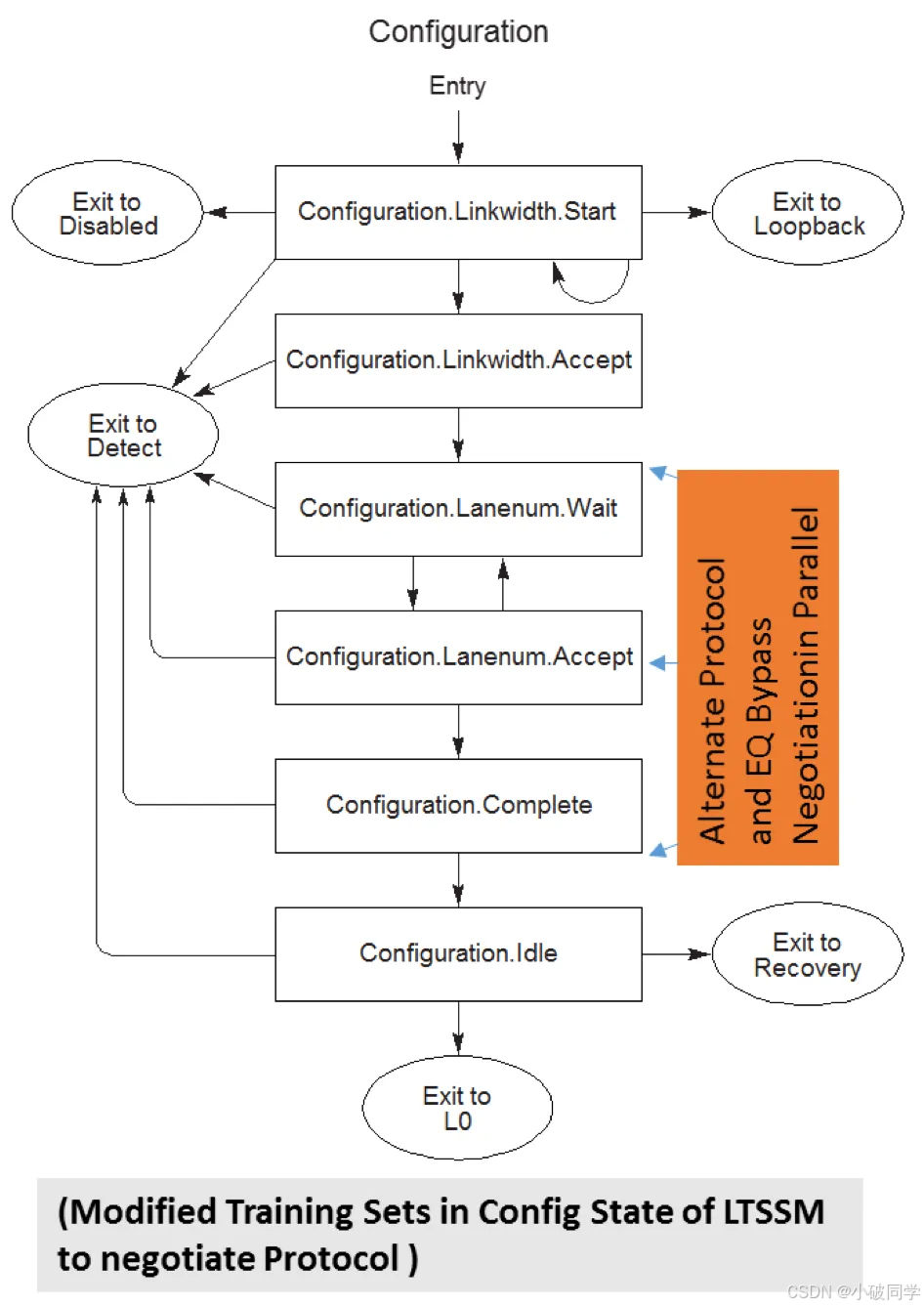

APN (Alternate Protocol Negotiation)

PCIe Gen5新增支持。CXL link training基于APN,采用Modified TS1/2。

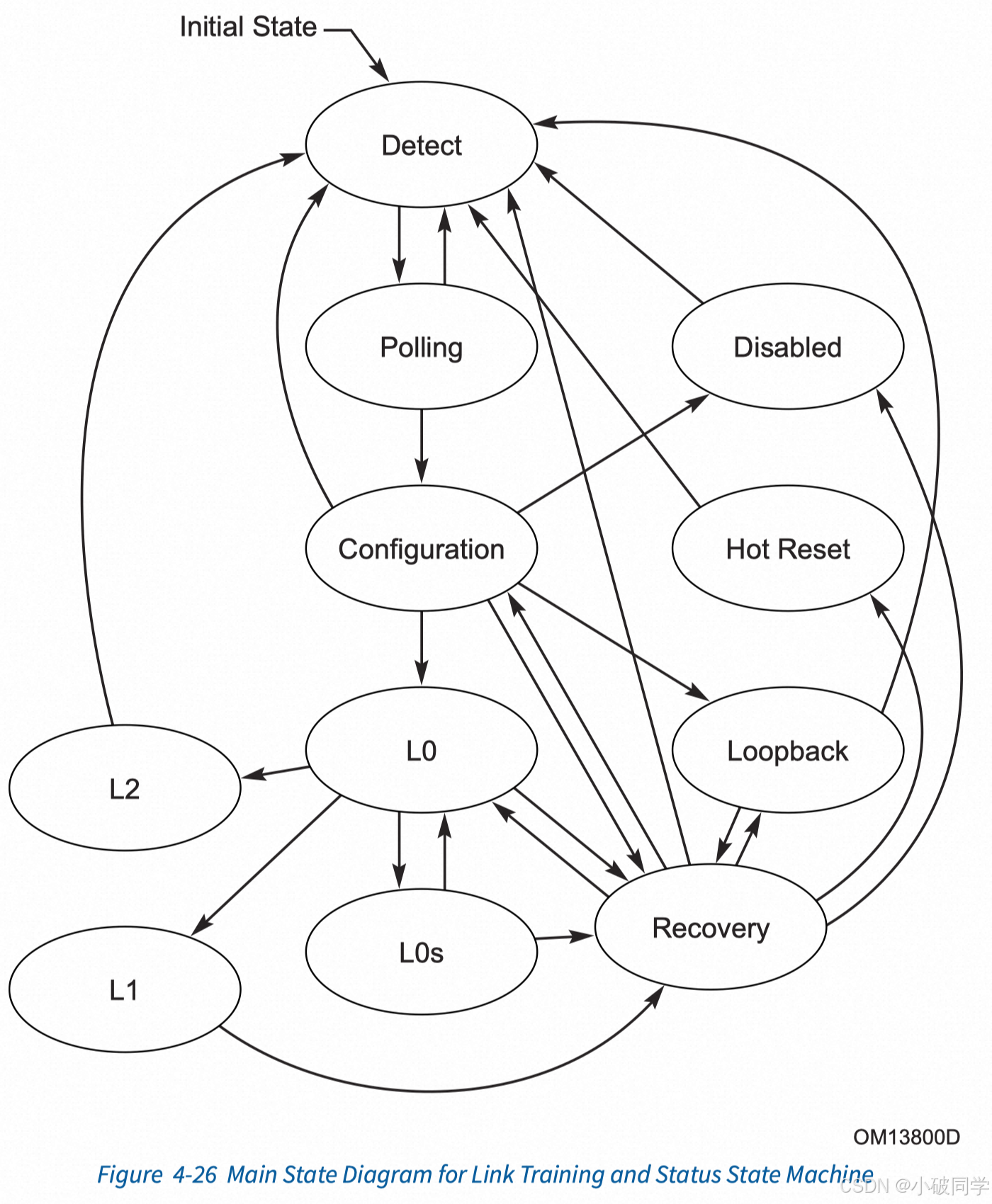

LTSSM (Link Training and Status State Machine)

LTSSM服务于单个Link,共有11个顶层状态,正常状态Detect => Polling => Configuration => L0。第一次训练必须进Gen1 L0。PCIe Gen5 LTSSM主要状态跳转示意图如下。

Detect:复位后初始状态,检测链路对端其他PCIe设备存在

Polling:发送方以2.5GT/s速率依次发送TS1/TS2序列以实现以下目标:

- 位锁定(Bit Lock)

- 字符锁定(Symbol Lock, Gen1/2)或块对齐(Block Alignment, Gen3+)

- 校正Polarity Inversion,如有必要

- 确定Lane支持的Data Rates

- 在测试条件下,发起兼容性测试序列

Configuration:上下游设备以2.5GT/s速率交换TS1/TS2序列以实现以下目标:

- 协商Link Width

- 分配Lane编号

- 可选校正Lane Reversal

- 补偿Lane-to-Lane De-skew

- 可以禁用加扰和设置N_FTS

L0:链路全功能正常状态(Normal and Full-Active State),切速必须在进入Recovery后

Recovery:用于Re-Training,会重新进行比特和字符/块锁定

L0s:由硬件控制的 ASPM 低功耗状态

L1:相对于L0s状态,L1状态下的功耗更低,恢复时间更长,需双方协商进入

L2:L2状态下的链路功耗更低,此时设备主电源切断,只保留辅助电源Aux Power,关闭链路其他功能

Loopback:主要用于测试,回环发送TS1序列测试链路完整性

Disable:链路禁用,此时发送端处于电气空闲态,接收端处于低阻态

Hot Reset:软件可以通过置位Bridge_Control_Register.Secondary_Bus_Reset位,复位链路。