基于RFSOC49DR-16收16发 PCIE4.0 X8 射频采集卡

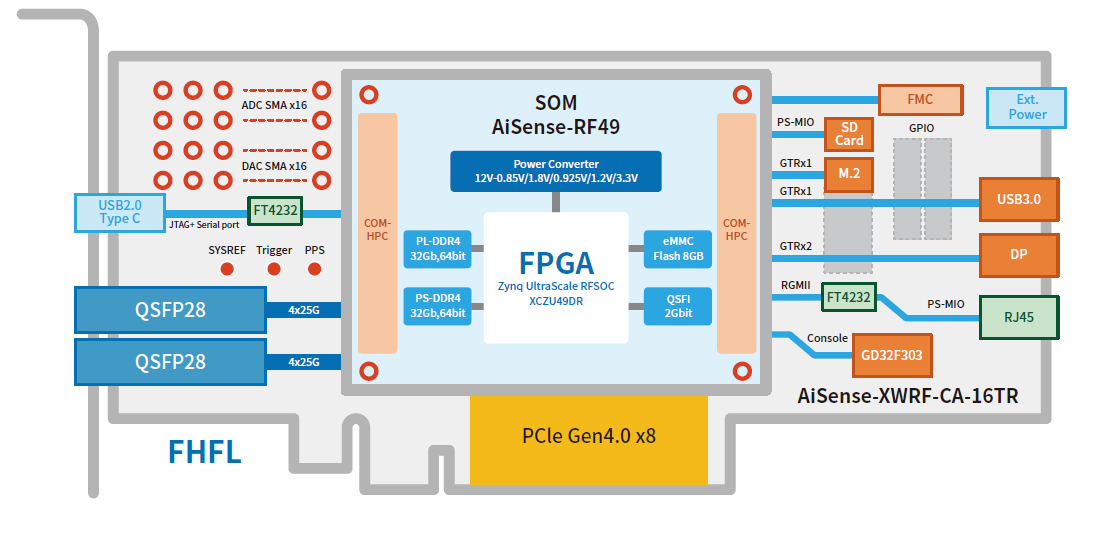

基于RFSOC49DR-16收16发 PCIE4.0 X8 射频采集卡是是一套无线电射频数据采样转换开发板及配套开发平台,该开发板包括:SOM 核心板和底板。其中 SOM 核心板是一个最小系统,包括 AMD 公司的Zynq UltraScale+RFSOC 第 3 代系列 XCZU49DR-2FFVF1760I FPGA、时钟、电源、内存以及 Flash。

底板是标准的全高全长 Gen4.0 x8 的 PCIE 卡,由底板引出了 DP 显示、USB3.0、USB2.0、RJ45、QSFP28、SMA、串口、存储接口、SATA3、 M.2 等丰富的外设接口,同时还配置了 GNSS( GPS+北斗)模块,而且还配有一个 FMC 连接器和 1 组 GPIO 通用插座,可通过此连接器进行功能扩展。

该开发平台支持 16 路 14 位 ADC,最大采样速率可达 2.5GSPS,16 路 14 位 DAC,最大采样

速率为 9.85GSPS, 实现射频直采,可以降低射频信号处理链的复杂性并拥有更低的功耗。应用于5G 及 LTE 无线技术、有线电视接入、测试测量、早期预警雷达以及其他高性能 RF 应用需求。

产品规格

FPGA:Zynq UltraScale+ RFSOC XCZU49DR

内置存储

· 2Gbit QSPI 存储,用于启动 FPGA

· 8GB eMMC,用于 SOC 系统 Boot-Up

FPGA内存

· PL DDR 支持 64 位 2400MHz,4GB 容量

· PS DDR 支持 64 位 2400MHz,4GB 容量

主机接口

· PCle Gen4.0 x8 接口直连 FPGA, 与 PCle 硬核 IP相连

用于 2x100G QSFP2 端口

· 2x100G QSFP28 光口,可通过 MPO 扩展为 2.5G/

10G/40G 等速率光信号

时钟接口

· 板载 HMC7044 用于 AD 通道参考时钟和同步时钟

· 提供外接 PPS 同步时钟触发,可进行板卡或者数据采集通道的扩展

扩展外设接口

· 千兆 RJ45、USB2.0、USB3.0、存储接口、SATA3、

M.2、FMC 扩展等

·JTAG 和串口,用于 FPGA 在线调试

定位功能

· 配置了 GNSS (GPS+北斗)模块

冷却系统

· 标准:单槽位主动散热

管理控制器 (BMC)

· 电压、电流、温度监控

· 电源时序管理和复位

· 现场升级

· FPGA 配置和控制

· 时钟配置

· 低带宽 BMC-FPGA 通信与 SM-Bus 总线链接

· 防止拷贝配置文件

电源

· 来自 PCle 插槽的板载电源

· 支持外接 +12V ATX 接口电源

· 功耗与应用有关

· 最大功耗约 75W

环境

· 工作温度: -40℃ 至 85℃