Design Compiler:层次模型(Block Abstraction)的简介

相关阅读

Design Compiler![]() https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12738116.html?spm=1001.2014.3001.5482

Design Compiler的综合策略大致可以分为三种:一种是自上而下(Top-Down),即一次性读入整个顶层设计及所有子模块,应用顶层约束,然后统一综合,这适合设计规模较小或计算资源充足时;一种是自下而上(Bottom-Up),即各个子模块单独约束、单独综合,最后再综合顶层设计,这适合超大设计或受到内存限制时;两种策略的结合是一种更常见的综合方法。

本文将讨论在自下而上综合过程中使用层次模型或者说抽象块(Block Abstraction)的情况,与此对应的是在自下而上综合过程中不使用层次模型,即使用完整的子模块模型(即使子模块已提前综合,这也会导致内存需求上升)。

曾经的层次模型分为两种:最初的接口逻辑模型(ILM, Interface Logic Model)和以及抽象块,但自2014版本后,接口逻辑模型不再被Design Compiler、IC Compiler等工具支持。

对于接口逻辑模型,模块会被建模为一个不完整的模块,其中仅包含该模块所需的接口逻辑,以及用户手动与接口逻辑关联的逻辑,所有内部逻辑都会被移除。

抽象块是接口逻辑模型的拓展,与接口逻辑模型使用单独的ddc文件表示移除了内部逻辑的模块不同,它将完整的模块和接口逻辑一起保存在同一个ddc文件中,但接口逻辑会被标记,如果指定使用抽象块,只加载接口逻辑;如果不指定,则还是使用完整的模块。

需要注意的是,IC Compiler只能使用在IC Compiler中创建的抽象块,而Design Compiler可以使用在Design Compiler以及IC Compiler中创建的抽象块。

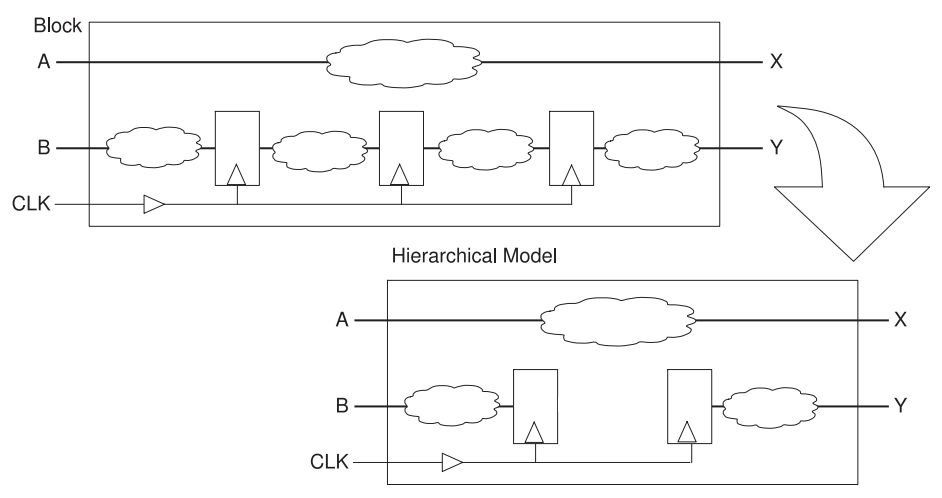

图1展示了一个抽象块的转换过程,其中与接口时序路径相关的逻辑被保留(in2reg、reg2out、in2out),而触发器间时序路径的逻辑则不考虑(reg2reg)。

图1 抽象块的转换

默认情况下,抽象块包含以下网表对象:

- 输入端口到输出端口、输入端口到触发器以及触发器到输出端口这三种数据路径上的单元、线网。

- 连接到接口触发器的时钟路径(包括主时钟到生成时钟之间的逻辑)及其最大和最小的时钟路径上的单元、线网。

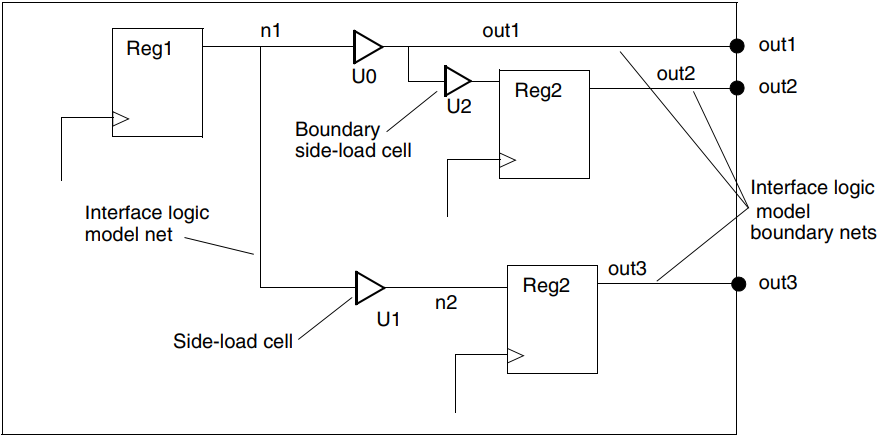

- 接口线网上的附加载单元(Side-load Cell),图2展示了附加载单元的定义。

图2 附加载单元

从图2中可以看出,附加载单元属U1于触发器到触发器数据路径,但由于其影响了接口线网的寄生参数,因此也被保留在抽象块中。单元U0既可以看做触发器到触发器数据路径的一部分,也可以看做触发器到输出端口数据路径的一部分,因此也被保留在抽象块中。

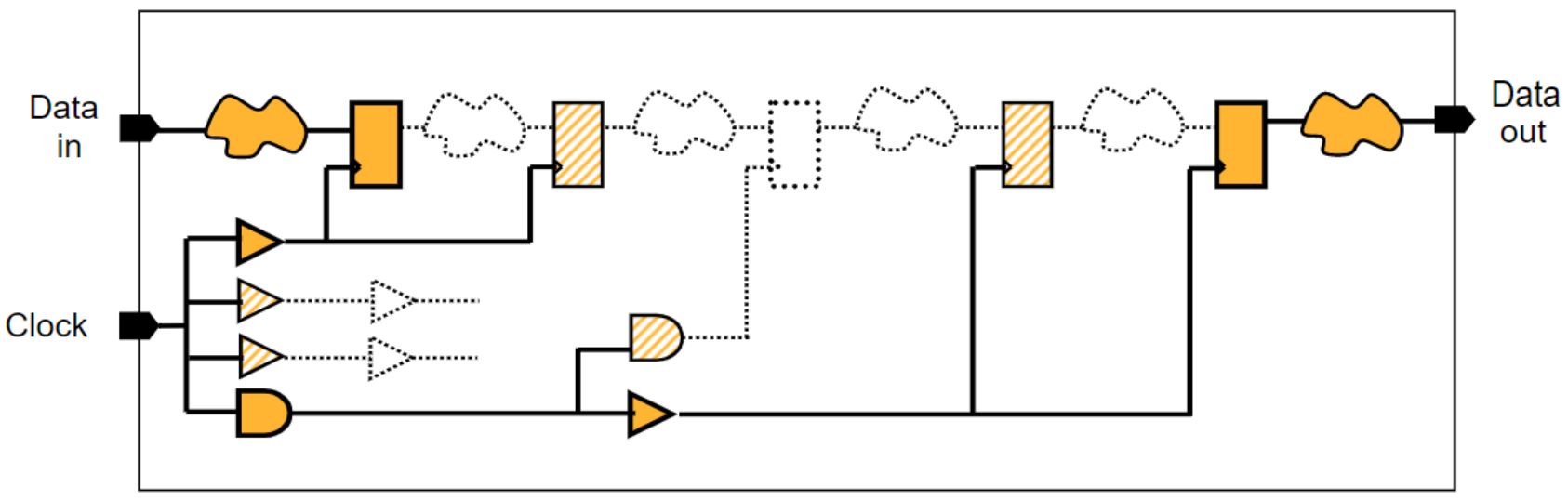

图3展示了抽象块中包含的元素,着重强调了时钟树。填充部分是接口数据路径和时钟路径上的元素,斜线部分是附加载单元,虚线部分的元素则不会包含在模型中。

图3 抽象块中包含的元素