STM32F4—电源管理器

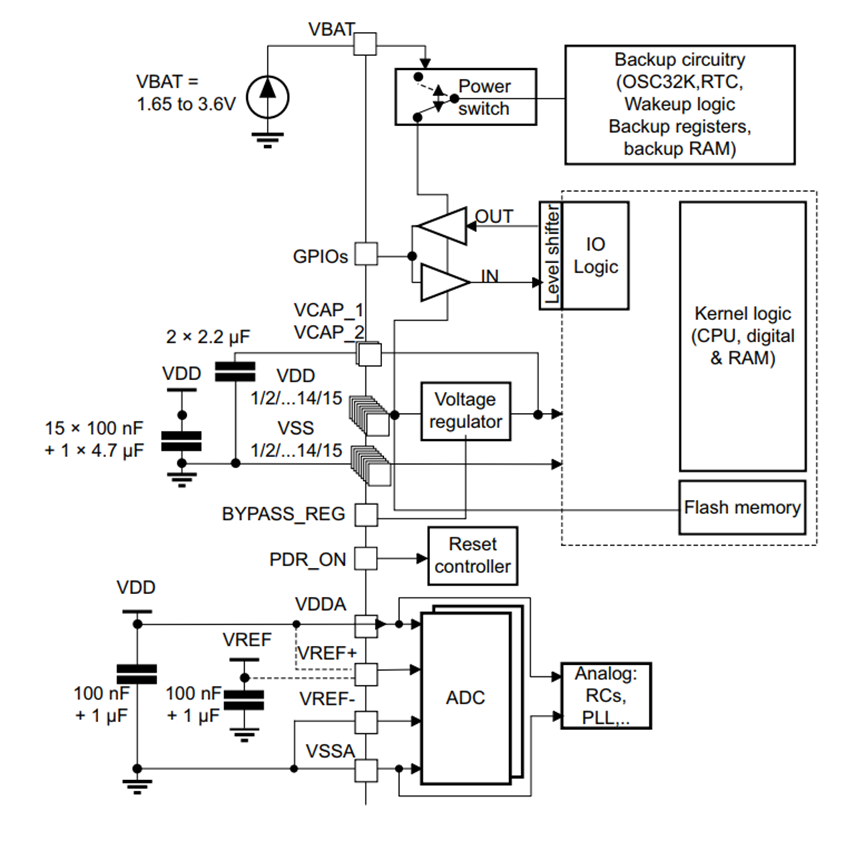

Power supply schemes

Power supply supervisor

Internal reset ON

有PDR_ON pin的MCU,PDR_ON pin被拉高的时候电源监视器被使能。没有PDR_ON pin的MCU默认一直使能。

内部集成了power-on reset (POR) / power-down reset (PDR)

POR(上电复位):当设备从断电状态接通电源时,POR电路会检测电压上升,并生成一个复位信号,确保芯片在电压稳定前保持复位状态,避免因电压不稳定导致的错误操作。

PDR(掉电复位):当电源电压异常下降(如突然断电)时,PDR电路会强制设备复位,防止电压不足时出现不可预测的行为。

Brownout Reset (BOR)(欠压复位)

当电源电压暂时跌落(但未完全断电,例如电压波动)并低于某个阈值时,BOR电路会触发复位。这避免了设备在电压不足时运行异常(如程序跑飞、数据错误)。

上电的时候,POR/PDR激活,保证MCU在达到1.8V上电。当达到 1.8 V的 POR 阈值水平后,选项字节加载过程开始,确认、修改默认的 BOR阈值水平,或者永久禁用 BOR。STM32F407ZG提供三个 BOR 阈值。

当电压低于阈值的时候,系统处于复位模式。

MCU里有一个programmable voltage detector (PVD),当VDD/VDDA低于或者高于PVD阈值的时候会产生一个中断。中断服务程序可以产生一个警告信息让MCU进入安全状态。PVD由软件使能。

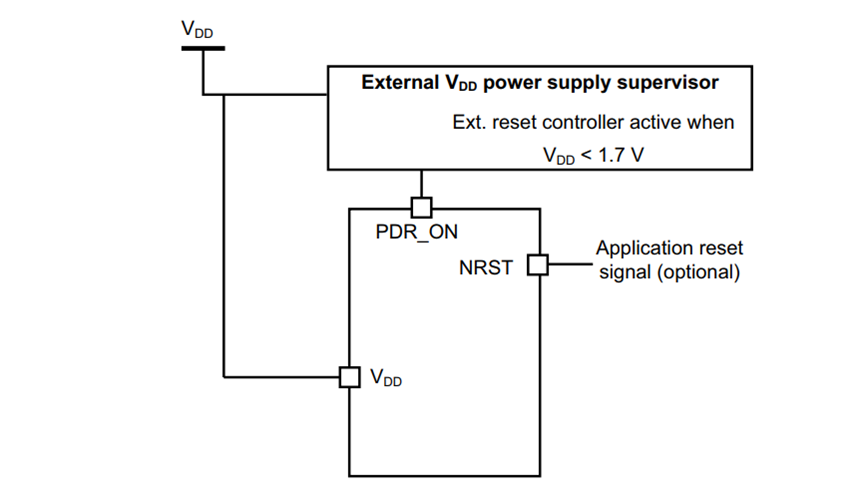

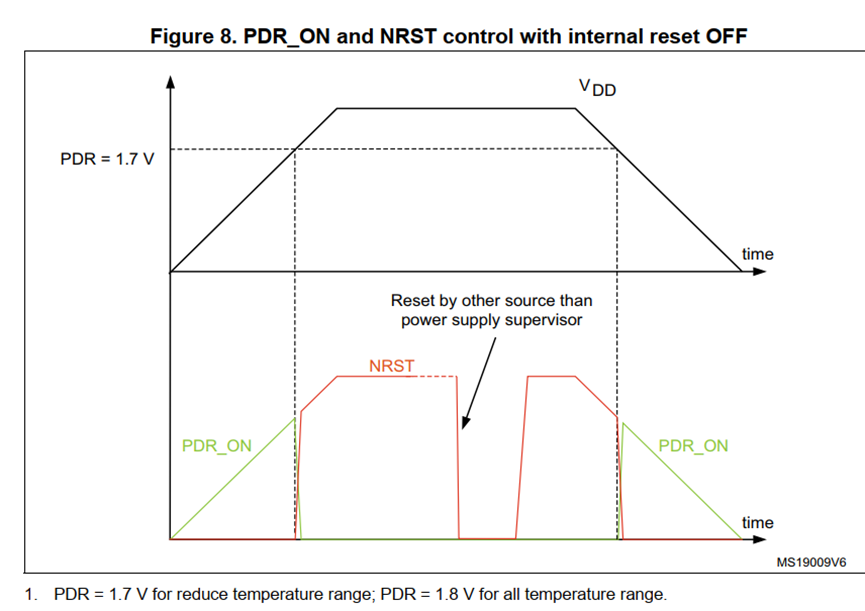

Internal reset OFF

关闭内部reset时,需要一个外部电压监视器,当供电电压低于VDD时,保证MCU进入复位模式。

当VDD低于1.8V时,MCU保持复位状态(硬件强制复位)。当运行温度在0~70°C时阈值可能会降至1.7V。

当内部的reset关闭之后,POR、PDR、BOR、PVD都会失能。并且VBAT 功能已不可用,VBAT 引脚应连接至VDD。这样做的优点是可以将系统的功耗降低。

芯片的内部复位功能被关闭(如通过选项字节禁用BOR/PDR),此时仅依赖外部复位电路或手动控制。

Voltage regulator mode

电压管理器有四种模式

Regulator ON打开时,主管理器模式(MR)、低功耗模式(LPR)、Power-down下电和Regulator OFF。

Regulator ON

MR是标准的管理模式,在此模式下,综合考虑最大频率和动态功耗对电压进行比例缩放。

LPR 被用在stop模式下,LP regulator mode由软件配置

Power-down用于Standby模式,只有进入Standby模式是才会被激活。调节器输出处于高阻抗状态,内核电路断电,从而实现零功耗。寄存器和SRAM将被复位。

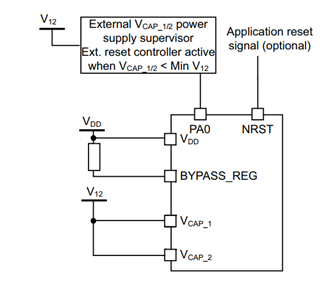

Regulator OFF

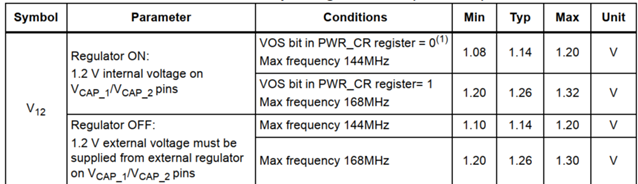

当管理器被关闭的时候,需要一个外部电压V12为VCAP_1 and VCAP_2供电。由于内部电压缩放不由内部管理,因此外部电压值必须与目标最大频率相匹配。

VCAP_1 and VCAP_2供电1.14V是最大频率144Mhz,VCAP_1 and VCAP_2供电1.2V最大频率168Mhz。

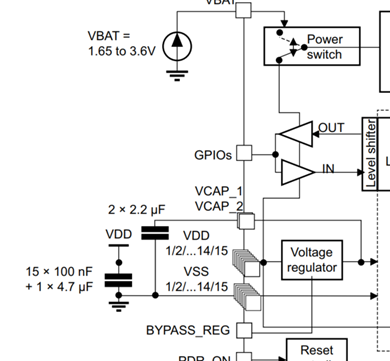

Regulator OFF 时VCAP_1 and VCAP_2的两个2.2uF的电容替换成两个100nf电容。

当调节器处于关闭状态时,V12将不再进行内部监控。此时应使用外部电源监控器来监控逻辑电源域的 V12。为此,应使用 PA0 引脚,并将其用作 V12 电源域的上电复位信号。

当调节器处于关闭状态时:

1、PA0不能被当做GPIO使用,它直接控制 V12 逻辑电源域(V12 logic power domain) 的复位功能,且该电源域 不受 NRST 主复位引脚控制。

2、PA0为低电平的时候,,芯片在 上电复位(Power-On Reset, POR)期间会禁用DEBUG模式。因此,若需支持 复位期间(或复位前)的调试连接,必须对 PA0 和 NRST 引脚进行独立管理。

3、standby不可用

管理器关闭的时候需要考虑一下几点:

VDD必须高于VCAP_1 and VCAP_2,避免电流倒灌,电流从 VCAP 引脚反向流入 VDD 电源域,损坏内部电路。

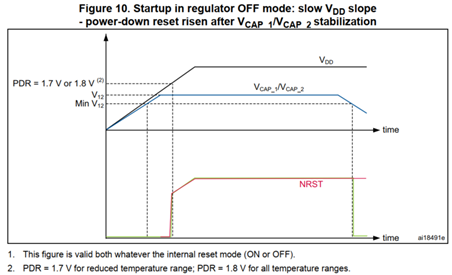

如果VCAP_1 and VCAP_2达到V12最小值的时间快于VDD达到1.8V的时间。PA0会保持低电平,直到VDD和VCAP_1 and VCAP_2达到各自的最小值。

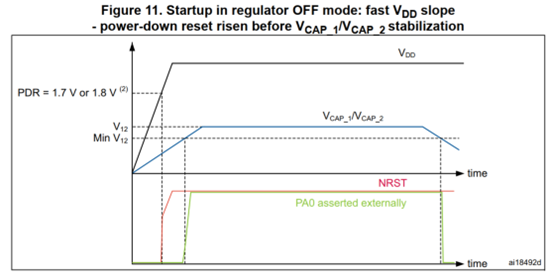

如果VCAP_1 and VCAP_2达到V12最小值的时间慢于VDD达到1.8V的时间。需通过外部强制拉低 PA0引脚来确保芯片安全初始化

当系统满足以下两个条件时,PA0引脚必须复位:

VCAP_1/VCAP_2电压 < V12最小值(如1.2V)

VDD电压 > 1.8V(保持有效供电)