【I】题目解析

目录

单选题

多选题

判断题

单选题

1.reg[7:0]A; A=2'hFF;则A=()

A.8'b11111110

B.8'b03

C.8'b00000011

D.8'b11111111

C

2'hFF实际上等效于2位二进制2'b11,赋值给8位寄存器A之后,低位赋值,高位补0

A=8'b00000011

AMD FPGA器件中URAM的大小为()

A.18kb

B.36KB

C.288kb

D.320kb

C

URAM(Ultra RAM)是一种高性能片上存储器,在AMD Xilinx FPGA器件中,URAM的大小同城为288kb,配置为4K*72bit的存储单元,其容量是Block RAM的八倍

3.FPGA中的分布式RAM是由()构成

A.进位链

B.Block RAM

C.LUT

D.MUX

C

FPGA中的分布式RAM(Distributed RAM)是由查找表(LUT)构成的存储资源,相比于Block RAM等其他乐行的RAM,分布式RAM可以根据需要灵活地分布在FPGA的各个区域,适合小规模、不规则的存储需求

进位链主要用于实现加法等算术运算;

Block RAM是FPGA专用大容量存储模块;

多路选择器MUX主要用于数据选择;

LUT本质上是一种数据存储逻辑单元,通过将LUT配置乘特定模式可以实现RAM的功能

【FPGA】LUT如何实现组合逻辑、时序逻辑_fpga lut-CSDN博客

4.关于AMD FPGA Slice说法错误的是()

A.SliceX没有存储功能,也没有进位链

B.SliceM除具有存储功能外,还包含进位链、多路复用器、查找表LUT和可变长的移位寄存器

C.SliceL具有存储功能,但没有进位链

D.Slice中含有多路复用器

A

Slice是AMD Xilinx FPGA的基本逻辑单元,由查找表(LUT)、寄存器、进位连和多路复用器(MUX)等组件构成,包括SliceX、SliceM和SliceL三种不同的类型。

SliceX具有存储功能和进位链,适用于累加等运算和结果存储,A错

SliceM具有存储功能、进位链、多路复用器、查找表和可变长移位寄存器,适用于数字信号处理算法卷积运算和数据滤波等操作,B对

SliceL仅具有存储功能,适用于简单逻辑处理和数据存储,C对

Slice中包含多路复用器,D对

【基本知识】CLB、Slice、logic cell、LUT... - 要努力做超人 - 博客园

5.'b00110 ^ 'b10000的结果为()

A.'b10110

B.'b01001

C.1'b1

D.1'b0

A

异或,相同位为0,不同位为1

00110

10000

10110

6.十进制负整数-10的8bit有符号数表示正确的是()

A.8'h76

B.8'hF6

C.8'hF5

D.8'hA

B

+10

0000 1010

-10

按位取反,末尾+1

1111 0101

1

1111 0110

8'hF6

7.以下运算符,()优先级最低

A. ? :

B. + |

C. ||

D. <<

A

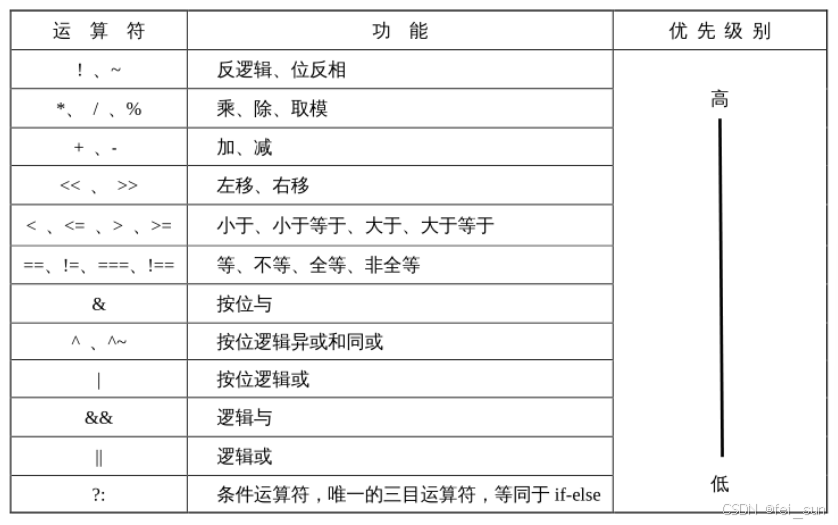

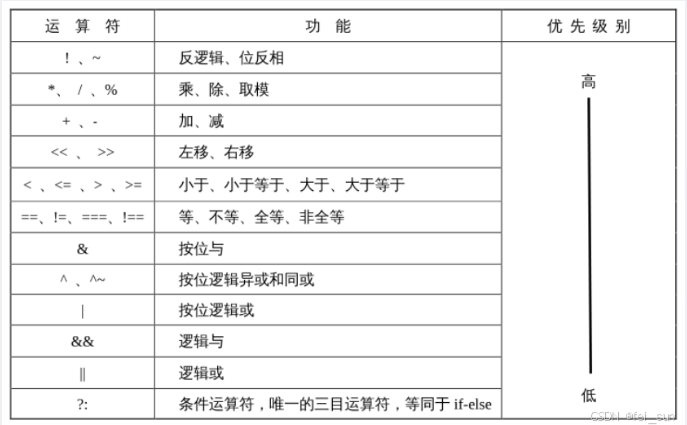

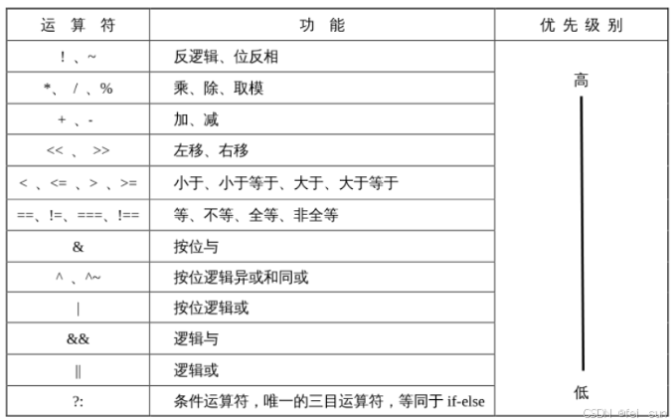

! ~ 高(从高到低) * / % + - << >> < <= > >= == != === 1=== & ^ | && || ?: 低

【Verilog】基于Verilog HDL的FPGA设计基础-CSDN博客

8.在下列程序中,always状态将描述一个带异步Nreset和Nset输入端的上升沿触发器,从选项中找出空括号内应填入的正确答案

always@()

if(!Nreset)

Q<=0;

else if(!Nset)

Q<=1;

else

Q<=D;

A.negedge Nset or posedge clk

B. negedge Nreset or posedge clk

C. negedge Nreset or negedge Nset

D. negedge Nreset or negedge Nset or posedge clk

根据要求实现一个带有异步复位(Nreset)和异步置位(Nset)的上升沿触发器,异步信号低有效,需要直接包含在敏感列表中,即敏感列表应该包括:

1. 异步复位信号(Nreset)下降沿;

2. 异步置位信号(Nset)下降沿;

3. 时钟信号(clk)上升沿。

同时包含三个触发条件,选择D

特性

同步设计

异步设计

敏感信号类型

仅时钟边沿(

posedge/negedge)时钟边沿 + 电平敏感信号(如复位、使能)

敏感列表约束

单一时钟边沿,不可混合其他信号

允许多个异步信号电平变化

复位实现方式

同步复位(通过

if条件判断)异步复位(直接敏感列表触发)

时序控制

严格依赖时钟,时序确定性高

依赖信号电平,时序不确定性高

综合结果

综合为寄存器,时序逻辑

可能综合为组合逻辑或带异步控制的时序逻辑

9.线网中的值被解释为无符号数。在连续赋值语句中,assign addr[3:0]=-3。addr被赋予的值是()

A.4'bxx11

B.4'bzz11

C.4'b0011

D.4'b1101

D

+30011

-3

按位取反,+1(补码)

1100

1

1101

10.关于保持时间说法正确的是 ( )

A. 指时钟采样沿稳定之前,数据保持稳定的时间

B. 当保持时间不满足要求时,可以降低时钟频率解决

C. 当保持时间不满足时,可以调整数据走线延时解决

D. 指时钟采样沿稳定之后,数据保持稳定的最长时间

C

保持时间是指时钟采样沿到来之后,数据需要保持稳定的时间,A 错误;

降低时钟频率会使时钟周期变长,数据的建立时间更容易满足,但对保持时间没有帮助,因为保持时间与时钟周期无关,B 错误;

当保持时间不满足要求时,可以通过调整数据走线延时来解决。例如,增加数据路径的长度或插入缓冲器等,使数据到达采样点的时间延迟,从而满足保持时间的要求,C 正确;

保持时间是指时钟采样沿稳定之后,数据保持稳定的最短时间,D 错误

11.Verilog代码中错误的注释符是()

A. //

B. ///

C. /*...*/

D.#

D

在Verilog语言中,通常使用符号//或///实现单行注释,使用符号/*...*/实现多行注释。符号#是VHLDL语言的注释方法,而非Verilog语言的注释方式

12.SignalTap文件后缀是()

A.cdc

B.stp

C.lpf

D.sdc

B

SignalTap是Intel Altera FPGA开发工具Quarter Prime中的嵌入式逻辑分析仪,用于实时捕捉和分析FPGA内部信号,其配置文件的标准后缀为.stp(SignalTap Project)

.cdc为时钟域交叉(Clock Domain Crossing)约束文件;

.lpf为布局与布线约束文件(Lay);

.sdc为Synopsys设计时序约束文件(Synopsys Design Constraint)

13.在Verilog语言中,下列哪个不属于分支语句()

A.if...else

B.case

C.casez

D.repeat

D

if...else语句是典型的分支语句,根据条件判断执行不同的代码块;

case和casez语句根据表达式的值执行多个分支中一部分代码块,casez在进行比较时会将高阻态z值视为无关项,均属于分支语句;

repeat语句用于重复一段代码,属于循环语句;

14.下列EDA软件中,哪一个不具有逻辑综合功能()

A.Vivado

B.Quarter II

C.Synplify

D.ModelSim

D

Vivado是Xilinx FPGA开发套件,集成了逻辑综合、实现(布局布线)和仿真功能;

Quartus II是Intel Altera FPGA 开发工具,同样具备逻辑综合能力;

Synplify是Synopsys推出的专业逻辑综合工具,主要关注于将HDL代码转换为门级网表

Modelsim是Mentor Graphics的仿真工具,仅用于验证设计功能,不具备逻辑综合能力

15.下列属于Verilog HDL非开源仿真工具的是()

A.IceStorm

B.Icarus Verilog

C.Questasim

D.Yosys

C

IceStorm是Lattice冰河系列FPGA的开源工具链,包含仿真等功能

Icarus Verilog是支持Verilog代码编译仿真的开源Verilog HDL仿真工具

QuestaSim是Mentor Graphics公司开发的Verilog HDL商业仿真软件,属于非开源仿真工具

Yosys是支持仿真的Verilog开源综合工具

16.在FPGA中实现FIR滤波器时,必须要使用哪种资源()

A.DSP

B.LUT

C.SRL

D.BRAM

B

DSP模块是用于高速乘法和累加专用硬件,虽然FIR滤波器使用DSP可以显著提升性能,但是小规模FIR滤波器完全可以由LUT实现;

LUT是用于实现组合逻辑的FPGA基本逻辑单元,FIR滤波器的核心运算是乘法和累加,其中乘法器可以由LUT或DSP模块实现,控制逻辑和其他赋值功能仍然需要LUT支持,因此LUT是实现FIR滤波器的必须资源;

SRL用于实现数据延迟功能,可以使用普通寄存器替代

BRAM用于数据存存储功能,可以使用普通寄存器替代

17.AMD的1个可编程逻辑(CLB)内共有几个LUT()

A.1

B.2

C.4

D.8

D

AMD Xilinx FPGA的可编程逻辑块(CLB)结构中,每个CLB由两个Slice(SliceL和SliceM)构成,每个Slice包含4个6输入LUT(可配置32*1位RAM或移位寄存器)

所以,每个CLB共包含8个LUT

18.选出下列运算符中优先级最低的一个()

A.!

B.&

C.||

D.<<

C

19.下列不属于底层可编程逻辑(CLB)的基本构成元素的是()

A.查找表(LUT)

B.乘法器(DSP)

C.寄存器(FF)

D.进位链(CARRY4)

B

可编程逻辑块(CLB)是FPGA的底层单元,不同厂家的CLB具体结构有所不同,但是通常都包含查找表(LUT)、寄存器(FF)和进位链(CARRY4)等基本构成元素,其中LUT用于实现组合逻辑功能,FF用于实现时序逻辑功能和数据存储,CARRY4用于实现快速进位运算,DSP通常是独立于CLB的高速乘法运算专用资源,不属于CLB构成部分

20.关于设计文件的代码注释率描述正确的是()

A.无需进行代码注释

B.代码注释符是'/'

C.注释是为了更好的维护代码

D.代码注释会干扰编译器

C

多选题

1.FPGA DSP资源可以完成哪些功能

A.加法和减法运算

B.乘累加运算

C.乘法运算

D.逻辑运算

ABC

DSP模块是FPGA的专用硬件资源,主要用于高效实现高性能算术运算,典型功能包括:

加法和减法运算:DSP模块内置加法器/减法器,可以直接实现高速加减运算,常用于FIR滤波器的累加部分

累乘加运算(MAC):DSP模块通过级联乘法器和累加器实现乘累加匀速那,常用于傅里叶变换FFT和卷积运算

乘法运算:DSP模块包含专用乘法器,可以实现高速定点或浮点乘法,匀速效率远高于LUT

DSP模块的主要功能包括加法和减法运算、乘法运算,逻辑运算由查找表LUT资源完成

2.可以用于FPGA功能仿真的语言有哪些()

A.Verilog

B.SystemVerilog

C.Perl

D.SystemC

ABD

FPGA功能仿真主要使用硬件描述语言(HDL)或专用仿真语言,Verilog是主流的HDL语言,广泛应用于FPGA设计和仿真,所有FPGA工具链(例如Vivado和Quartus)都支持Verilog语言;

SystemVerilog是Verilog的扩展,增加面向对象特性和验证功能(如约束随机测试),广泛应用于复杂设计验证;

Perl是脚本语言,主要应用于自动化任务(如测试脚本生成),不直接应用于硬件行为描述和仿真;

SystemC是C++的扩展,主要应用于系统级建模和硬件-软件协同仿真,常用于ASCI设计,也可以用于FPGA高层次验证

3.对于FPGa管脚输入信号的建立时间()和保持时间(

)约束,以下说法正确的是()

A.保持时间约束可以通过调整数据路径延时解决

B.建立时间约束仅与时钟频率有关

C.静态时序分析工具会同时验证和

是否满足

D.异步时钟域的/

约束比同步时钟域更复杂

ACD

当保持时间不满足时,可通过增加数据路径延时(如插入缓冲器)使数据延迟到达,确保时钟沿后数据稳定时间满足

要求;

建立时间约束与时钟频率、数据路径延时、时钟抖动等因素相关,并非仅由时钟频率决定;

静态时序分许(STA)工具会分别检查所有路径的建立时间和保持时间是否满足约束,任何一项违例都会报错;

异步时钟域需要考虑时钟间的相位差和抖动,通常需要特殊处理(如异步FIFO和打拍器),约束更为复杂

4.下列哪些说法是错误的()

A.FPGA的配置程序在器件断电后消失

B.时钟沿触发的触发器本质上也是组合器件组成的

C.TTL与CMOS电平可以直接互连

D.锁存器是边沿触发器件

BCD

FPGA通常采用SRAM工艺存储配置数据,数据断电后丢失,需要通过外部Flash重新加载;

触发器是时序逻辑器件,由门电路构成的锁存器和时钟控制电路组成,本质上依赖时钟边沿触发,与组合逻辑有本质区别;

TTL输出高电平(2.4V)与COMS输入高电平阈值(3.5V~5V)不匹配,需要通过电平转换器(例如74LVC系列)或上拉电阻适配,不能直接互连;

锁存器是电平触发事件,例如D锁存器在时钟高电平时透明,而触发器是边沿触发事件,仅在时钟上升沿或下降沿采样

5.FPGA的常用设计方法包括()

A.并发设计

B.流水线设计

C.乒乓缓存

D.源同步设计

BCD

FPGA常用设计方法是指针对其并行计算特性和资源特点优化的技术,包括流水线设计、乒乓缓存和源同步设计等:

流水线设计:将复杂逻辑拆分为多级寄存器级联的阶段,提高时钟频率

乒乓缓存:使用双缓存区交替处理数据,实现数据流无缝切换;

源同步设计:数据与时钟同源传输,例如DDR接口利用DQS信号消除时钟偏移,提高高速数据传输可靠性

“并发设计”是FPGA通过硬件资源复用实现的广义概念,并非常用设计方法

6.下面可能会产生Latch的情况有()

A.if...else语句不完备

B.缺少begin...end

C.case语句中缺少default

D.复位操作时,信号赋值是变量

AC

在Verilog/VHDL中,锁存器(Latch)通常由不完整的条件赋值产生,使组合逻辑记住当前状态,增加时序分析复杂度,导致毛刺和亚稳态,降低设计系统的可靠性

if...else语句不完备,没有对应的else分支,综合工具会生成Latch保持上一个状态;

缺少begin...end仅影响代码块范围,不会直接导致Latch;

case语句中缺少default,代码不能覆盖所有可能得输入,综合工具会生成Latch保持未定义状态下的输出;

复位操作时,信号赋值是变量与Latch无关

7.对于提高FPGA设计的时钟频率,下列说法正确的是()

A.增加流水级别,分割组合逻辑

B.组合逻辑平衡(register balance-register retiming)

C.寄存器复制,减少一个寄存器的输出(register duplicate),控制扇出,规定每个寄存器的最大扇出

D.优化状态机编码,使用ONE-HOT独热码进行编码

ABCD

提高FPGA时钟频率的核心是缩短关键路径时延,即寄存器到寄存器之间的组合逻辑延时。

增加流水级别,分割组合逻辑,使每级组合逻辑延时缩短,从而允许更高的时钟频率;

通过调整寄存器的位置,例如将寄存器存逻辑前级移到后级,重新平衡组合逻辑延时,使路径延时更加均匀,提升整体时序性能;

当单寄存器驱动多负载导致扇出过大时,输出网络的电容负载会增加RC时延,通过赋值寄存器降低单寄存器的扇出,可以减少输出延时改善时序;

独热码利用1位表示1个状态,虽然导致寄存器数量增加,但组合逻辑译码复杂度显著降低;

8.下列关于行为描述和结构描述特点正确的是()

A.行为描述是指描述电路的功能行为

B.结构描述有门级和开关级

C.结构描述是指描述元件或较大部件的互连

D.行为级描述有系统级、算法级和RTL级

ABCD

在硬件描述语言(HDL)中,行为描述和结构描述是两种核心建模方式,行为描述侧重于电路功能,结构描述侧重于电路实现。

行为描述是指描述电路的功能行为,不涉及具体硬件结构,按照抽象层级可以分为系统级、算法级和RTL级;

结构描述是指底层元件实例化与接口互联,包括门级和开关级

9.在下列程序中,给出了几种硬件实现,以下的模块被综合后可能是哪种?()

always@(posedge clk)

if(A)

C=B;

A.一个上升沿触发器和一个多路器

B.一个输入是A,B,clk的三输入与门

C.一个透明锁存器

D.一个有使能引脚的clk上升沿触发器

AD

根据代码分析:行为描述的是时钟边沿触发的寄存器逻辑,属于时序逻辑电路,与门和锁存器均属于组合逻辑电路,B、C错误;

if(A)语句可以被综合为组合逻辑多路器,或触发器的使能信号。

若综合为组合逻辑多路器,当A=1时,多路选择器B作为输入,当A=0时,多路器默认保持寄存器原值,此时代码被综合为一个上升沿触发器和一个多路器;

若综合为触发器的使能信号,当A=1时,时钟上升沿到来时更新数据,当A=0时,数据保持原值,此时代码被综合为一个带有使能引脚的clk上升沿触发器

10.对FPGA器件的接口约束正确的有()

A.所有同步输入信号都要进行建立时间和保持时间

的约束

B.约束的建立时间小于实际测得的建立时间和保持时间,以保证一定的时序裕量容忍实际工作过程中存在的时序波动

C.具体的约束值需要参考逻辑器件输入管脚实际测得的时钟数据相位关系确定

D.建立时间和保持时间无需约束

AC

所有同步输入信号都要进行建立时间

和保持时间

的约束,避免产生亚稳态;

约束的建立时间应大于实际测得的建立时间和保持时间,以确保设计在最坏情况下仍满足时序;

具体的约束值需要参考逻辑器件输入管脚实际测得的时钟数据相位关系确定;

未约束建立时间和保持时间会导致静态时序分析工具无法验证时序,可能在实际运行中出现亚稳态或数据采样错误

判断题

1.逻辑开发软件的版本没有统一要求,任何补订的版本都可以使用()

A.错误

B.正确

A

逻辑开发软件(如Vivado、Quartus、ISE等)的版本选择对设计流程至关重要,不同版本软件对硬件器件、IP核和第三方工具的支持存在差异,低版本软件可能不支持新器件或新特性,高版本软件可能无法打开旧版本工程文件;

新版本通常修复旧版本的bug、优化性能或增加新功能,若设计依赖某版本特有的功能或存在已知bug,必须使用特定版本;

团队开发需统一版本,避免因版本差异导致设计不兼容,例如网表格式、约束文件语法,维护旧项目时,可能需要使用与原开发一致的版本,否则可能因工具链变化导致编译失败;

部分软件版本的许可证类型不同,功能限制或授权范围可能影响设计流程

2.Verilog语言运算符没有优先级()

A.错误

B.正确

A

3.Moore状态机的输出由输入和当前状态确定()

A.错误

B.正确

A

状态机根据输出信号是否与输入信号相关可以分为Moore状态机和Mealy状态机:

Moore状态机的输出仅由当前状态决定,与输入信号无关;

Mealy状态机的输出由当前状态和输入信号共同决定

4.使用四个空格符缩排,可以使用TAB键()

A.错误

B.正确

A

在代码编写过程中,不同编辑器对TAB键的解析不同,可能为 4 个空格,也可能为 8 个空格,空格和TAB混合使用将导致代码缩进混乱,影响代码的可读性。代码开发团队应遵循统一的缩进风格,选择全空格或全TAB的缩排方式

5.模块内部的声明,reg类型必须要声明,wire类型可以不声明()

A.错误

B.正确

A

在Verilog语言中,无论是reg还是wire类型的信号都必须显式声明后才能使用。其中,reg类型信号用于存储数据或表达时序逻辑;wire类型信号用于连接不同模块或表达组合逻辑