【蓝桥杯嵌入式】【模块】一、系统初始化

1. 前言

最近在准备16届的蓝桥杯嵌入式赛道的国赛,打算出一个系列的博客,记录STM32G431RBT6这块比赛用板上所有模块可能涉及到的所有考点,如果有错误或者遗漏欢迎各位大佬斧正。

本系列博客会分为以下两大类:

1.1. 单独模块的讲解

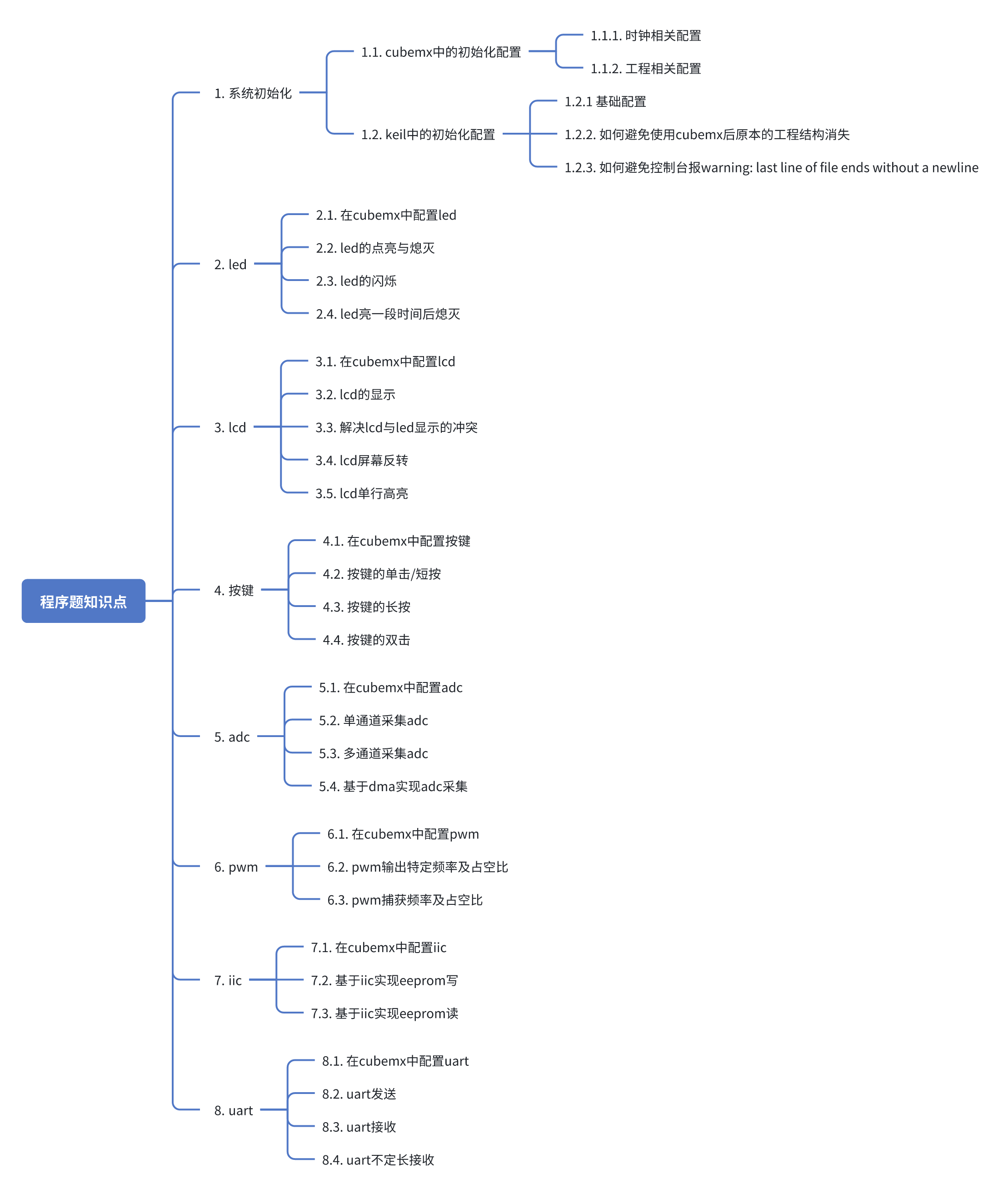

在这部分,我会分享自己总结的各个模块的相关配置、代码书写模板,涉及到的大致框架如下:

这个框架后续可能会不断更新,欢迎各位给出建议。

这一大类相关的文章链接如下:

【蓝桥杯嵌入式】【模块】一、系统初始化-CSDN博客

【蓝桥杯嵌入式】【模块】二、LED相关配置及代码模板-CSDN博客

1.2. 蓝桥杯各届的真题、模拟题复盘及个人答案

在这一部分,我会分享个人练过的所有题的复盘思路及代码。

这一大类相关的文章链接如下:

以下是本篇博客正文内容:

2. 在cubemx中的初始化配置

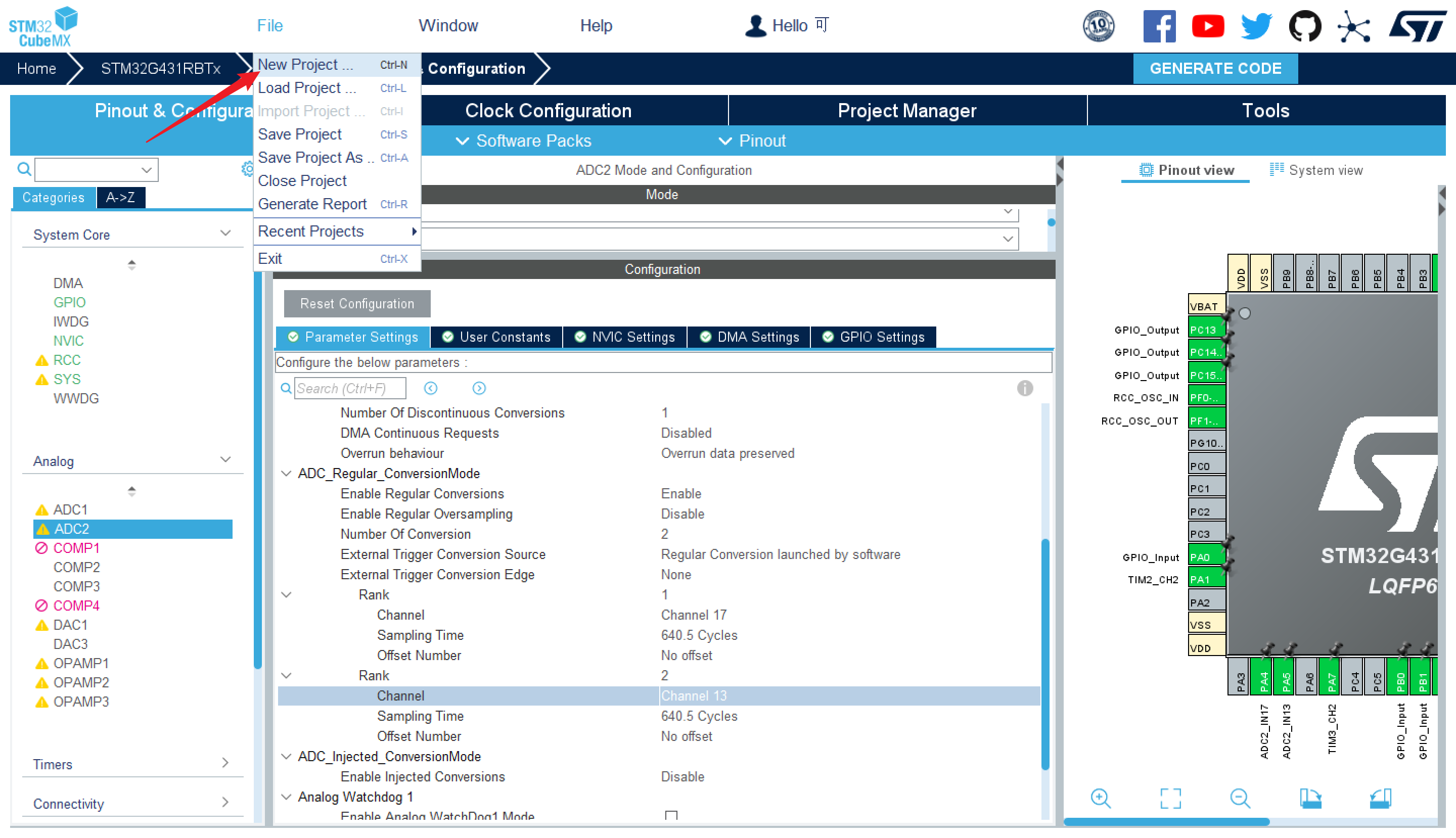

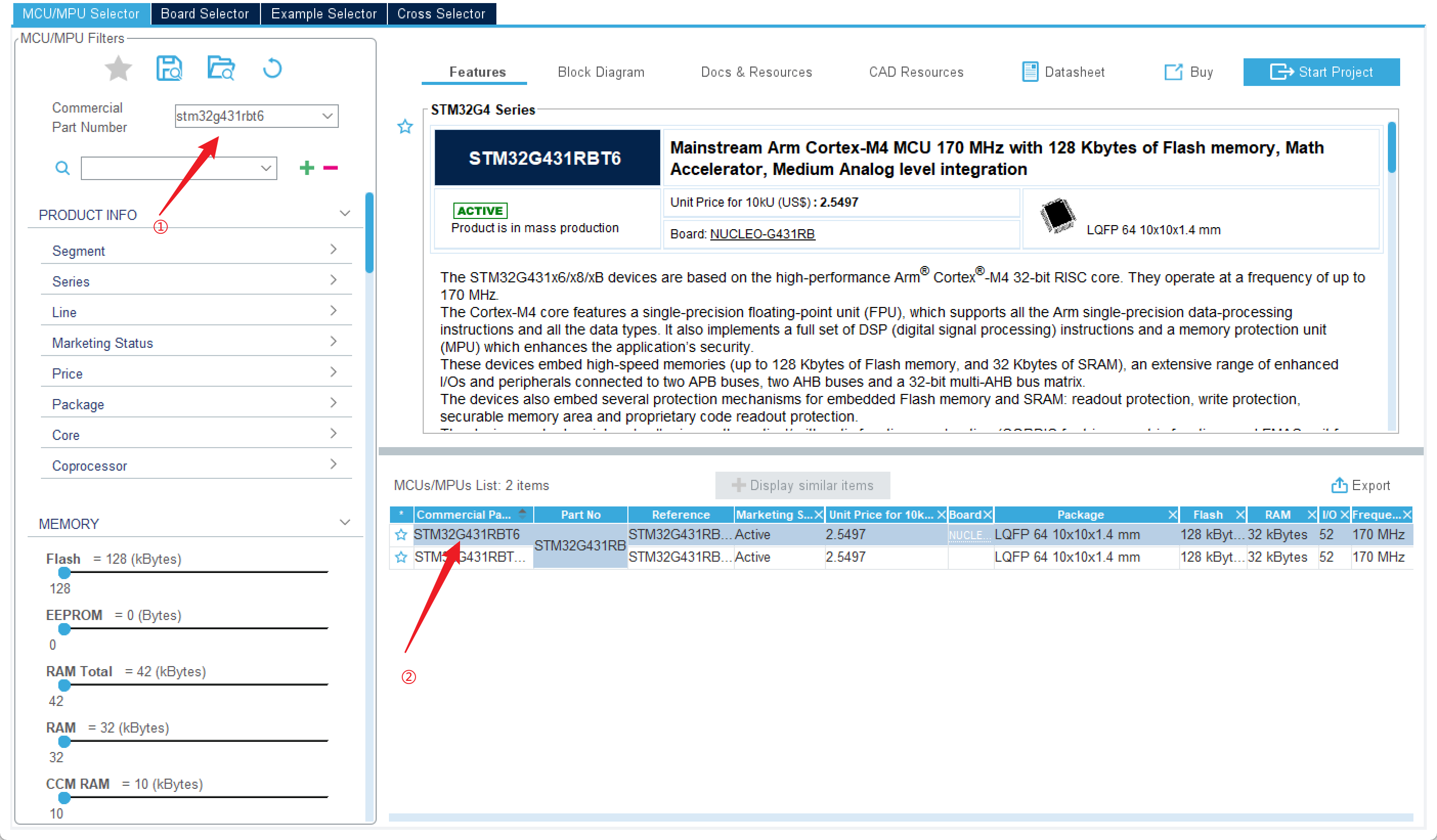

首先,需要在cubemx中新建stm32g431rbt6的工程,流程见下图:

第一步,新建一个工程。

工程中选择芯片:stm32g431rbt6,选择图示正确的封装。

PS:在左上角输入芯片型号时将输入法切换成英文,否则一次会输入两个字母。

2.1. 时钟相关配置

时钟配置总的来说分为三步:

- 配置调试接口

- 配置RCC时钟

- 配置时钟树

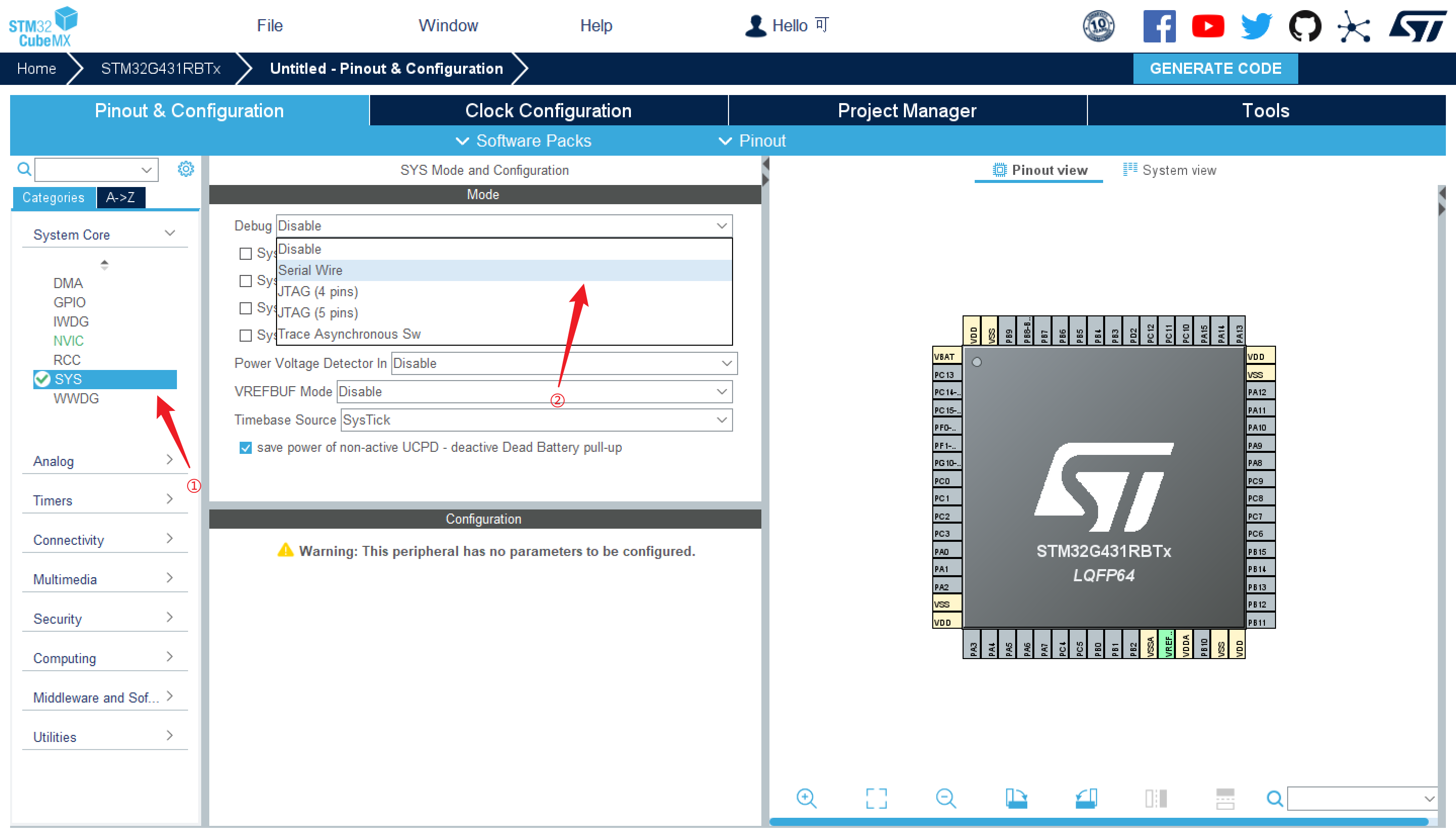

第一步,配置调试接口,选择图示选项。

因为比赛用板采用的是串口转stlink的烧录方式,选择Serial Wire表示启用SW烧录接口,这样才能适配烧录器。

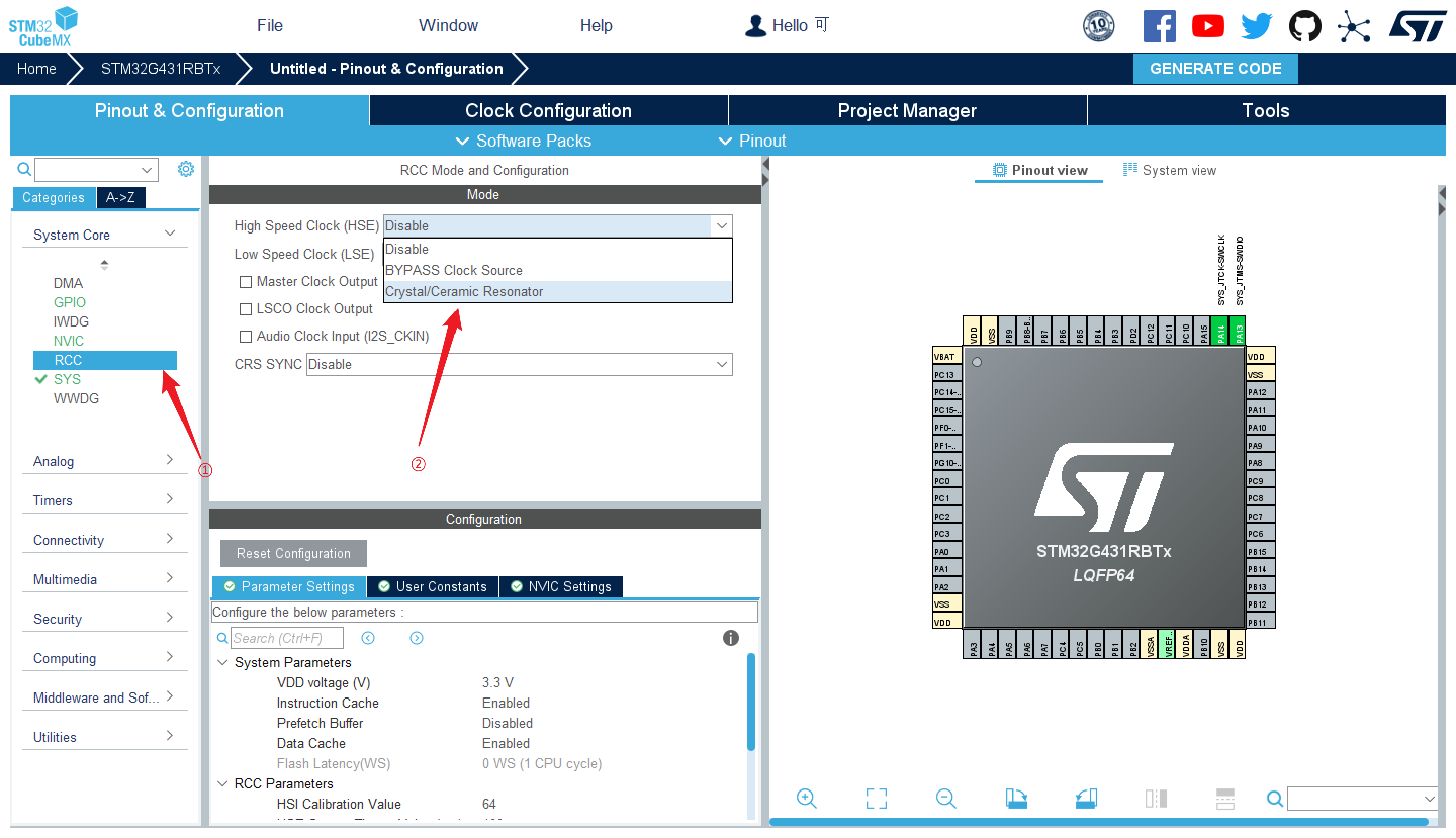

第二步,配置RCC时钟源,选择图示选项。

图示选项代表芯片使用外部时钟源的外部无源晶振,这样的晶振的精准度是最高的。

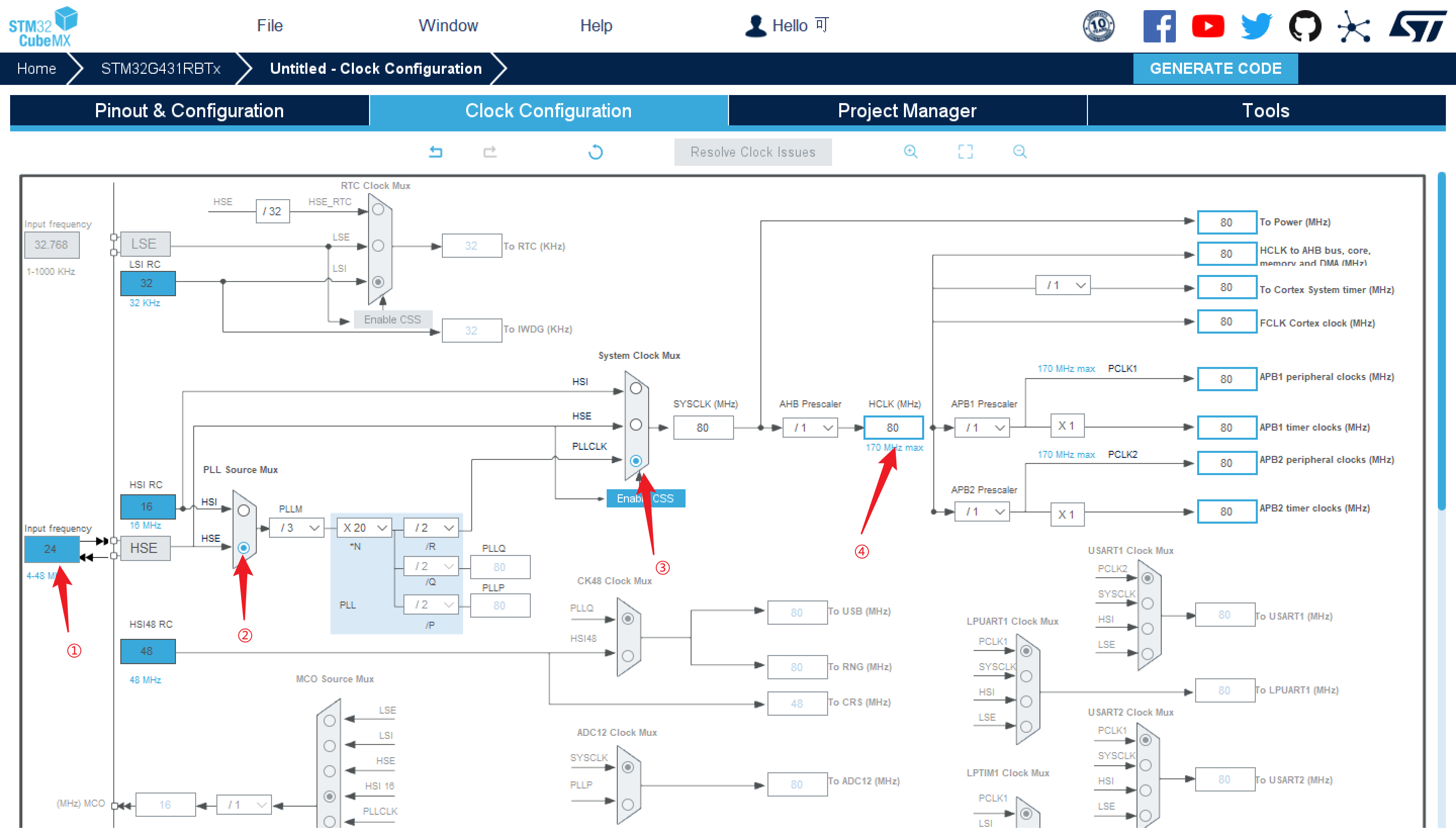

第三步,配置时钟树,按图示配置。

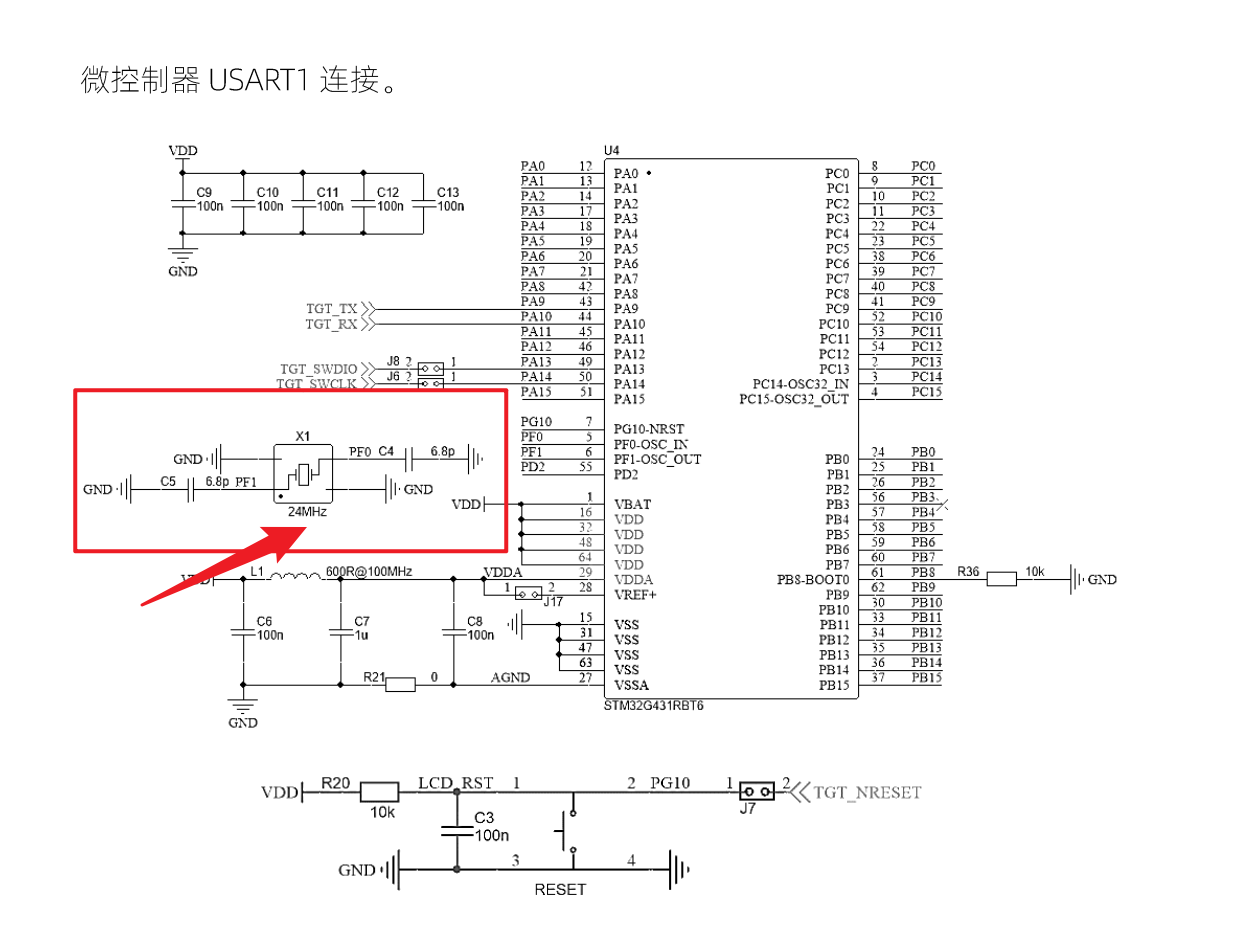

输入频率即等于外部无源晶振的振动频率,根据开发板手册,其频率为24MHZ。

后续勾选HSE、PLL锁相环,最终将总频设置为80MHZ,这也是比赛通常要求的系统主频。

2.2. 工程相关配置

工程的配置主要是涉及到工程文件的保存路径、保存方法。

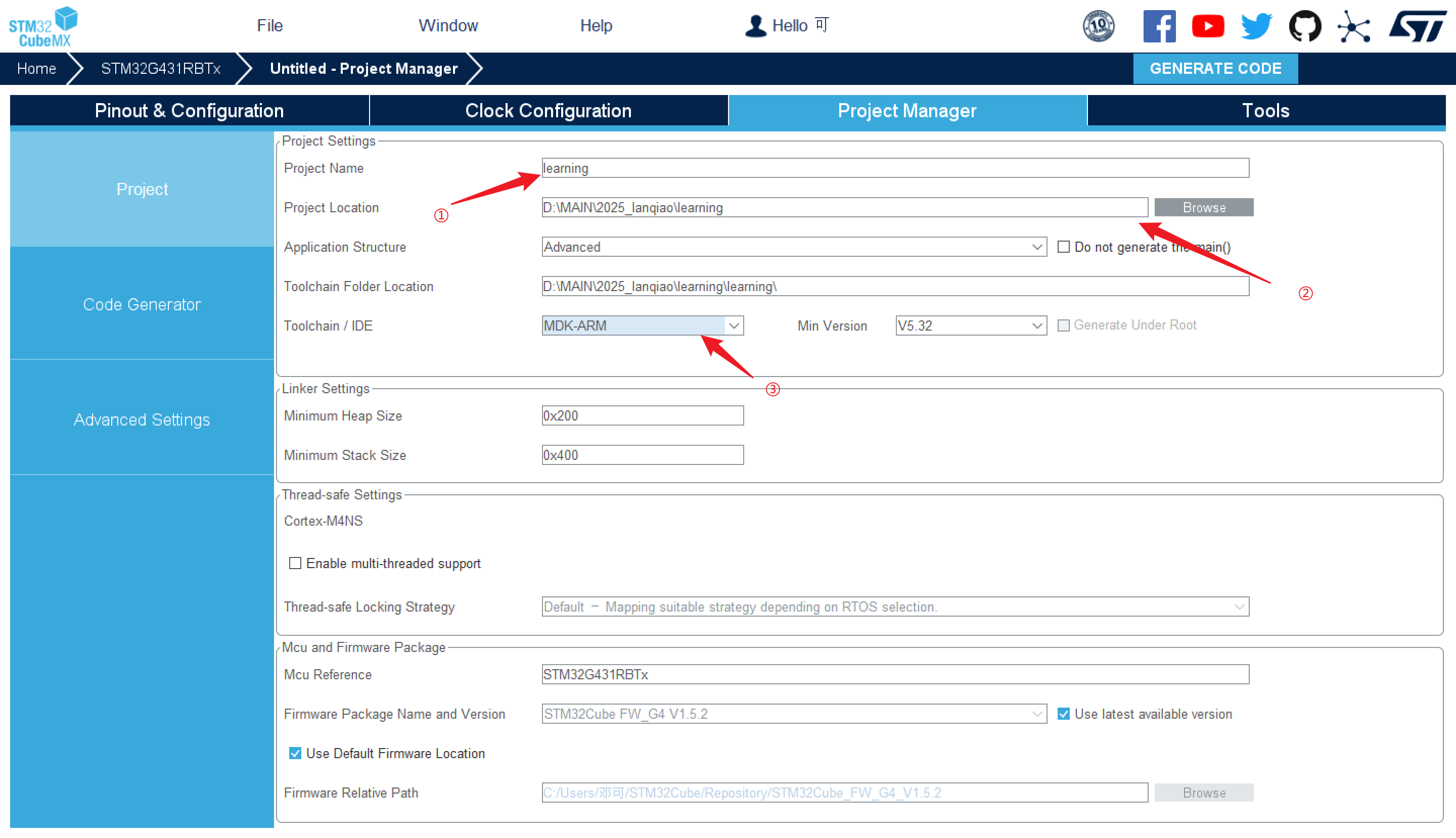

第一步,在Project选项下定义项目工程名、存放路径,注意,第三步一定要选择MDK-ARM,这样才能在keil下打开这个工程。

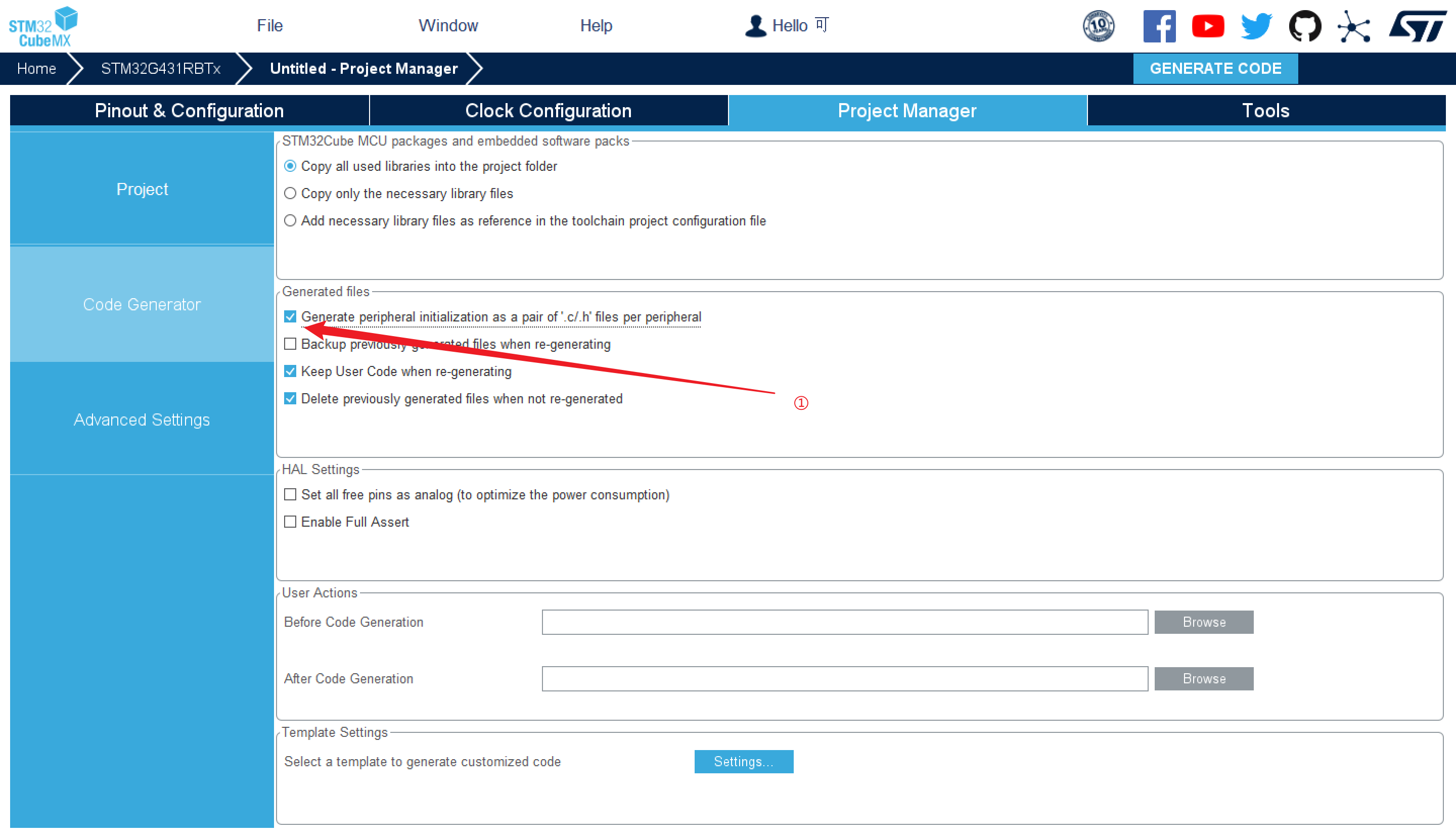

第二步,在Code Generator中勾选图示选项。不过这一页的勾选选项因人而异,不会对工程造成决定性的影响。

我选择构成图示选项是因为勾选之后相关外设的初始化会生成单独的.c/.h文件,与我后续的模块化工程结构比较相符。

3. keil中的初始化配置

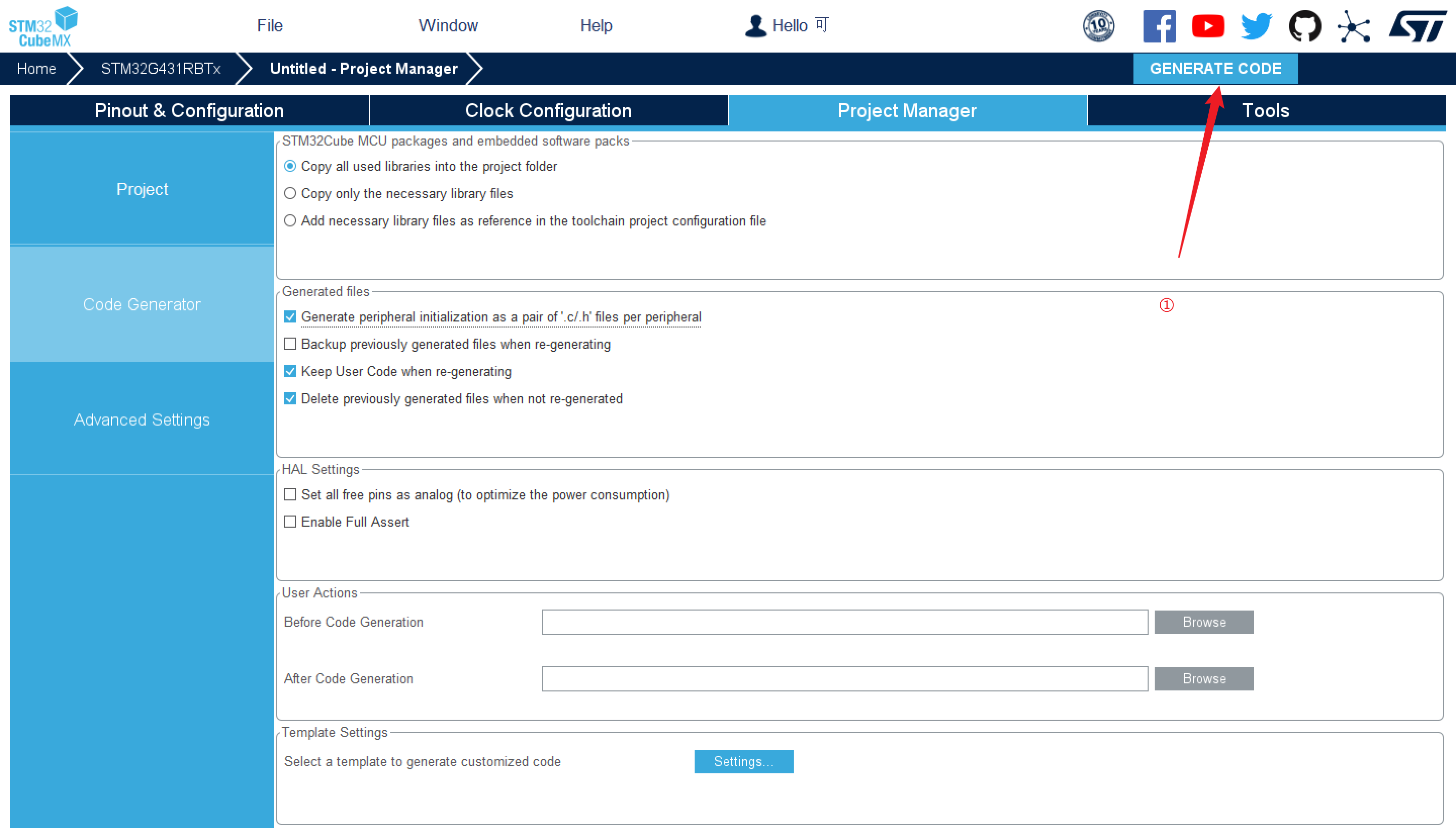

cubemx配置好后选择右上角的生成代码,便可生成一个keil工程。

3.1. 基础配置

这一部分我感觉直接看别人的适配教学比较快捷:

开发板资源简介&工程模板建立_哔哩哔哩_bilibili

我喜欢按如下步骤做基础的配置(建议照做)。

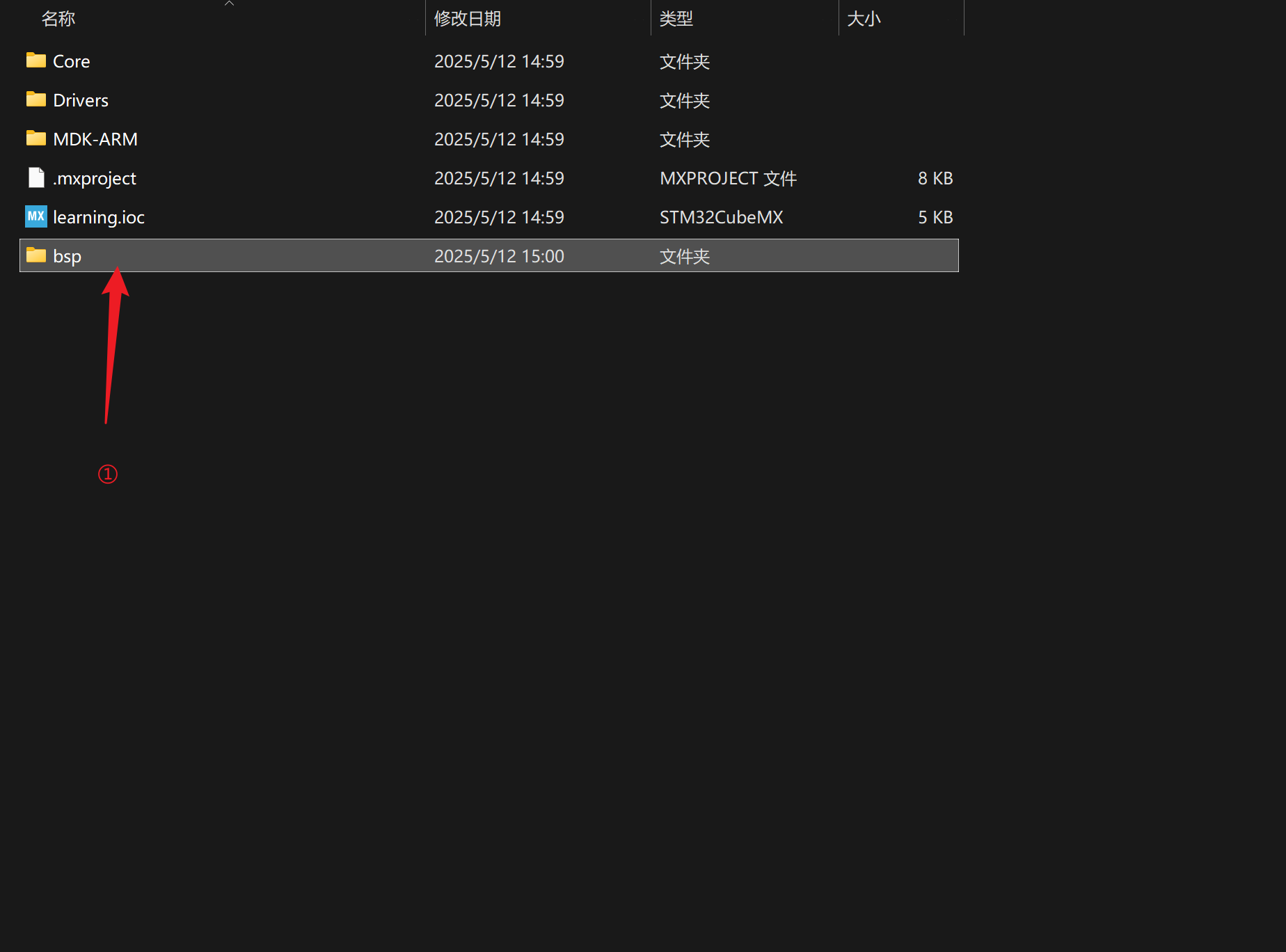

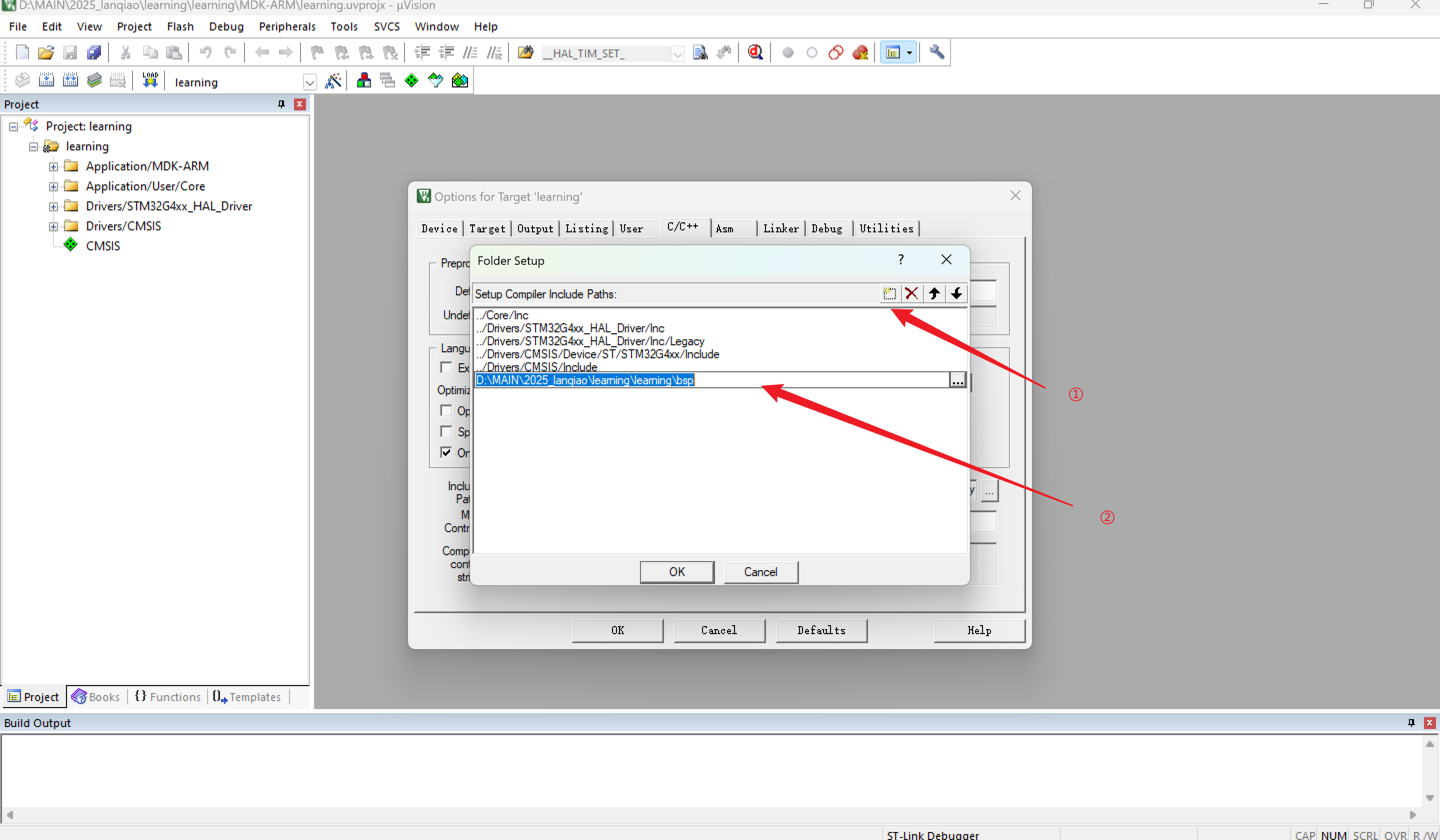

第一步,在图示目录下新建一个bsp文件夹,用于存放后续会用的需要移植的蓝桥杯官方模板文件。

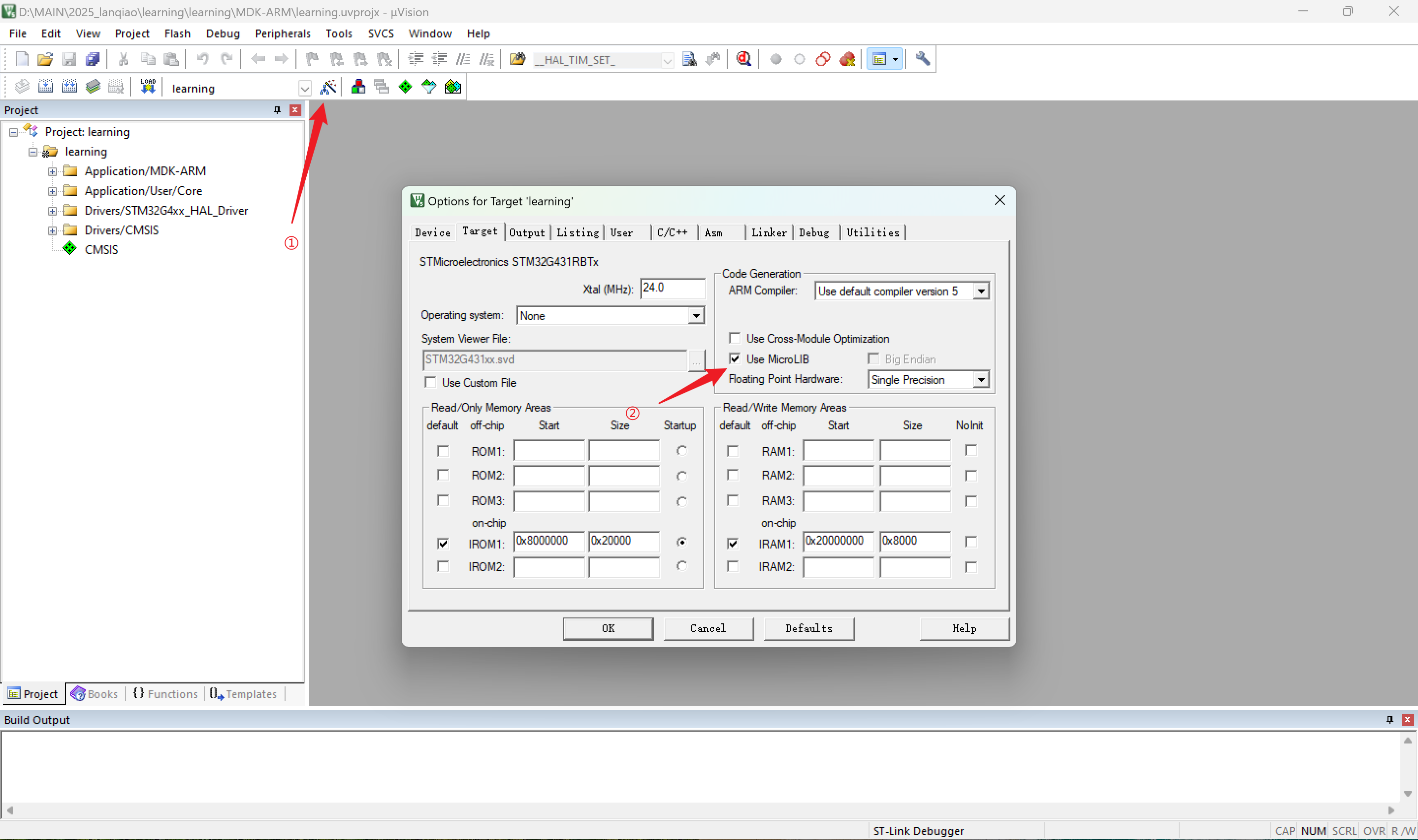

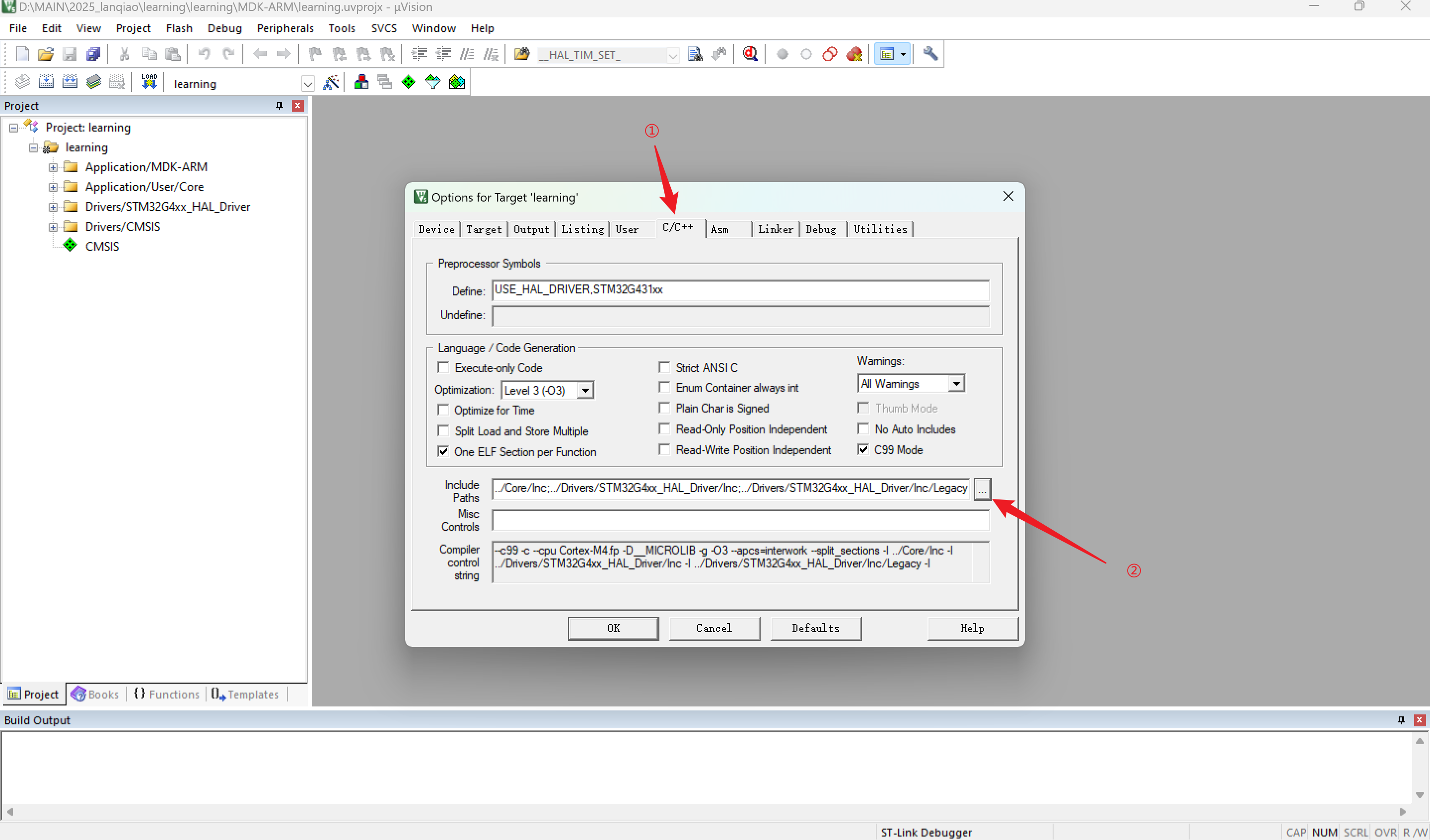

第二步,按图示顺序将微软的微库勾选上,我们后续的串口收发等功能会用到这个库。

第三步,将刚刚新建的那个bsp文件的路径加入编译头文件路径里,否则会编译报错,显示找不到头文件。

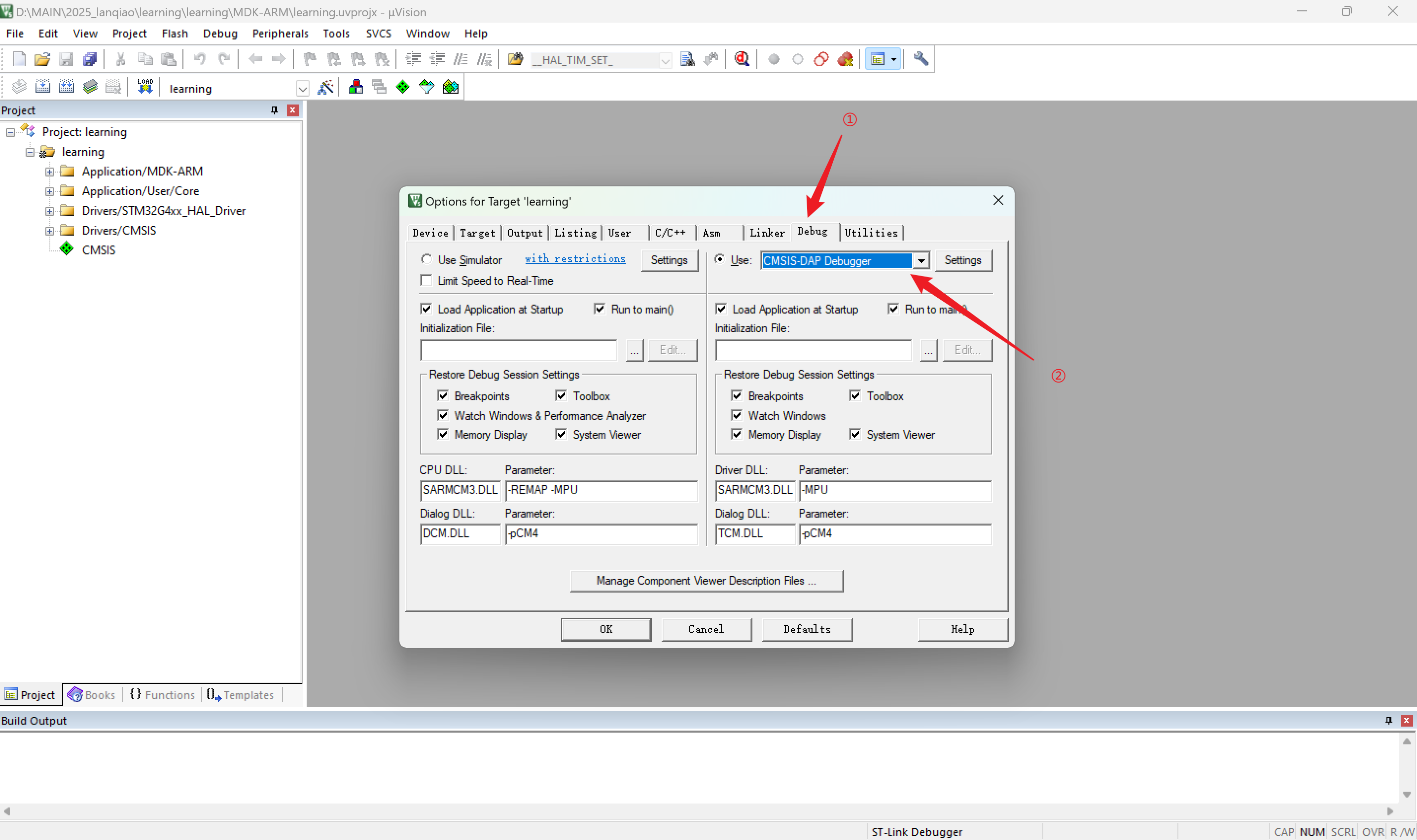

第四步,将烧录选项改成如图所示。

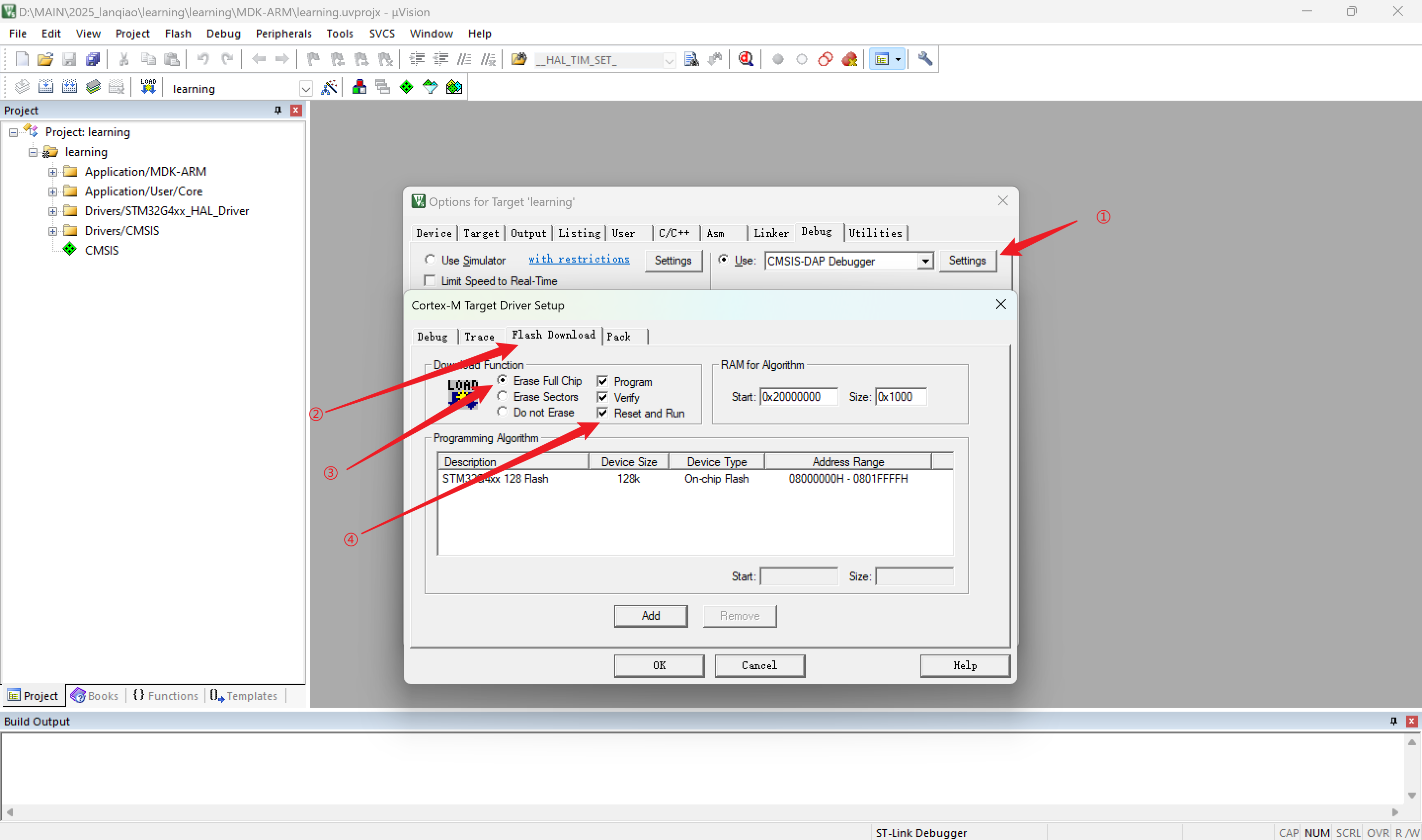

第五步,按如图所示勾选,这样每次烧录时,会先清除板子里之前的代码,并自动重启、运行。

3.2. 如何避免使用cubemx后原本的工程结构消失

这个bug有些同学可能遇到过,即自己按之前的流程将bsp文件建好了,keil中的各种选项都勾好了,发现cubemx中还有些东西没配好,于是配好之后生成工程,生成好之后发现原本的工程结构和keil配置都消失了,于是只得重新再配。

这个bug貌似是ide版本的问题,这里介绍一种解决办法:

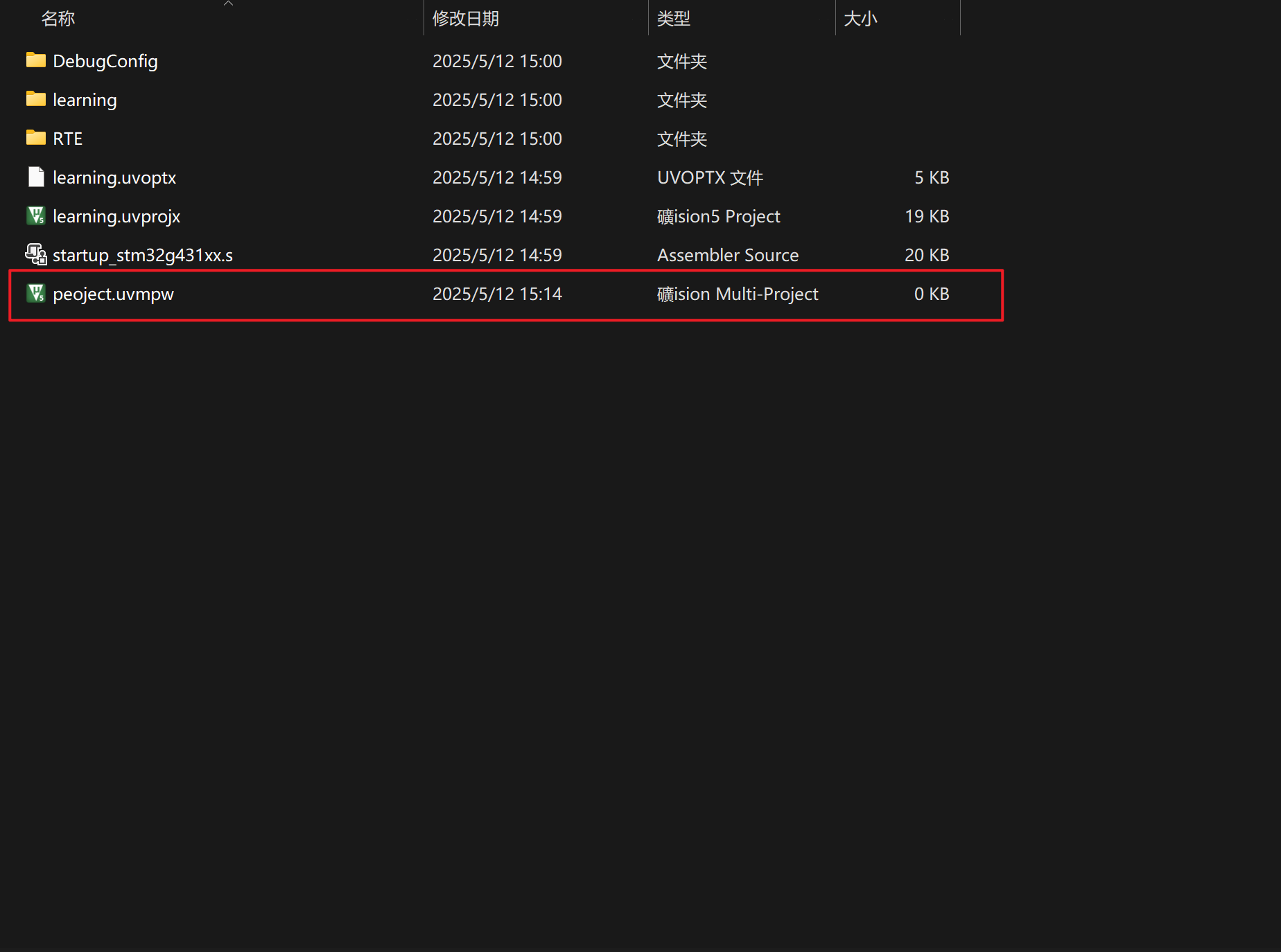

在与keil文件同级的目录下,建一个文本文件,将名字和后缀都改成图示文件那样即可。

3.3. 如何避免编译后报warning:last line of file ends without a newline

这个问题是keil的软件bug,实际可以不用管,要解决其实也很简单,网上大多是说在报警告的文件最后一行敲一下回车,不过有种更一劳永逸的办法,参考于:

Keil uVision 用错误屏蔽彻底消除 warning: #1-D: last line of file ends without a newline 方法_keil 屏蔽报错-CSDN博客

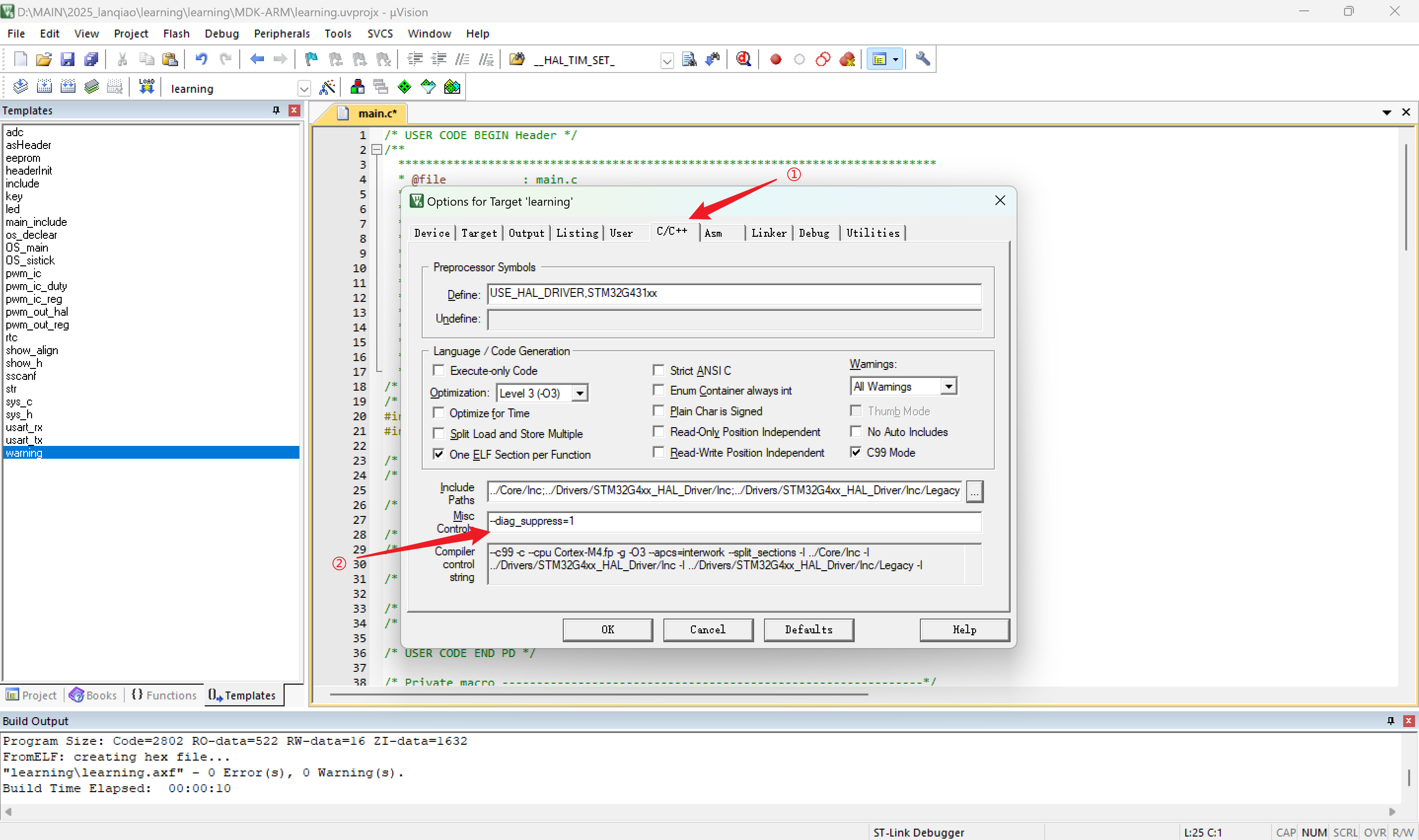

在编译选项中做如此设置便可以屏蔽调该警告。

总结

本文介绍了初始化工程的建立方法,包括cubemx和keil中的配置,以及一些常见小bug的解决方法。