异步复位,同步释放

参考链接:数字电路复位信号设计(异步复位、同步释放)笔记详解_异步复位同步释放的高有效原理-CSDN博客

一、异步复位(Asynchronous Reset)

-

含义:当复位信号

reset为低(或高,视具体设计),不论时钟clk的状态,电路立即进入复位状态。 -

作用:电路能在系统上电或发生错误时立即复位,不用等时钟边沿。

二、同步释放(Synchronous Release)

-

含义:虽然复位是异步进入的(立即清零),但退出复位(释放)时,是等待时钟上升沿才恢复正常工作。

目的:避免因异步信号直接控制状态机或逻辑单元造成亚稳态或毛刺,保证时序一致性。

三、结合实现:异步复位 + 同步释放

这种组合设计的重点是:

-

异步进入复位(立即生效)

-

释放时需要同步到时钟边沿再启用功能逻辑

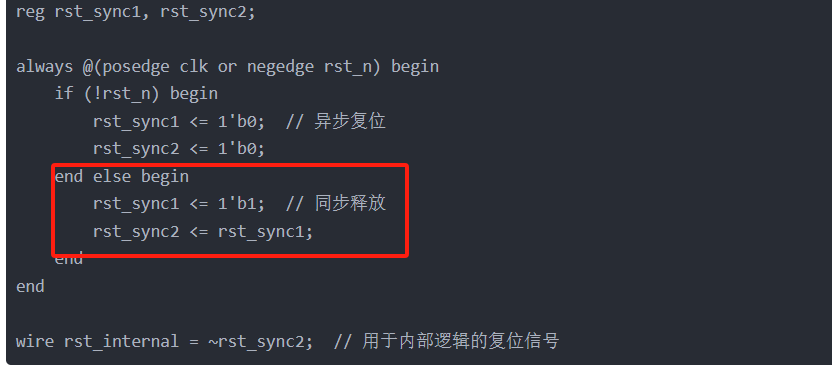

reg rst_sync1, rst_sync2;always @(posedge clk or negedge rst_n) beginif (!rst_n) beginrst_sync1 <= 1'b0; // 异步复位rst_sync2 <= 1'b0;end else beginrst_sync1 <= 1'b1; // 同步释放rst_sync2 <= rst_sync1;end

endwire rst_internal = ~rst_sync2; // 用于内部逻辑的复位信号

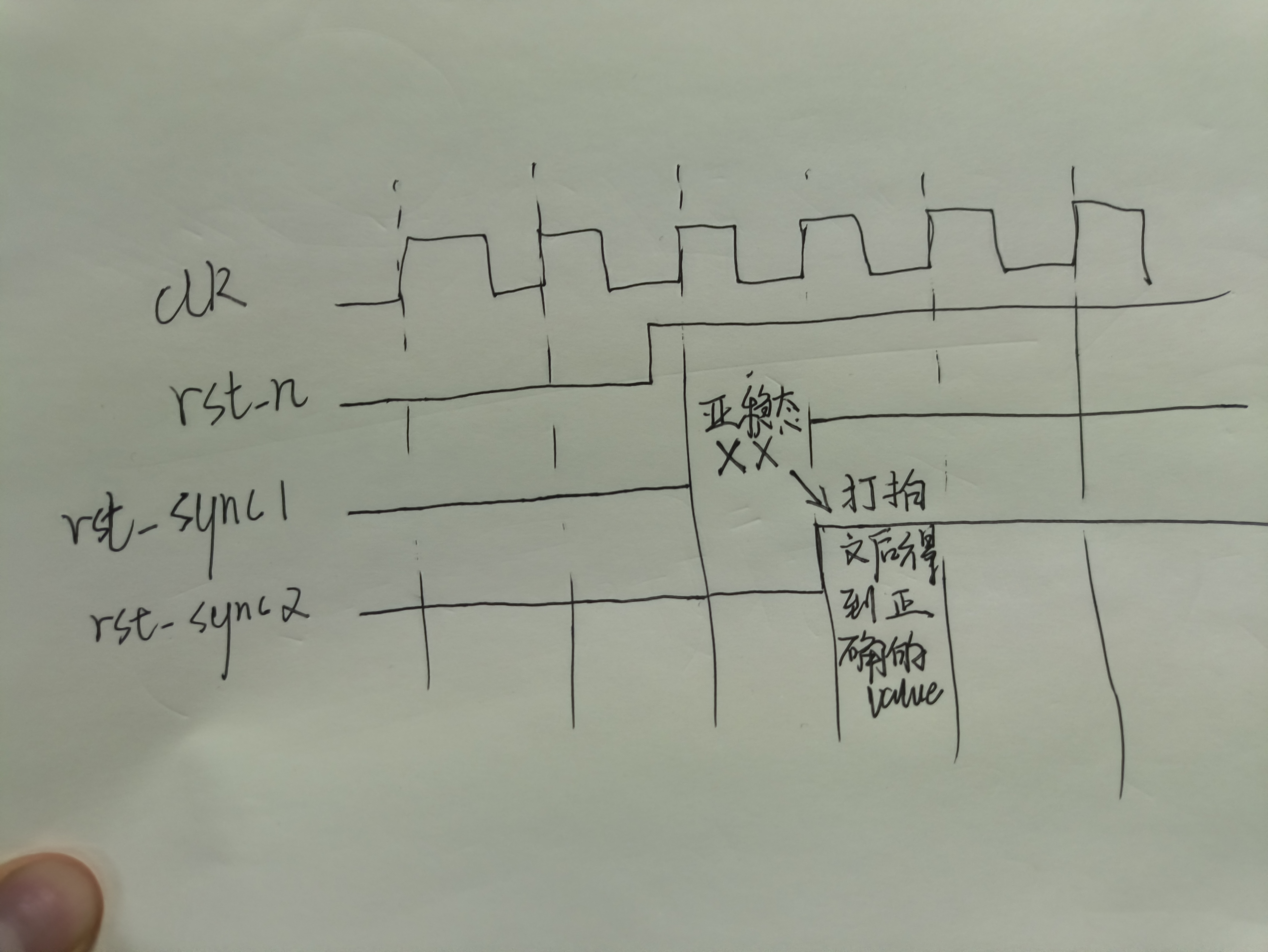

代码的灵性在同步释放,首先是rst_sync1没有复位的时候,值为1。其次,此时rst_sync2是一个打两拍操作 ,解决了亚稳态问题。

至此,完成了异步复位,同步释放。