pcie phy电气层(PCS)详解gen1、2 (rx)

注:推荐大家查看英文原版,笔者大部分内容也为翻译;

S IP:

1. pcie供电:

Vph: 1.2,1.5, 1.8V high voltage IO supply;

Vp/VptxX/Vpdig :analog supply, 0.9V;

vddcore: core supply; 0.75~0.9V;

其中Vddcore和Vp在进行upf时会通过power switch对外部pin进行控制;

一,. upcs层 支持的feature:

1, 支持original PIPE结构;

2. 支持serdes 结构;

3.支持pclk方式: pclk as phy output/input; 支持external pll;

4. 支持low pin count interface,移除那些对timing时序较低的信号线,将他们挪到message bus register中;

5. 标准的pipe接口连接mac层;

6. pcie 8b/10b以及128b/130b编解码;

7. 传输PIPE 相关的power state(P0,P1,等)到phy层,并维持power相关的sequence;

8. 时钟补偿 elastic buffer (original pipe结构)

9. error report

10. 可选的bif & aggre 结构

11. 最多支持连接x16 lane;

Original PIPE:在检测到EIOS之后,phy_rxX_data_en; 被拉低;lane CDR停止转换;使用elastic buffer模式,来补偿lane skew;

serdes pipe 结构:

数据move 在controller中实现;pipeline 可选用于timing 收敛。

Mindshare 部分翻译

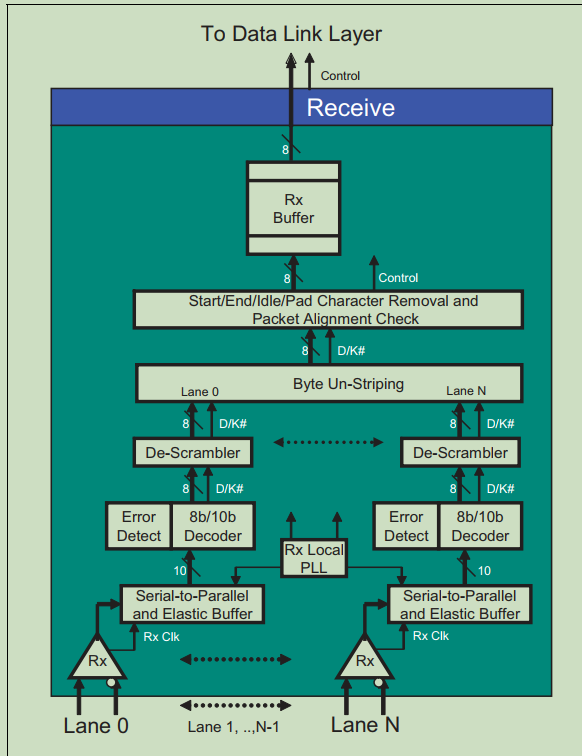

整体框图;

差分对接收:

RX 时钟恢复:

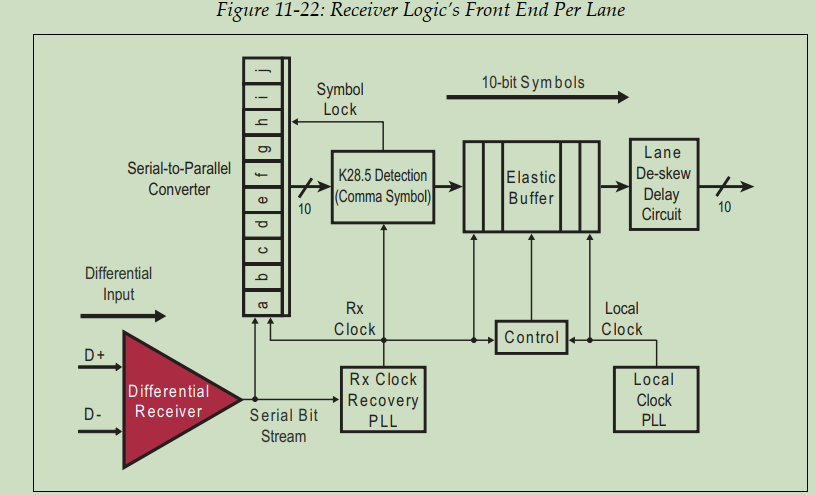

gen1,2 没有CDR结构;使用的是RX本地PLL进行恢复,PLL时钟和tx数据流同频(2.5或者5Ghz)。并且将RX数据进行解串。解串数据10bit为一组。解析出COM码。

接收bit锁定:在TX 8b/10b编码中,已经包含了频率信息。(CRD)当RX时钟和TX时钟的频率同步了,可以被称为“bit lock”

在低功耗下(l0s或L1),为了避免数据包丢失造成bit lock 失锁。所以TX在进入到低功耗之前要发送EIOS码告知RX关闭其输入(de-gate)。

Regaining Bit lock:重新锁定

当TX 从L0s状态恢复时,会发送特定数量的FTS(S IP 默认CX_NFTS=200)接收端会从新获取bit和symbol lock。从L1恢复和L0s情况完全不同。

symbol lock:

COM码有两种编码方式:![]()

所有order set 均不会进行scramble 在tx端。只要检测到了COM之后就被称为“symbol lock”

RX 端时钟补偿

elastic buffer: 输入recovery clock;输出receiver clock;当输入快输出慢时会删除SKP,反之亦然;elastic buffer有两种方式:empty buffer,half-empty buffer。TX周期性的发送SKIP码流就是为了消除skew。他们在传到下一个层dllp之前会被完全丢弃。

当在1180到1538 个symbol 周期内发送SKIP order set。一个symbol就是10bit 码流。

SKIP最大间隔:![]()

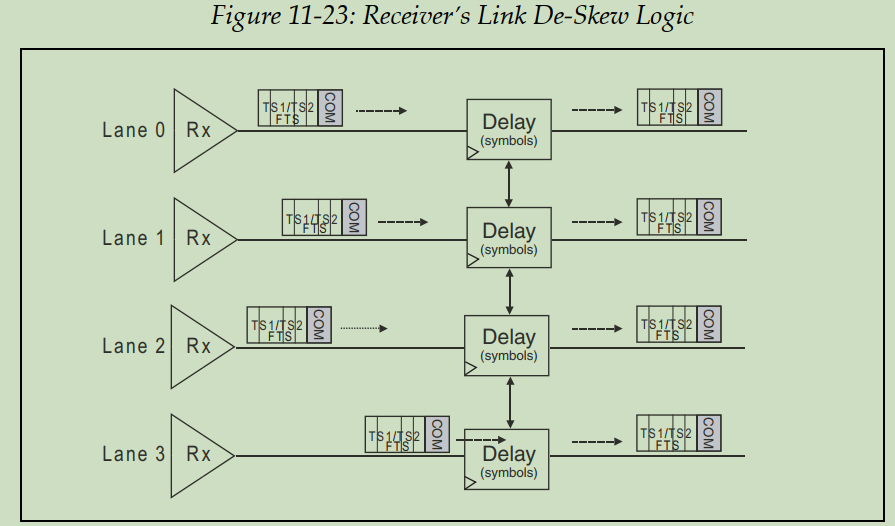

lane到lane之间的deskew

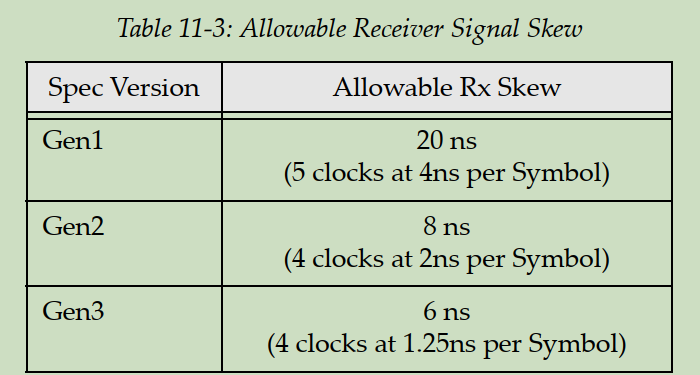

由于多种原因(pcb布线等)会找出RX端存在lane之间的skew。

ordered set 帮助deskew

所有的lane在相同时间检测到COM码,用于deskew;超前检测到COM码会加入延迟。

RX lane2lane de-skew capability

放在elastic buffer之后;优点:到达时间差现在被本地时钟同步为符号时间。可以通过延迟早到的COM适当符号时钟来使其与晚到的COM对齐。接收器允许的最大时钟偏移是时钟周期的整数倍。

(注:官方spec中只提及了Gen1 允许的最大de-skew,其余未提及,gen2~gen5应该都是4 clocks最大,正好是一个SKP order set有续集时间)

注:1. 为什么8b/10b decode要放在elastic buffer之后?

1)时钟域隔离;

elastic buffer就是一个跨时钟与fifo;所以必须先缓存并稳定数据,然后再到本地时钟域解码。确保稳定性。

2)保持码流完整性;

8b/10b 编码保证了传输的直流平衡和足够的边沿用于时钟恢复。CDR用的是10bit编码后的数据来锁相。先解码可能会丢失时钟边沿信息。

3) 链路训练需要使用原始10b数据

链路训练过程中检测特殊字符K码。都是10bit编码;

4) 更尬获得处理码流skew

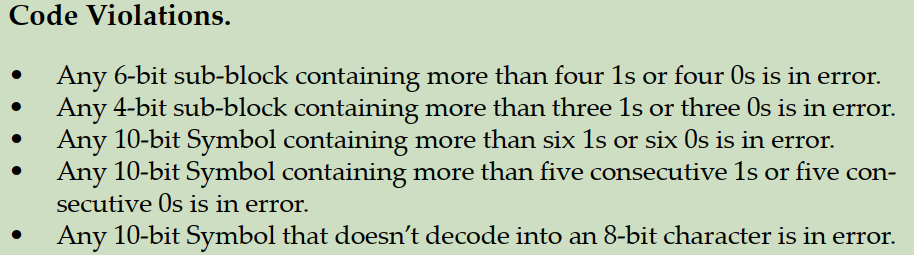

8b/10b解码

通过查找表来解码,两个查找表。D码和K码。

10b码流disparity计算。当symbol lock之后开始指定初始的disparity。

如果一个符号(Symbol)中的两位发生错误翻转,该错误可能不会被察觉,而该符号仍可能被解码为一个有效的8位字符。这样的错误在物理层是无法被检测到的。

descrambler(解码器)

在8b/10b之后是解码器;只对Data数据进行解码,K码不进行解码。当一个 COM 字符进入解扰器时,它会将 LFSR(线性反馈移位寄存器)的值重新初始化为 FFFFh。

disable:

If the descrambler receives at least two TS1/TS2 ordered sets with

the “disable scrambling” bit set on all of its configured Lanes, it disables the

descrambler.当收到至少两个TS序列中包含了disable scrambing bit时,disable该功能。

Byte-unstrip

un-striping: 去交织;在接受端将多条lane中的字符从新按原始顺序合并成串行数据流的过程。

TX strip:tx交织的实现;

将一个数据包中的字节分发到多个通道(lanes)中,形成并行发送的结构。例如在 x8 链路中,第1个字节发到 Lane 0,第2个发到 Lane 1,以此类推,循环分配。Round-Robin 字节分发。但是要注意STP/SDP/END symbol需要有一些特定的规则。

RX buffer

RX buffer 保存TLP和DLLP的数据(header+data)。

物理层错误处理

内容不多,放到一起了。

S IP中通过CR端口或者Jtag 端口可以读到Phy内部的所有reg;用于判定phy status。

必须上报错误:

8b/10b decode error: disparity, illegal symbol;

S IP中有pipe_rxX_rec_ovrd_8b10b_decerr 信号;用于指示当收到error时应该如何处理。

可选的error checking;

• Loss of Symbol lock (see “Achieving Symbol Lock” on page 396)

• Elastic Buffer overflow or underflow

• Lane deskew errors (see “Lane‐to‐Lane Skew” on page 398)

• Packets inconsistent with format rules

Response of Data Link Layer to Receiver Error

物理层像dllp层报告一个rx error之后会自动出发dllp的错误重传机制。回复nak,retry buffer输出当前tlp报文。当使能了AER时该错误会报告出来,一个correctable error;

Active State Power Management

phy + controller 配合支持pcie 低功耗。(低功耗内容,可能会开一个专题)

Link Training and Initialization

后续会开一个专题。