中央处理器(CPU)(概述、指令周期)

一、概述

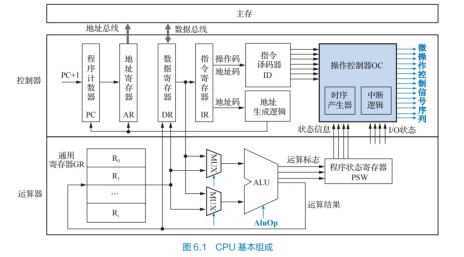

主要功能:(1)程序控制(2)操作控制(3)时序控制(4)数据加工(5)中断处理

组成:早期冯·诺依曼计算机的 CPU 主要由运算器和控制器两部分构成,现代 CPU 还增加了cache、MMU、浮点运算器等单元。

1.1 CPU 中的主要寄存器

(1)程序计数器(PC)

程序计数器(PC)保存要执行的指令的字节地址,CPU取指令时借助PC来访问主存,Intel x86 系列中称为指令指针寄存器(IP)。PC 位宽与主存地址总线位宽相同。

(2)存储器地址寄存器(AR)

存储器地址寄存器(AR)也可简称为地址寄存器,在 CPU 中AR 通常用来保存 CPU 访问主存的单元地址,无论 CPU 是取指令还是存取数据,都必须先将要访问地址送入 AR,直到读写操作完成。AR 位宽和主存地址总线位宽相同。

(3)存储器数据寄存器(DR)

存储器数据寄存器(DR)也可简称为数据寄存器,在 CPU 中 DR 用于存放从主存中读出的数据或准备写入主存的数据,其数据位宽与机器字长相同。作为 CPU 和主存之间的缓冲寄存器也可用于存放运算器 ALU 的操作数、运算结果或中间结果,以减少访问主存的次数。

(4)指令寄存器(IR)

指令寄存器(IR)用于保存当前正在执行的指令。从主存中取出的指令字存放在 IR 中,其位宽和指令字相同。

(5)通用寄存器组(GR)

通用寄存器组(GR)是指运算器内部的若干寄存器,又称寄存器堆。这些寄存器都对程序员可见,每个寄存器均有对应的地址编号,寄存器地址由指令字中的地址码部分提供。

(6)程序状态字寄存器(PSW/PSR)

程序状态字寄存器(PSW/PSR)用于保存由算术运算指令、逻辑运算指令、测试指令等建立的各种条件标志。另外程序状态字寄存器还可用于保存中断和系统工作的状态信息,以便 CPU 能及时了解计算机运行的状态,从而便于控制程序。

1.2 操作控制器

操作控制器接收指令译码器,形成各种具有严格顺序的操作控制信号,控制相应部件按指令的功能依序进行动作,从而实现指令的功能。

CPU 执行指令的过程就是 CPU 控制信息流的过程,操作控制器是控制的决策机构,其产生的微操作控制信号序列就是控制流。

1.3 时序产生器

指令执行过程中的所有操作都必须按照一定的次序执行,需要引入时序的概念,也就是要对完成指令而执行的微操作控制信号进行时间调制,严格规定各信号的产生时间和持续时间。

操作控制器分为硬布线控制器和微程序控制器两种。前者采用时序逻辑,是一种硬时序;后者采用程序存储逻辑,是一种软时序。

二、指令周期

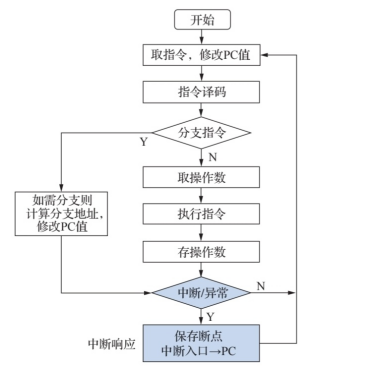

2.1 指令执行流程

计算机运行程序的过程,实质上就是由控制器根据程序对应的机器指令序列逐条执行指令的过程。

2.2 指令周期基本概念

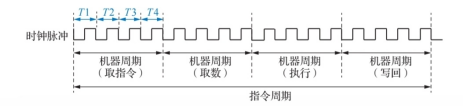

指令周期:一条指令从取出到执行完成所需要的时间

一般计算机包含取指周期、译码|取操作数周期、执行周期、写回周期。部分计算机还有中断周期、总线周期和IO周期。

为了便于指令的同步,可进一步将指令周期划分成若干个机器周期(又称 CPU 周期)。通常将从主存取出一个存储字所需的最短时间定义为机器周期,而每个机器周期又可包含若干个时钟周期。

指令周期的机器周期数以及每个机器周期所包含的时钟周期数并不一定是固定的,和具体实现有关,通常分为定长指令周期和变长指令周期两种。

2.3 寄存器传送语言

每条指令的执行过程都可以分解为一组操作序列,进而可分解为一组微操作序列。其中“操作”是指功能部件级的动作,微操作是指令序列中最基本的、不可再分割的动作。

结合C++的原子操作我们能更好理解微操作