FPGA时序分析(三)--基础知识

前言

通过前两篇文章,相信大家对于时序有了一个大概的认识,这篇文章讲解如何分析时序路径,理解一些概念。因为后续看时序报告时,FPGA工具也时用这些概念来告诉我们时序的情况,所以这也是我们看懂时序报告,从而优化时序的基础。这篇文章将通过一个典型的时序分析模型来帮大家理解相关的概念。

时序分析模型

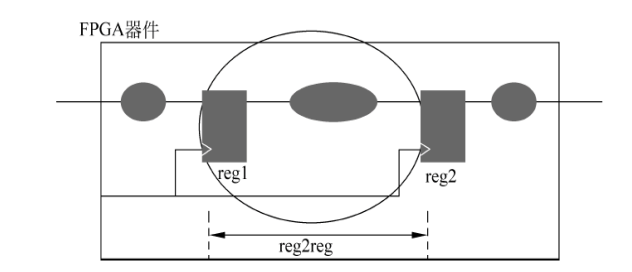

这里我们选用两个寄存器之间的数据传输路径作为分析模型。这个“寄存器到寄存器”的路径是时序分析中最本质、最核心的构建块 (fundamental building block)。 无论数据是从外部传输到FPGA输入端口(输入路径),还是FPGA驱动信号到外部负载(输出路径),甚至是内部复杂的组合逻辑链,本质上都可以被建模或抽象成一个“发起寄存器(Source Register) → 组合逻辑+布线 → 捕获寄存器(Capture Register)”的基本结构。 深刻理解并掌握对这个基础模型的时序约束与分析(包括建立时间和保持时间的要求),是为理解FPGA设计中所有其他类型时序路径奠定坚实基础的关键。 后续其他路径的分析规则,往往是这个基础模型在特定场景下的延伸或边界条件处理。下面的分析,就是分析捕获寄存器能不能正确的捕获到数据。FPGA工具也是这样来分析某一条路径的。

时钟路径和数据路径

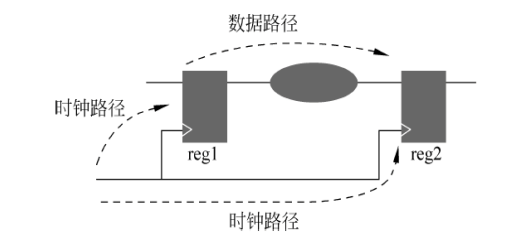

数据路径是指:从数据发起点,到数据到达点的路径,在这里的话就是从reg1的起点到达reg2的起点。

时钟路径是指:时钟到达两个寄存器时钟引脚的路径。

分析的建立时间和保持时间,其实也就是看信号在这两个路径所花的时间。数据到达reg2的时间称为:数据到达时间 (Data Arrival Time)。时钟到达reg2的时间称为数据需求时间 (Data Required Time) 。

假设reg2的建立时间和保持时间为Tsu和Th。那么可以得到下面的关系:

Setup Time Slack= Data Required Time- Data Arrival Time-Tsu

Hold Time Slack = Data Arrival Time-Data Required Time -Th

建立时间余量要想为正,意味着数据到达时间要比数据需求时间早,还得早出一个Tsu。

保持时间余量要想为正,意味着数据到达时间要比数据需求时间晚,还得超出一个Th。

那岂不是建立时间和保持时间根本不可能同时满足吗?

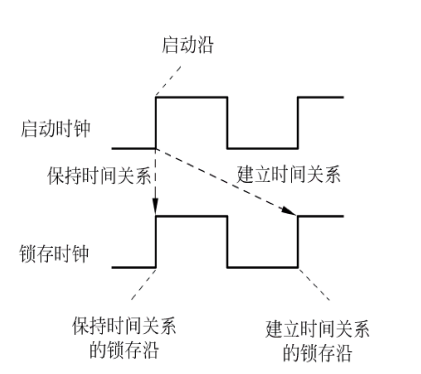

这里就涉及到一个新的概念:启动时钟和锁存时钟。

启动时钟和锁存时钟

启动时钟和启动沿,锁存时钟和锁存沿。对于建立时间来说,启动时钟比锁存时钟早一个周期,对于保持时间来说,启动时钟和锁存时钟是同一个周期。

回到时序分析的基本模型,即数据从寄存器1传输到寄存器2的过程。我们关注的是寄存器2捕获数据的时刻。一个数据通常在第一个时钟周期被寄存器1捕获,并在下一个时钟周期到达寄存器2。也就是说,该数据实际上是在第二个时钟周期被寄存器2捕获的——这正是建立时间分析要滞后一个时钟周期的原因。

而对于保持时间的分析,我们关心的是在第二个时钟周期,从前一级传来的新数据不应过早到达,以免覆盖当前正在被捕获的数据。由于捕获发生在第二个时钟周期,而可能造成干扰的新数据也产生于同一时钟周期,因此保持时间分析针对的是同一个时钟周期。这一步挺重要的,希望我有讲清楚,大家还有疑惑的话欢迎在评论区进行讨论。

建立时间保持时间余量分析

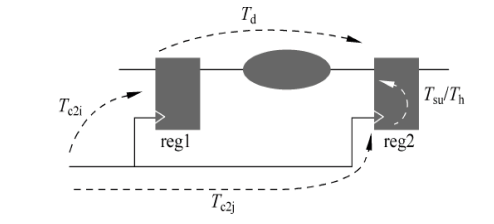

图中,Tc2i是时钟源到源寄存器regl 所经过的时钟网络延时。

Tc2j表示时钟源到目的寄存器reg2 所经过的时钟网络延时。

Td表示表示 数据从上一级 寄存器 (源寄存器) 的输 入端被锁存后 ,到下一级 寄存器 (目的 寄 存器) 的输入端所经过的时延。这里还包括了在寄存器内部的延时,在线上的延时。

建立时间余量分析

Data Arrival Time = Launch Edge+ Tc2i(max)+ Td

Data Required Time = Latch Edge+Tc2j(min) -Tsu - Clock Uncertainty Time

Setup Time Slack =Data Required Time - Data Arrival Time

=[Latch Edge+ Tc2j- Tsu-Clock Uncertainty Time ]-[Launch Edge+Td + Tc2j]

= Tc2j(min) -Tc2i(max) + Latch Edge-Launch Edge-Td-Clock Uncertainty Time-Tsu

从物理意义上讲:它是看数据需求时间比数据到达时间晚多少。那么时钟端,也就是数据需求端的延时就会增加建立时间余量,而数据端的延时会减少数据余量。所以最坏的情况就是时钟端延时的少,而数据端延时的多,这也是公式中Tc2j取min 和Tc2i取max的原因。

保持时间余量分析

Data Arrival Time = Launch Edge+ Tc2i(min)+ Td

Data Required Time = Latch Edge+Tc2j(max) +Th+ Clock Uncertainty Time

Hold Time Slack = Data Arrival Time -Data Required Time

=[Launch Edge+ Tc2i(min)+ Td ]-[Latch Edge+Tc2j(max) +Th+ Clock Uncertainty Time ]

= Tc2i(min) -Tc2j(max) +Launch Edge - Latch Edge+Td-Clock Uncertainty Time -Th

保持时间余量和建立时间余量要求正好相反,它希望的是数据到达时间比数据需求时间晚到。这也意味着,保持时间余量和建立时间余量是互斥的,一方增加另一方必然减小。

写在最后

这篇文章引入了比较多的概念,如果直接看可能会有点抽象,但有了前面两篇文章建立的认识应该会容易理解一些。之后我们就开始讲具体的时序约束了。