实战案例-FPGA的JESD204B IP核配置详解

目录

一、JESD204 配置方式:

二、JESD204 PHY 配置方式(ultrascale系列的FPGA)

三、 IP核的使用

一、JESD204 配置方式:

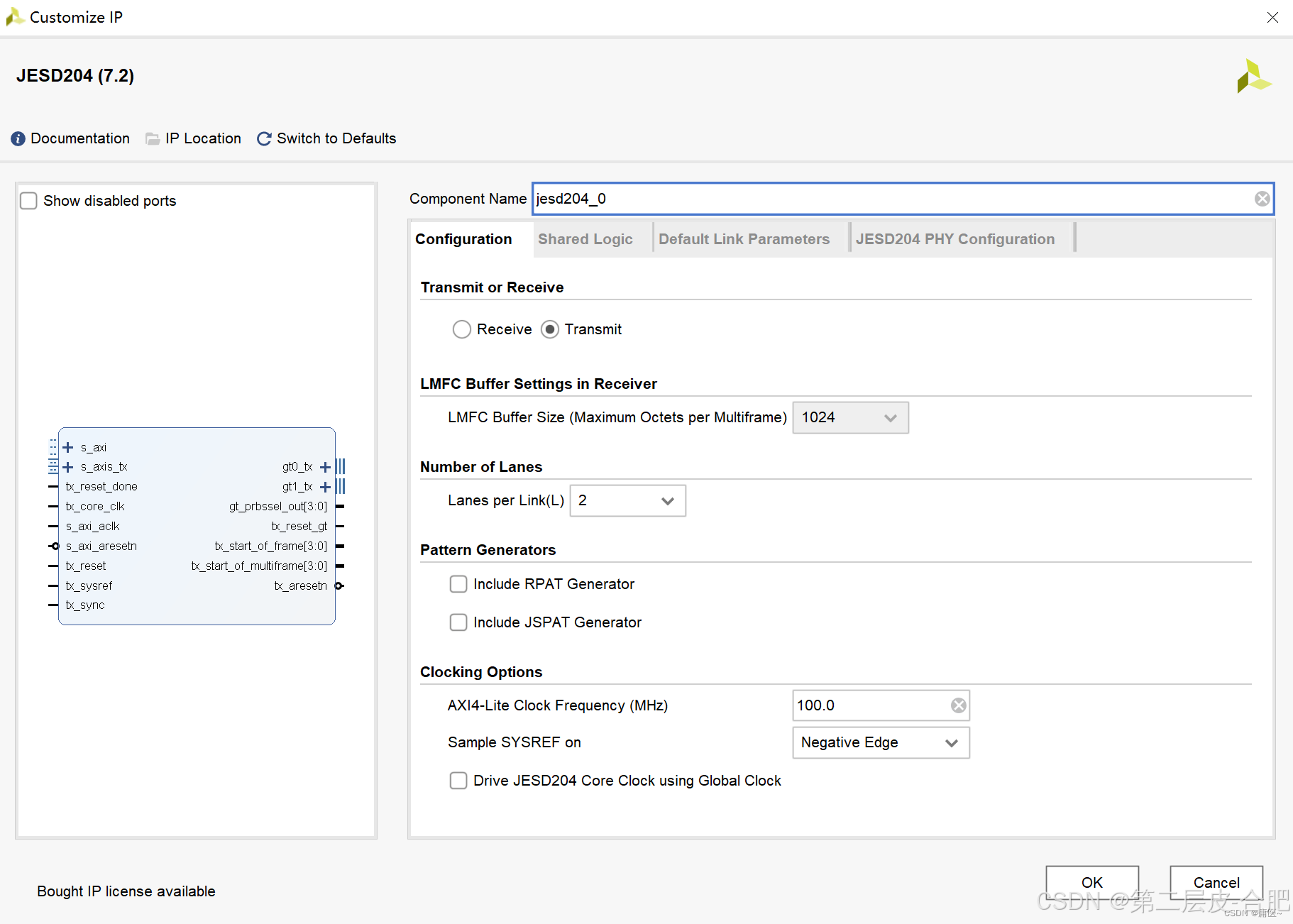

Configuration

1、Transmit or Receive: 选择是作为接收机还是发射机

2、LFMC : 默认值

3、Number of lanes : 传输的通道数,根据实际需求选择

4、pattern:模式的选择,正常情况下两个都不选

5、clocking options: AXI_lite总线配置IP核的时钟频率、以及触发位置(下降沿触发效果比较好)

6、Drive JESD204 core cloking using global clock:

时钟的分配,如果收发器的时钟频率与核时钟相同,二者可用同一个时钟源。

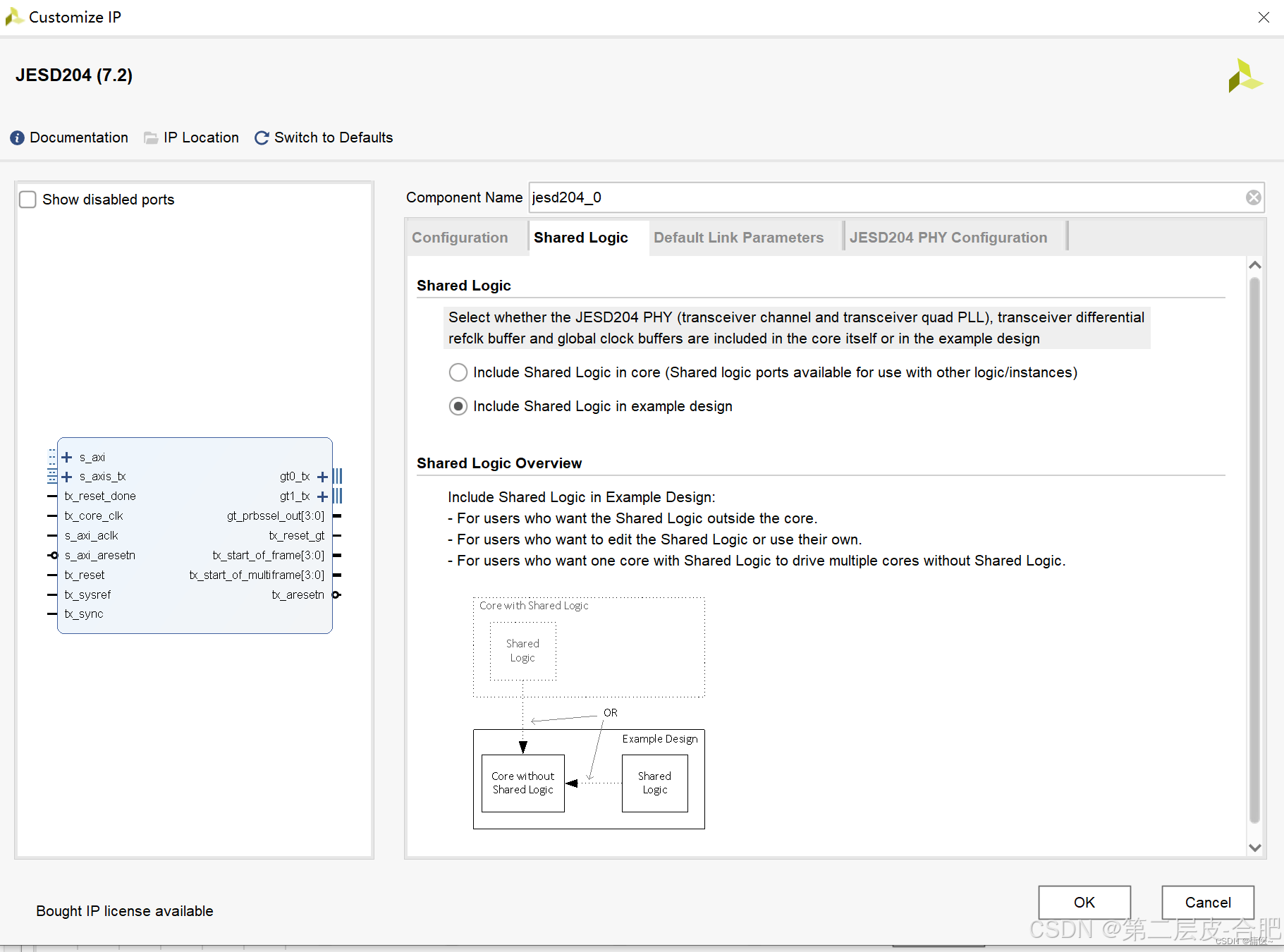

Shared logic

物理层的位置,一种是物理层在JESD204 IP里;另外一种是物理层在JESD204 IP外部,需要再配置JESD204 phy IP核进行使用。

Include shared in core 比较简单,容易配置。

Include shared logic in example design 配置起来比较复杂,但是这样接收机和发射机可以共用一个收发器。

如果只使用接收机和发射机,推荐配置为Include shared in core,如果同时接收和发射,推荐配置为Include shared logic in example design

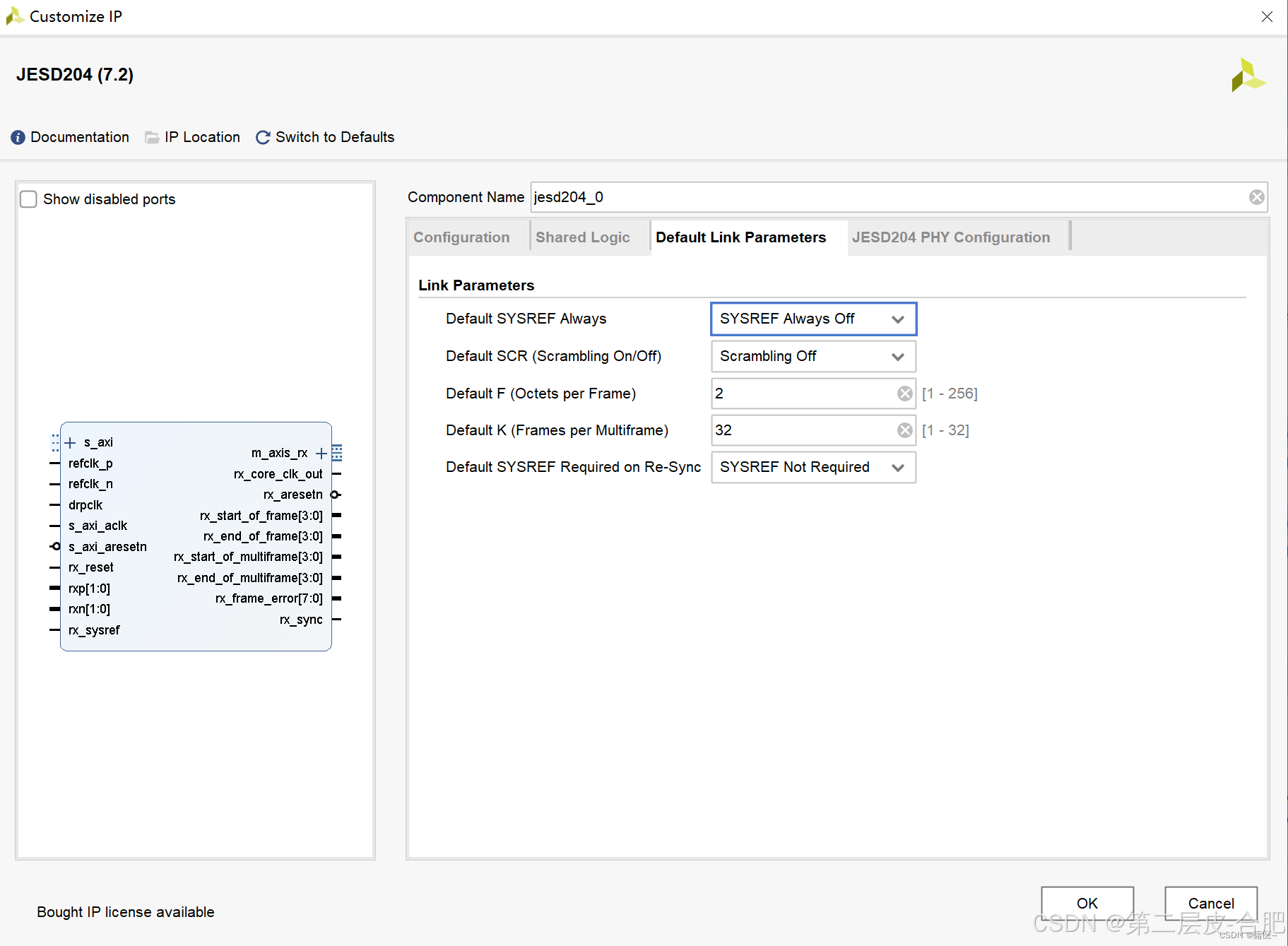

Default link parameters:

Default SCR : 是否添加扰码

F: 每帧数据包含的字节数

K: K个帧组成一个复帧,要满足ceil(17/F)

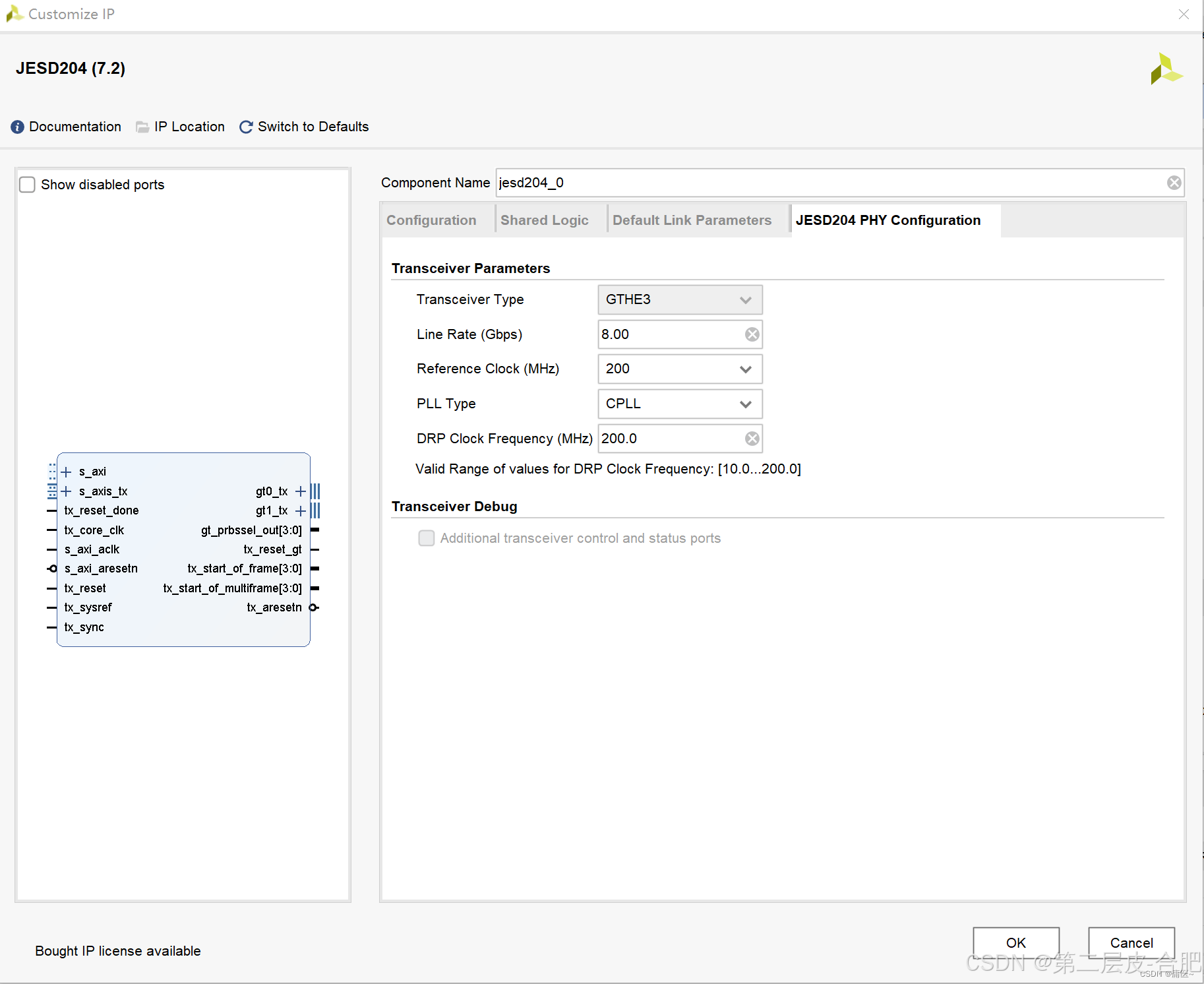

JESD204 PHY configuration

物理层的配置,选择(Include shared logic in example design)没有该配置界面。

1、type:收发器的类型,根据器件自动选择。

2、lane rate :收发器的速率

3、reference clock:收发器的时钟

4、PLL type: 收发器的类型,QPLL性能更好,适合高速率 的传输。

5、DPR clock:动态配置IP核的时钟,GTH需要该时钟。

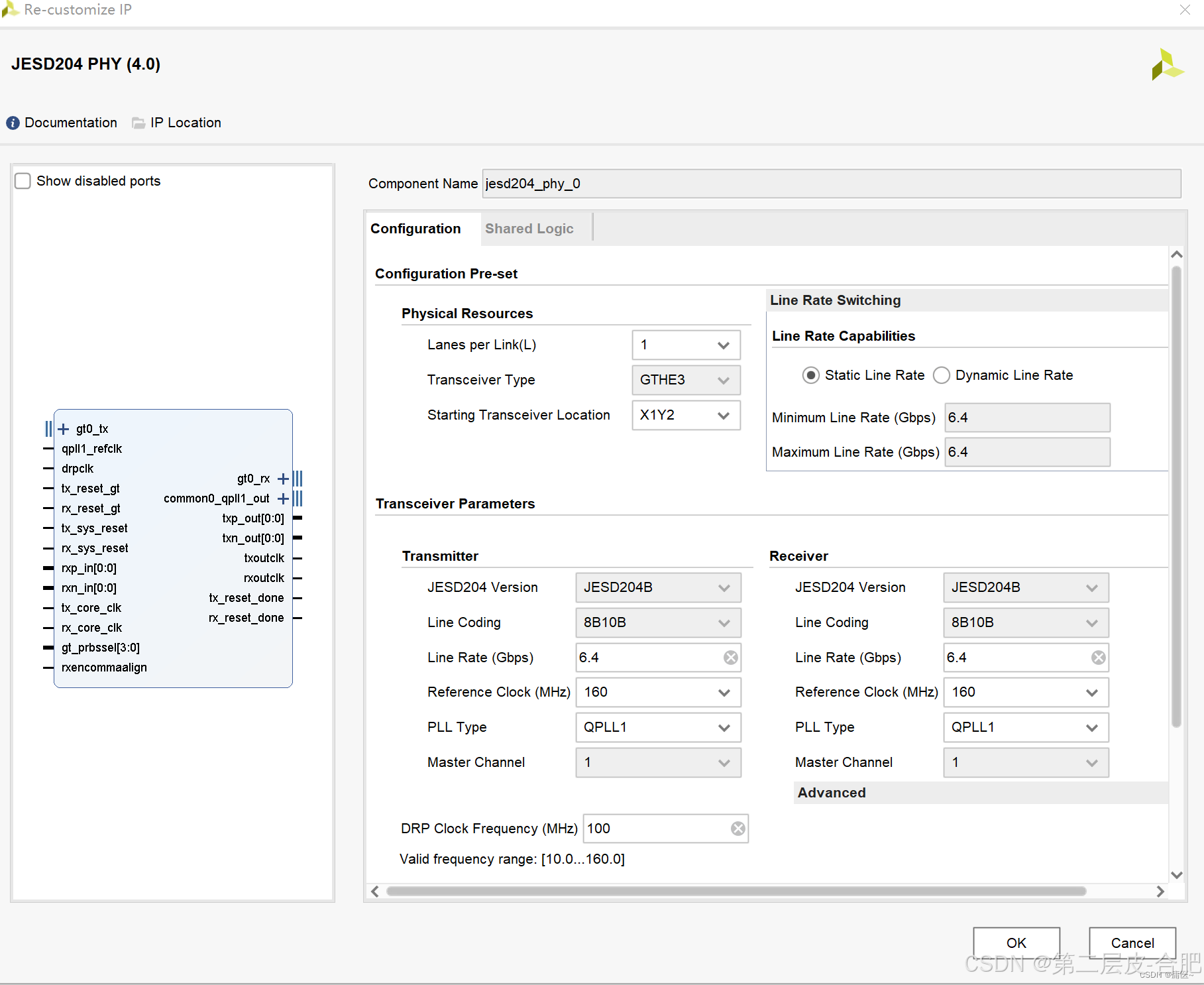

二、JESD204 PHY 配置方式(ultrascale系列的FPGA)

选择(Include shared logic in example design)需要配置该IP核

1、pre_set :这里包括通道数和收发器的位置。ultrascale需要选择收发器的位置,具体选择看对应的原理图

2、parameters: 这里和JESD204的配置一样。

三、 IP核的使用

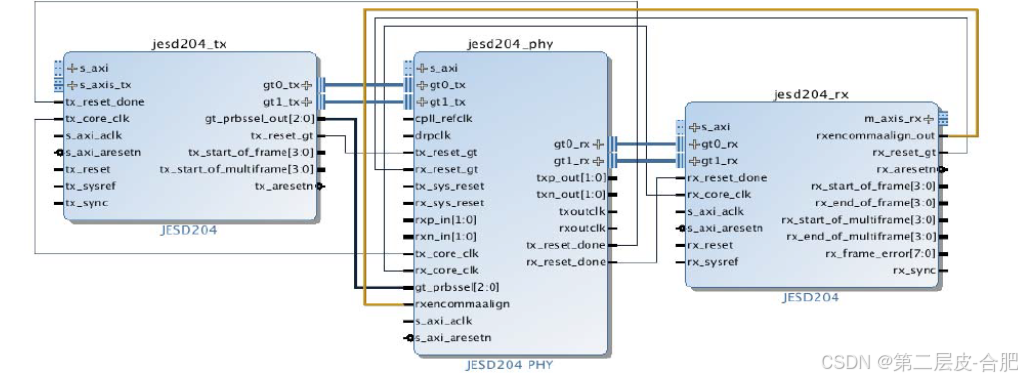

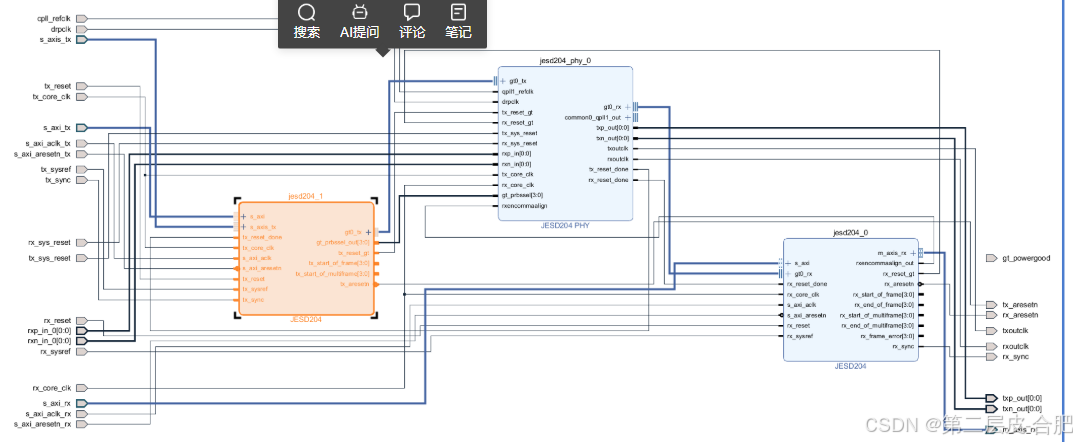

以Include shared logic in example design方式为例

首先两个 IP核间的互联。这些连接是链路层建立通道进行的通信链路。

引出输入输出的接口。

IP核工作前需要用AXI_lite总线进行配置,具体的寄存器和数值可以看官方文档查看,也可以直接用JESD204生成一个官方的例程,参考其寄存器配置。

AXI总线配置完成后 IP就可以正常工作。