基于FPGA+DSP数据采集处理平台的搭建

基于FPGA+DSP数据采集处理平台的搭建

- 项目背景

- 一、重点内容

- 二、EMIF硬件接口介绍

- 三、EMIF通信协议介绍

- 总结

项目背景

目前需要搭建一个FPGA+DSP的一个数据处理平台,FPGA这边负责逻辑控制以及数据采集相关工作,将相关数据送至DSP进行滤波、FFT等计算,将计算结果返回至FPGA进行逻辑控制,或者直接返回控制信号进行逻辑控制。

一、重点内容

其实单独做任何一方,无论是FPGA做数据采集处理,还是DSP进行数据计算都是比较简单。因为DSP优秀的计算能力,通过两者合作能够大大提高实时的处理速度(大家也知道FPGA对浮点数处理的一个鸡肋性)。所以这个平台搭建的一个关键就在于通信方案的确定。目前能确定的是通信速度应该是在几十M左右,其实最简单的话选用SPI也可以,但是害怕后续要提高速度,所以索性调查一下各种方案的速率限制。

这是豆包给出的对比,结合难度吧选用EMIF总线通信进行设计,但是之前并没有做过,所以学习吧,学硬件,学协议,在进行购置相关板卡或者绘制板卡进行实验。

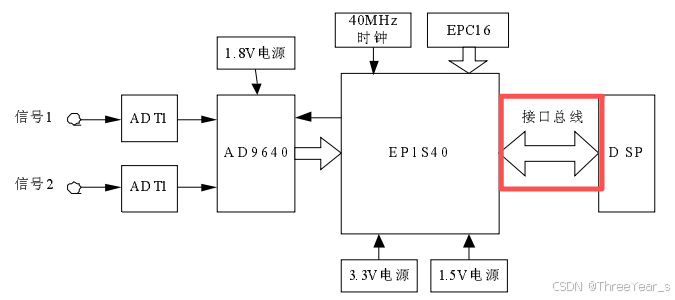

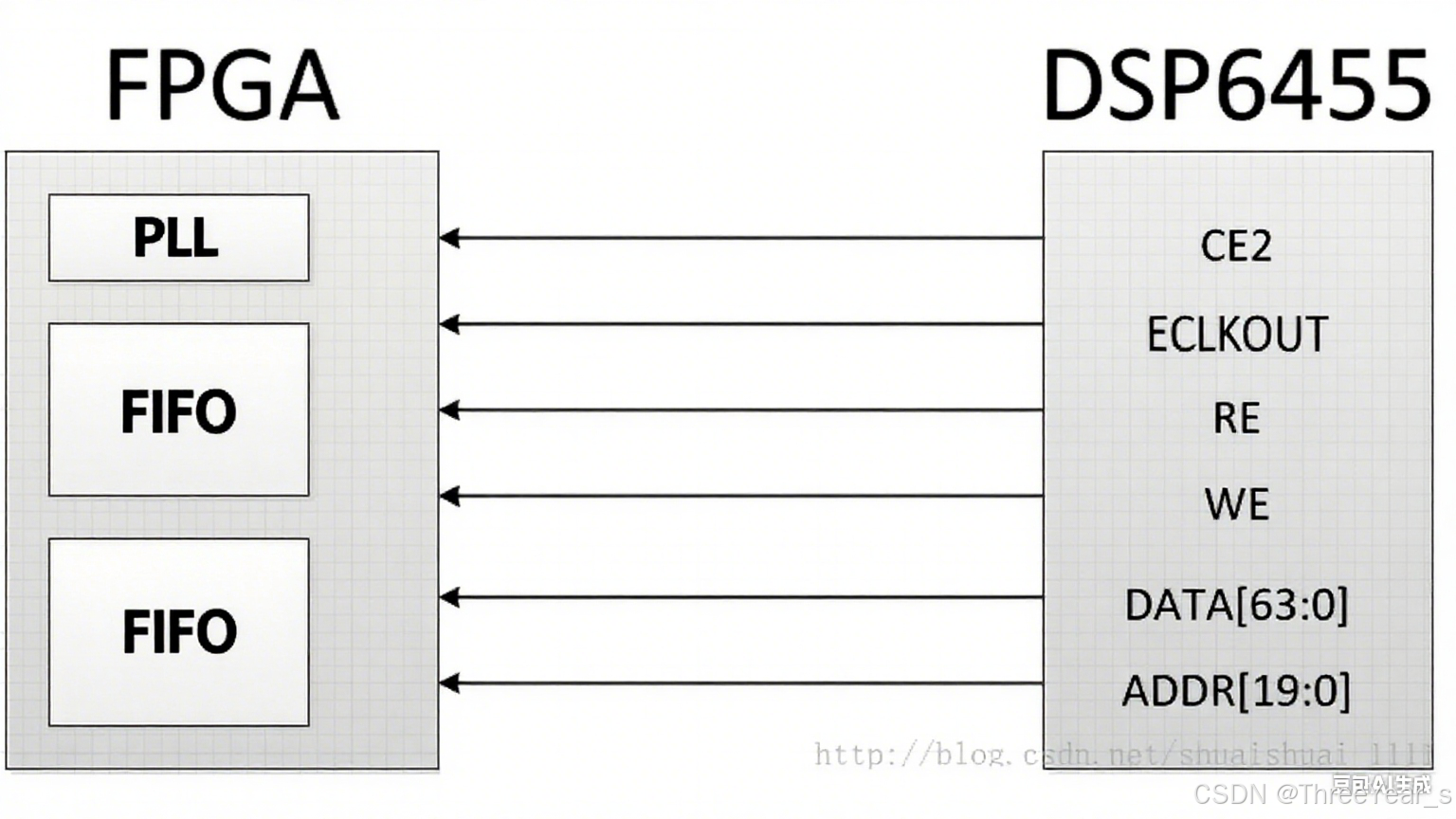

借用论文里面的一张框架图,里面的内容不做参考,只是大概是这个工作方式,目前市场上也已经有非常成熟的通信解决方案了,目前是确定想用EMIF总线进行FPGA和DSP之间的通信工作。

二、EMIF硬件接口介绍

外部存储器接口(External Memory Interface,简称EMIF)是TMS DSP器件上的一种接口,具体可以分为EMIFA和EMIFB。一般来说EMIF可实现DSP与不同类型存储器(SRAM、Flash RAM、DDR-RAM等)的连接。一般EMIF与FPGA相连,从而使FPGA平台充当一个协同处理器、高速数据处理器或高速数据传输接口。

所以EMIF是一种与存储器进行进行通

信的接口,那么DSP与FPGA进行通信就是将FPGA作为存储器进行使用,FPGA这边可以使用DDR、BRAM、RAM、FIFO等等存储方式进行数据的传输。

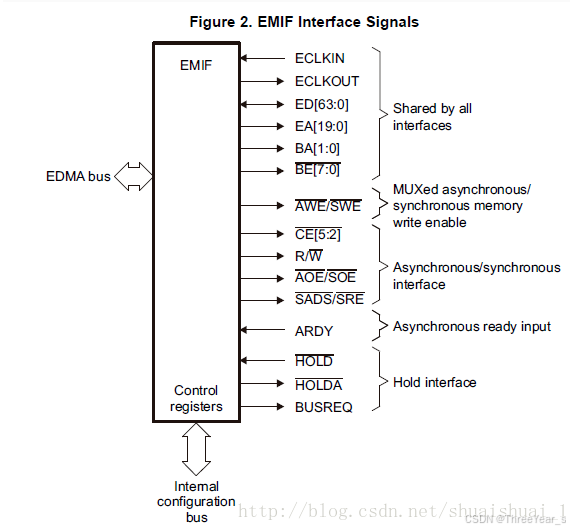

下面先来看一下EMIF接口需要什么信号线,也就是硬件上需要连接哪些线,才能完成通信,并且知道关键信号线的作用。

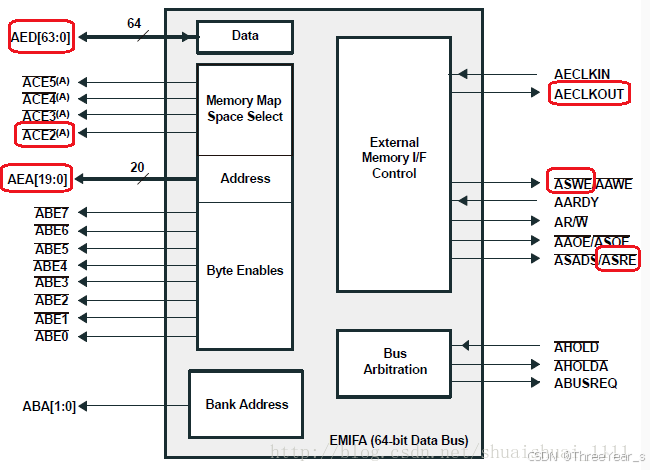

其中,并不是所有的信号线都需要了解清楚,只需要了解关键的信号线即可,比如地址线、数据线以及控制相关的信号线即可。其中红色框标出的就是其中比较重要的信号线。图中可以看出,EIMFA的地址线20bit,数据线64bit。

AED[63:0] 64位数据总线

AEA[19:0] 20位地址总线(Optional)

ACE2 片选信号(低有效)

AECLKOUT 时钟信号

ASWE 写使能(低有效)

ASRE 读使能(低有效)

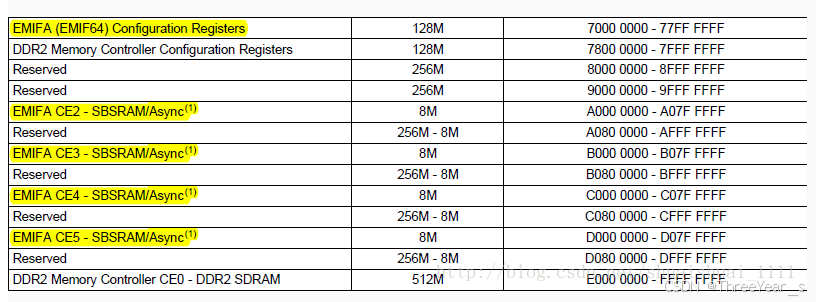

EMIFA共支持4个外部存储器,比如可以把CE2分配给FPGA,CE3分配给SRAM,CE4分配给FLASH等。 所以在这里的话CE2就是这个bank的。

每个外部存储器的寻址空间大小是8MB。20根地址线即2的20次方,也就是1MB,此外由于数据总线是64bit的,也就是8字节,故对应的寻址空间是8MB。地址的单位都是字节,不能用bit计算。

DSP与FPGA进行通信,FPGA不像传统存储器件,需要告诉现在要读取那个地址里面的数据,或者要向哪个地址里面写数据,FPGA是可以自己生成特定的地址。所以理论上DSP与FPGA进行通信,地址线是可以不用的。

如果我们使用DMA的方式进行传输,就只需要告诉传输的基地址,传输长度,目标地址等等参数。

ECLKOUT,即时钟信号的。因为FPGA工作是需要时钟激励的,即同步工作模式。

ASRE,ASWE。更熟悉的叫法是RE,WE。读使能和写使能。这个就不赘述了。

数据总线&地址总线。

三、EMIF通信协议介绍

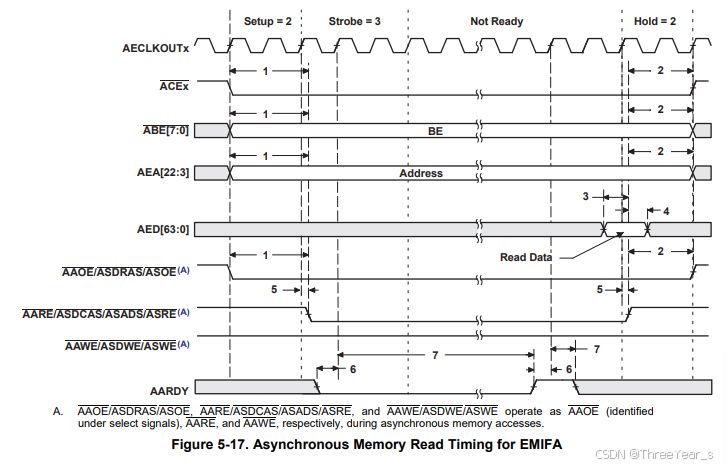

时序参数

读/写建立周期(Setup Time):

地址信号稳定后,需要等待的时间才能发出读/写信号(防止信号抖动)。

示例:读建立周期=1 → 等待1个时钟周期。

读/写选通周期(Strobe Time):

读/写信号保持有效的时长,确保数据可靠传输。

示例:读选通周期=3 → 读信号持续3个时钟周期。

读/写保持周期(Hold Time):

读/写信号结束后,地址信号继续保持的时间(避免设备提前释放数据)。

示例:写保持周期=3 → 写信号结束后地址保持3个时钟。

到时候先做仿真,时序建立没问题在上板,上板后用逻辑分析仪或者ila确定时序。

总结

对EMIF有个最简单的认识,后面在进行实际实验和深度学习。