SAR ADC 比较器的响应设计

SAR ADC的比较器是非常重要的模块,需要仔细设计。主要考虑比较器的以下指标:

1)失调电压

2)输入共模范围

3)比较器精度

4)传输延时

5)噪声

6)功耗

这里主要讲传输延时。

比较器传输延时,主要分大信号延时和小信号延时。

对于输入大信号,由于比较器增益比较大,输出直接顶到电源或地。这时候,比较器的延时就主要依赖于比较器输出的SR。设比较器高电平输出为Voh,低电平输出为Vol,比较器延时为tp,则(Voh-Vol)/2/tp=SR,则tp=(Voh-Vol)/2/SR。则增大SR就可以缩短比较器的大信号延时。增大SR的方法是增大输出级的供出或吸入电流的能力。同时减小输出级比较器的负载电容。

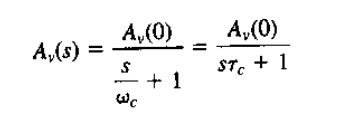

对于小信号,假设比较器是单极点系统,

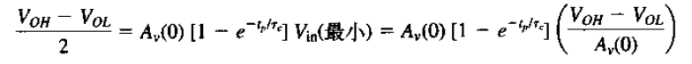

Av(0)为直流增益,Wc为-3dB带宽。定义比较器的最小输入信号为:(Voh-Vol)/Av(0),对于一阶阶跃输入信号,比较器输入信号响应为指数型响应:

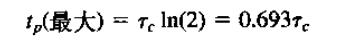

所以计算得到输入信号Vin(最小)的延时为:

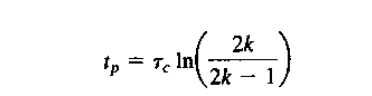

如果输入是Vin(最小)的K倍, 则有比较器延时为:

所以想减小比较器的延时,就需要增大比较器的-3dB带宽。如果一个单极点系统,增益比较高,则-3dB带宽就比较低,建立时间就会比较长,采用多级级联的方式,达到高增益、-3dB带宽频率高的效果。具体原理,详见模拟芯片设计基础专栏里的的文章《模拟电路中反馈的相关应用》。

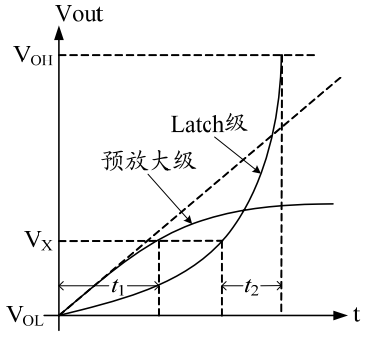

实践中,通常通过一级放大或两级预放大后,小信号变成大信号,后面用latch把信号放大到电源和地。Preamp的小信号延时加上latch的大信号延时就是总的比较器延时。

第一级或两级预放大贡献的延时一般要小于clk的半个周期。后面时间供latch放大信号到电源和地。如果第一级或两级预放大贡献的延时比clk半个周期大,可以适当改变clk的占空比,使latch放大占用的时间少一些,也是可以的。