数字IC后端实现教程 | Early Clock Flow和Useful skew完全不是一个东西

数字后端零基础入门系列 | Innovus零基础LAB学习Day10

Q: Early clock flow和useful skew都是做短某段路径,这两个有什么区别呢,既然这样还用useful skew是不是有点多余了?

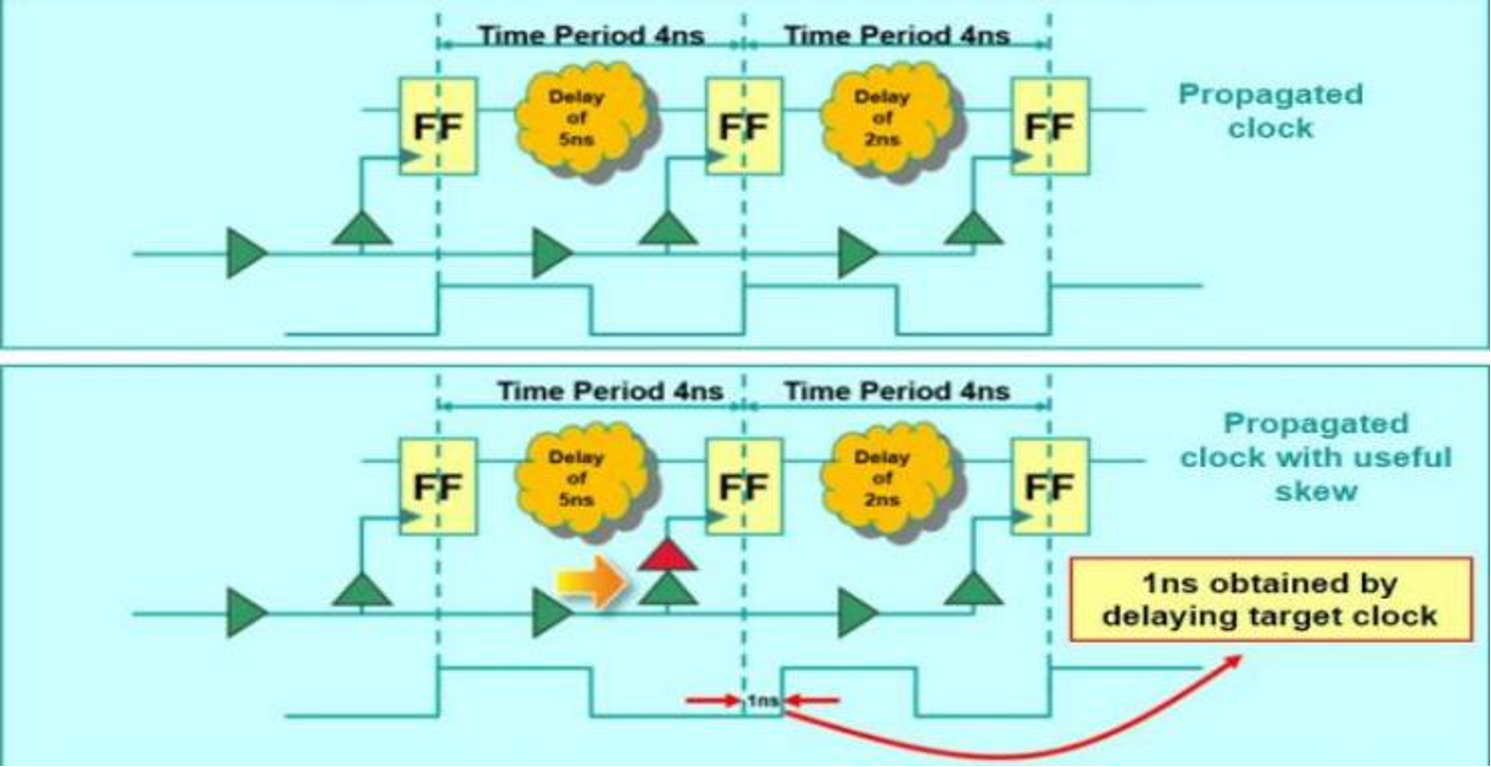

Useful Skew技术

在不使用useful skew技术,第一级FF到第二级FF的setup原来存在-1ns的violation。一个设计能跑的最高工作频率受限于WNS最大的那条timing path,即当前设计的最大工作频率小于1.0/4ns(小于250MHz)

经过借用后一级的timing margin把第二个FF的tree做长1ns后这条timing path的setup slack变成0ns,即meet了。而且我们发现第二级FF到第三级FF的setup slack虽然从原来的2ns slack变成1ns的slack,但依然还是正的slack。

也就是说使用useful skew技术后该电路的最高工作频率可以跑在250MHz了。

数字后端设计实现之自动化useful skew技术(Concurrent Clock &Data)

useful skew技术的核心是利用前后级的timing margin(时序裕量)来改善时序,提高电路最高工作频率。

在实际后端项目中我们还会使用useful skew技术来优化congestion和hold violation。也就是我们一直说的hold violation乾坤大挪移大法。

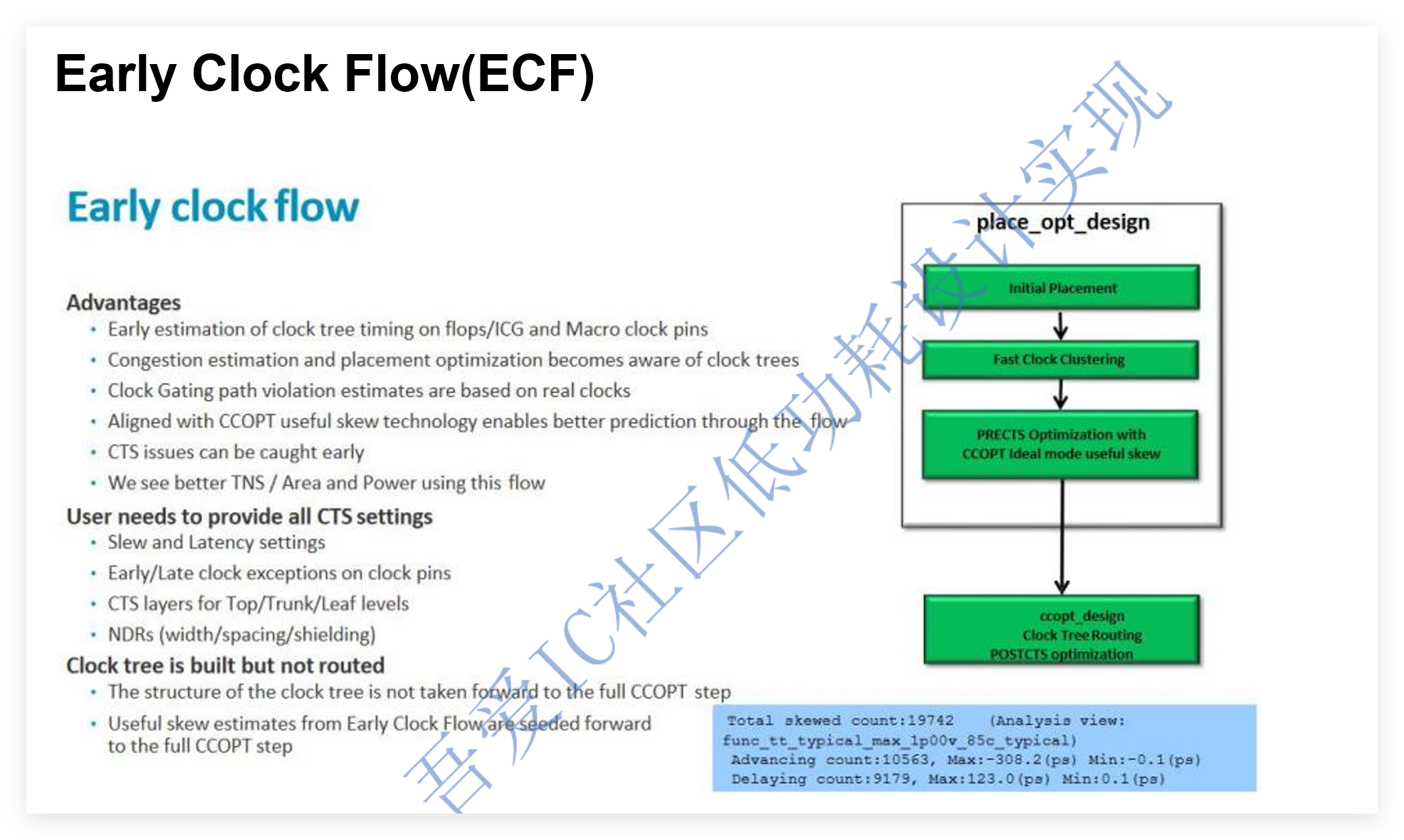

Early Clock Flow (ECF)

它是指在preCTS(placement)阶段提前做一个初步的clock tree,目的是希望工具在placement阶段就可以看到长clock tree后的相关信息,确保placement阶段和CTS后的一致性。

通过快速做一个初步clock tree,一方面可以提前看到clock net上 ndr约束带来的潜在congestion问题,这样可以提前做congestion优化

另外一方面可以提前看到Clock Gating的clock tree长度和普通寄存器(Memory)clock tree长度不一致性的情况。最典型的情况就是placement阶段到ICG enable pin的setup没有问题,但长clock tree后setup violation会高达200ps及以上。使用Early clock flow就可以提前规避这类问题。