IC ATE集成电路测试学习——Stuck-at fault And Chain(一)

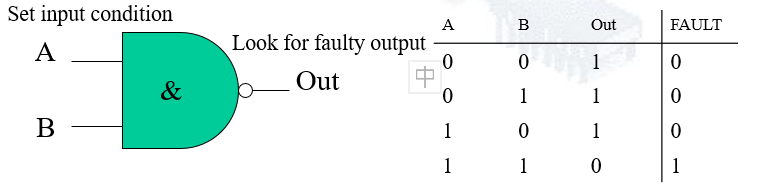

Stuck at fault测试目的:

Stuck-at fault 测试用于检测逻辑电路中可能出现的永久性故障,例如某个节点被永久地卡在逻辑“1”或逻辑“0”的状态。

工作原理:

- Simulation:在测试前,会对所有可能的stuck-at faults进行仿真,以生成相应的测试向量。

- Testing:通过扫描链将这些测试向量加载到芯片中,观测输出并与预期结果对比,判断是否存在stuck-at故障。

用途:

Stuck-at 测试是最基本的故障模型,几乎所有的数字电路都会进行这种测试,以确保电路中的每个节点都可以正确切换逻辑状态。

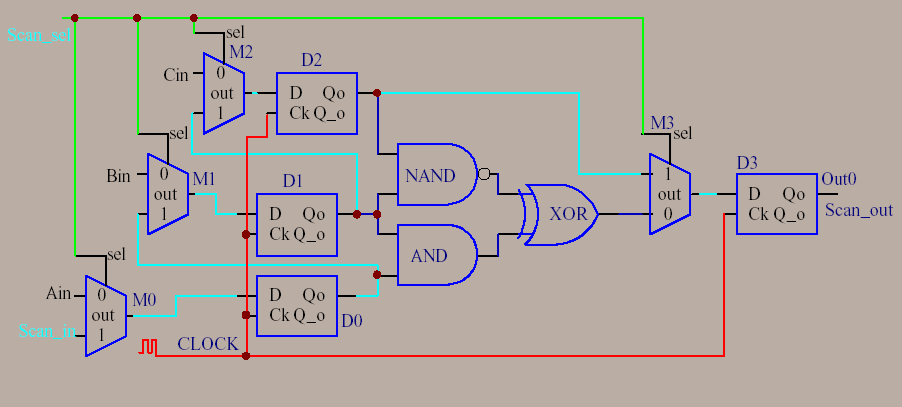

为检查该节点,Ain、Bin和Cin应分别设置为以下值:0、1、1。若该节点固定为1,则故障将传播至OUT0。

如果输入信息的信息比较复杂的话,又该如何处理呢?

在每个触发器上添加一个多路复用器,将它们串联起来

添加一个“扫描选择”信号以选择模式,并添加一个“扫描输入”以提供数据

如图,增加上复用器之后,数据从SCAN_IN串行输入,然后依次可以通过M0~M2 传输到D0~D2 这几个触发器。

也就是说,只需要很少的管脚(一般 1 根 SCAN_IN + 1 根 SCAN_OUT + 1 根 Scan_Enable),就能把几十万触发器都“级联”起来。

这就是典型的“用时间换空间”:虽然扫描需要多拍时钟才能把数据灌进去,但相比几百万个专用引脚,代价小得多。

那么为什么要加 多路选择器 (MUX)?

- 在正常工作模式下,触发器的数据输入是来自功能逻辑的。

- 在测试模式下,通过 Scan_Enable=1,触发器改为从 SCAN_IN 串行链路接收数据。

- 这样,一个触发器既能正常工作,也能在测试时作为 scan chain 的一部分。

多路选择器的开销很小(几个晶体管),相比于大幅增加 IO pin 数量和复杂性,几乎可以忽略。

SCAN是目前最流行的动态故障测试技术

——基于规则的设计

——自动化故障测试硬件插入

——组合式自动测试模式生成器

优点

——设计自动化

——高故障覆盖率;有助于诊断

——分层扫描可测试模块易于组合成大型扫描可测试系统

——面积(约 10%)和速度(约 5%)的适度开销

缺点

——庞大的测试数据量和漫长的测试时间

——基本上是速度较慢DC的测试

Chain测试目的:

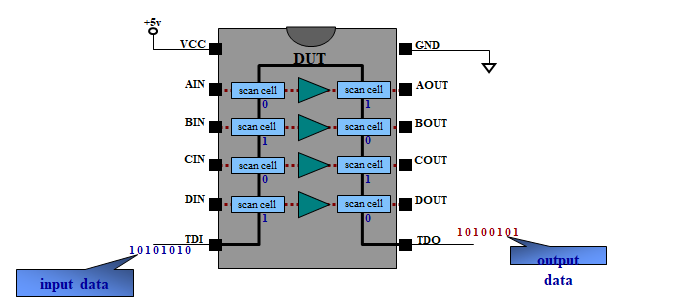

Scan chain 是一种常见的DFT技术,用于检测时序和逻辑故障。通过将芯片中的触发器(flip-flops)串联成一个长链,测试设备可以更容易地控制和观察这些触发器的状态。

工作原理:

- Normal Mode:在正常模式下,触发器按照设计的功能进行操作。

- Scan Mode:在测试模式下,触发器通过扫描链连接,形成一个可移位寄存器。测试向量通过扫描链输入,然后将内部状态移出并比较输出结果。

用途:

通过扫描链,可以捕获逻辑电路中的组合逻辑错误和时序故障,这些错误可能会导致芯片在正常操作中出现故障。

带有扫描功能的设备还允许通过扫描链加载数据并将其存储在扫描单元中。然后,这些数据会通过功能逻辑进行处理,改变输出扫描链中存储的值。之后,可以通过从扫描链中移出数据来检查输出扫描数据。

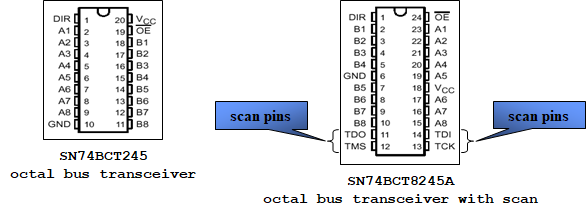

以下分别为有scan 管脚的封装和没有scan 管脚的封装

Chain 和Stuck 的区分:

Chain 只检测扫描通道、涉及元素:Scan FF (flip-flop) 本身、scan 多路复用器(scan/func 切换)、SI/TDI、SO/TDO、SE 线、移位时钟(Shift clock),以及压缩/解压器的移位路径(若存在)。一般不经过功能组合逻辑(只是把寄存器串成链并移位)。

Stuck 既依赖扫描链又测功能逻辑、向量先通过扫描链装入(shift),然后通过一次功能时钟 capture 让信号穿过组合逻辑,随后将响应移出并比较。

涉及元素:Scan FF(用于载入/捕获)、组合逻辑网表(被测目标)、IO、可能的响应压缩器(MISR)等。

一般来讲,**测试时先做 Chain,再做 Stuck。**扫描链若不完整(chain fail),无法正确加载或读取 ATPG 向量,会导致 stuck-at 测试被掩盖或误报。Chain 故障可能“屏蔽”掉本应检测到的 stuck-at 故障(因为响应无法正确移出或向量无法装入)。

反之,即使 chain 完整,仍然可能出现 stuck-at 故障通过 chain 测试却被捕获为 stuck-at fail(两者相互独立覆盖不同层面)