【技术笔记】通过Cadence Allegro创建一个PCB封装(以SOT23为例)

【技术笔记】通过Cadence Allegro创建一个PCB封装(以SOT23为例)

- 一、焊盘创建

- 二、PCB封装设计

- 三、丝印位号及标识添加

更多内容见专栏:【硬件设计遇到了不少问题】、【Cadence从原理图到PCB设计】

一、焊盘创建

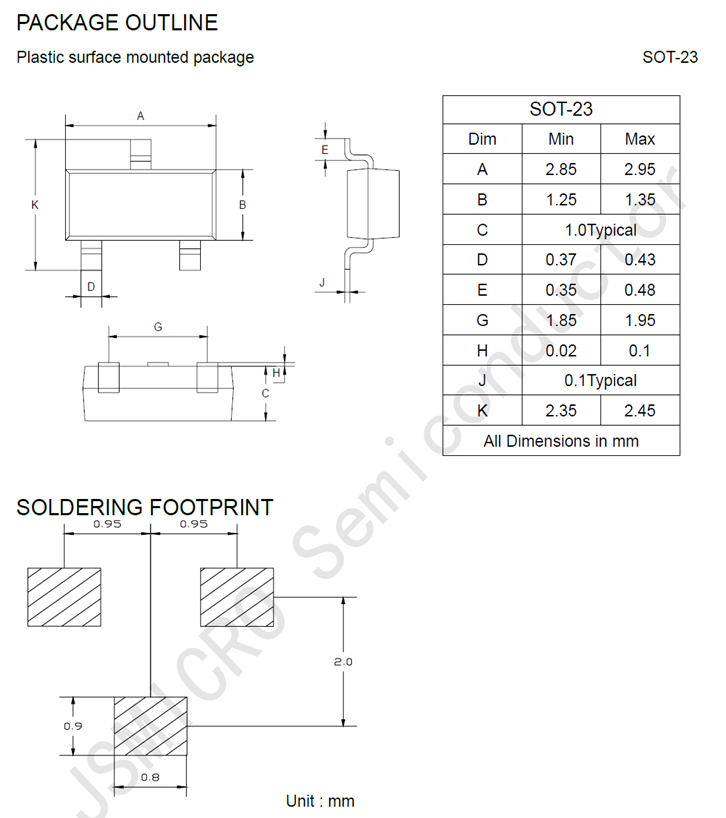

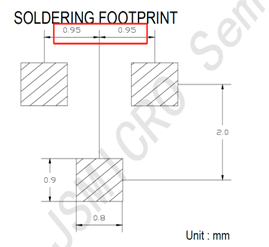

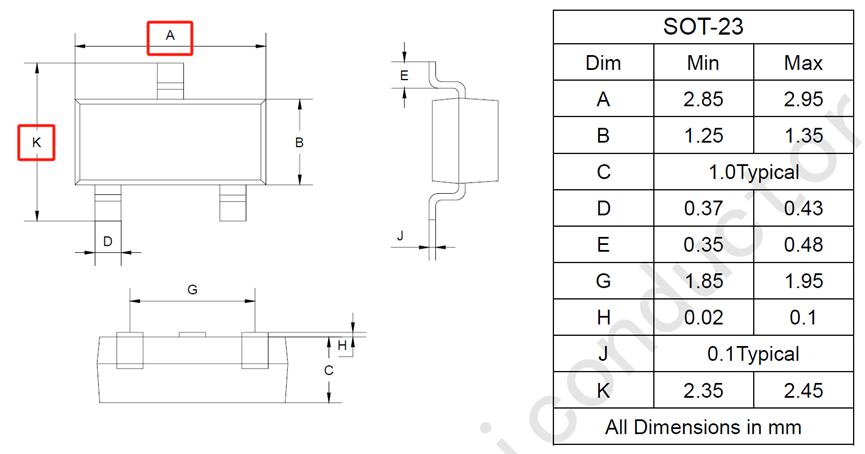

- 首先要找到元器件的相关手册,根据手册上的相关尺寸进行设计。在这里我们选择以SOT23为例,进行PCB封装的设计记录。

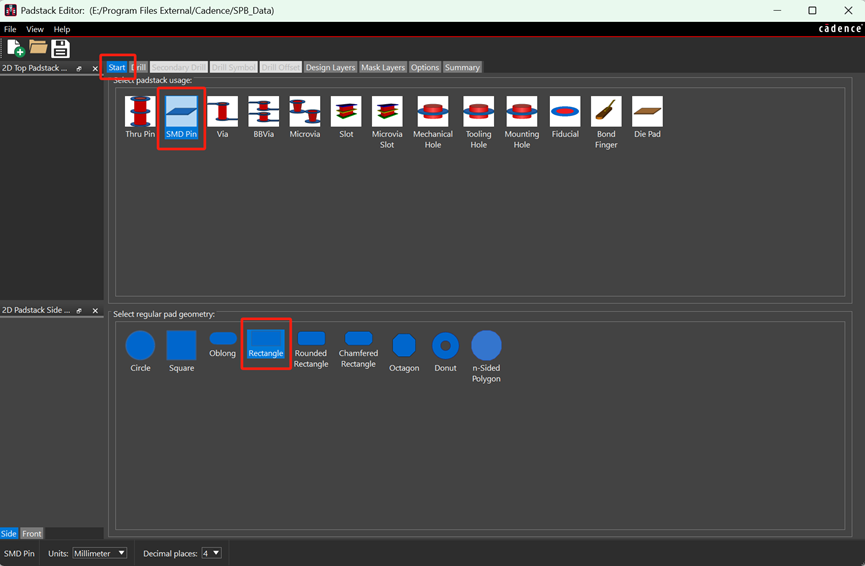

- 打开焊盘编辑器【Padstack Editor】

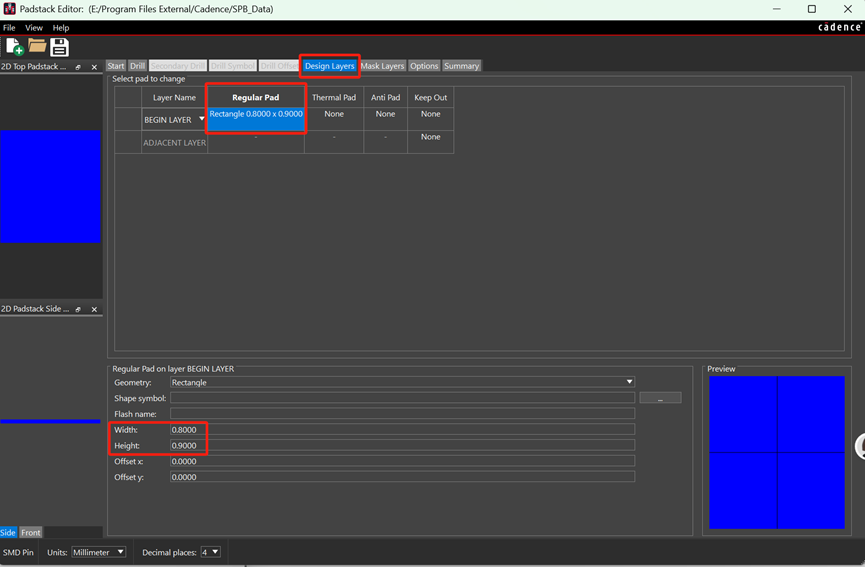

- 设置焊盘尺寸

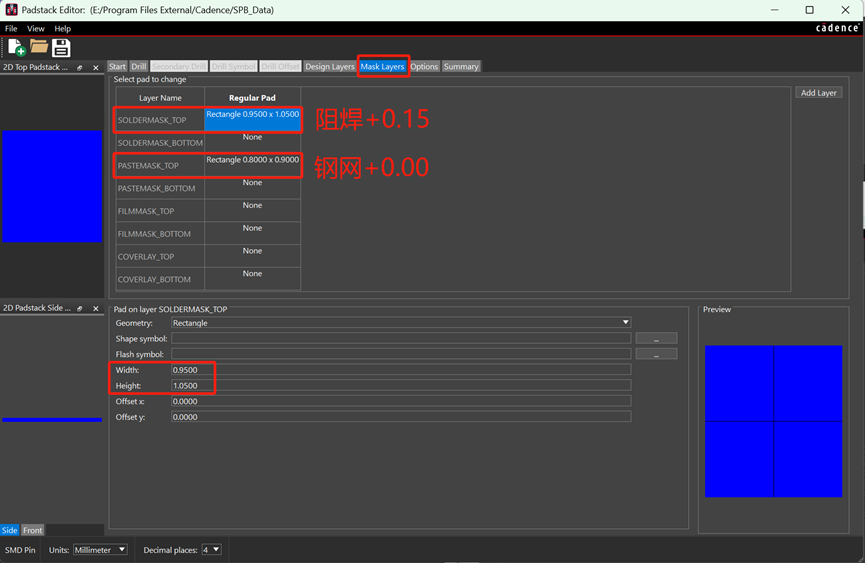

- 阻焊和钢网

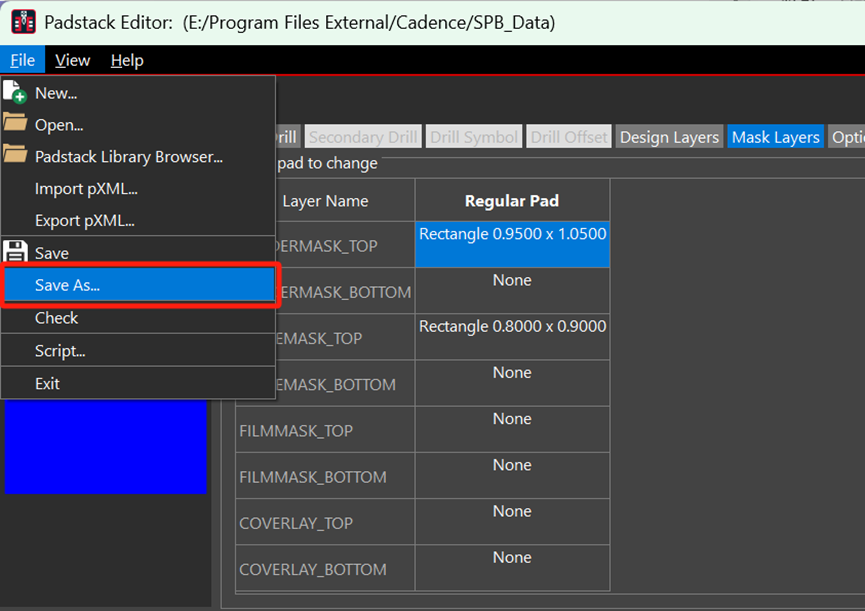

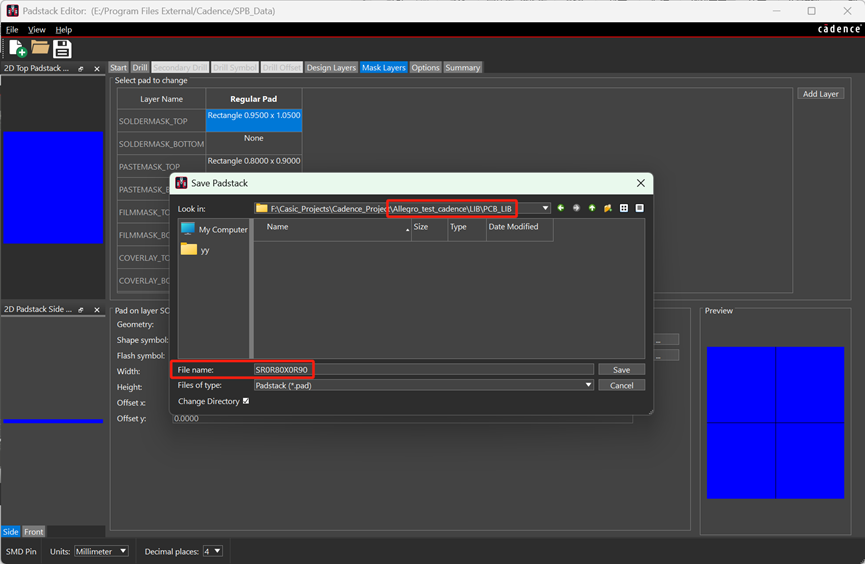

- 做好之后单独另存为

- PAD和FLASH一般放在一起,新建PCB_LIB文件夹

根据命名规则:S + R + 0R80 + 0R90

二、PCB封装设计

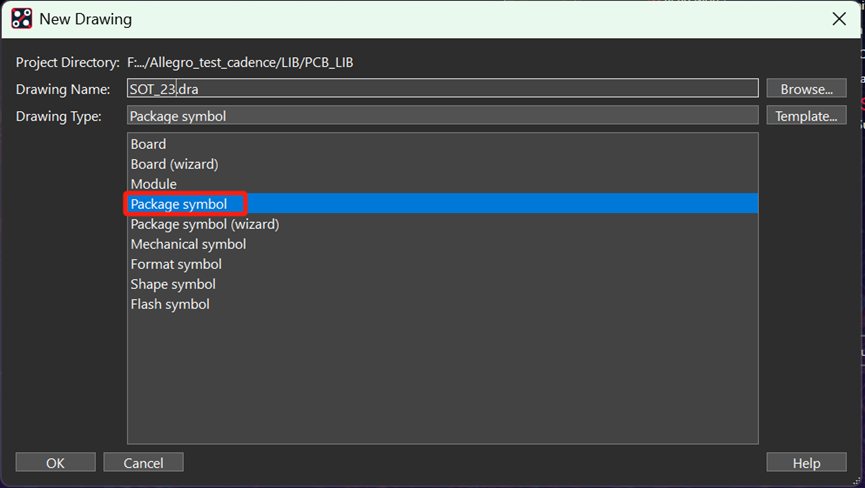

- 做封装,打开PCB编辑器【PCB Editor 24.1】,模式选择【Allegro X Designer】

- 手工新建一个封装,后缀为 .DRA,位置存于PCB_LIB,创建方式选择【Package Symbol】

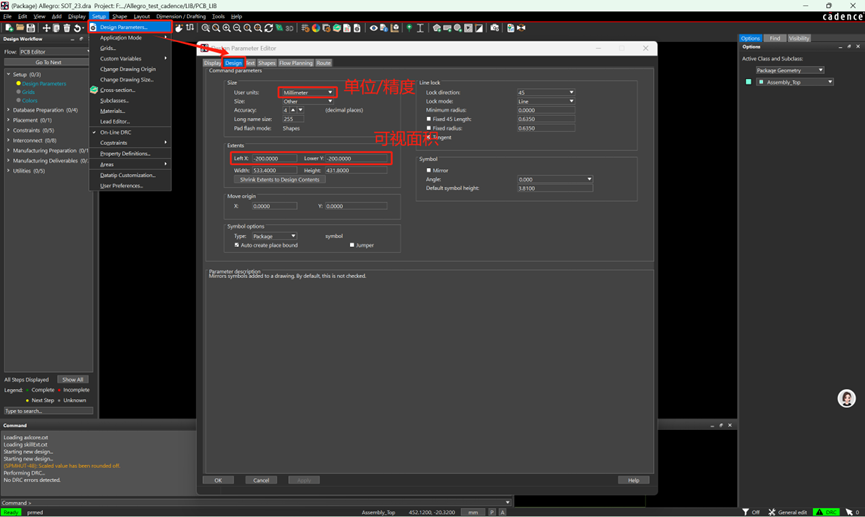

- 设置单位及可视面积

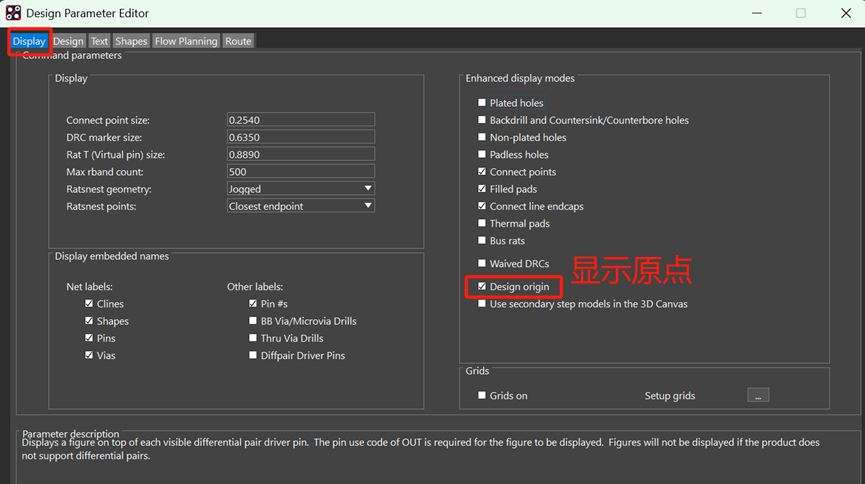

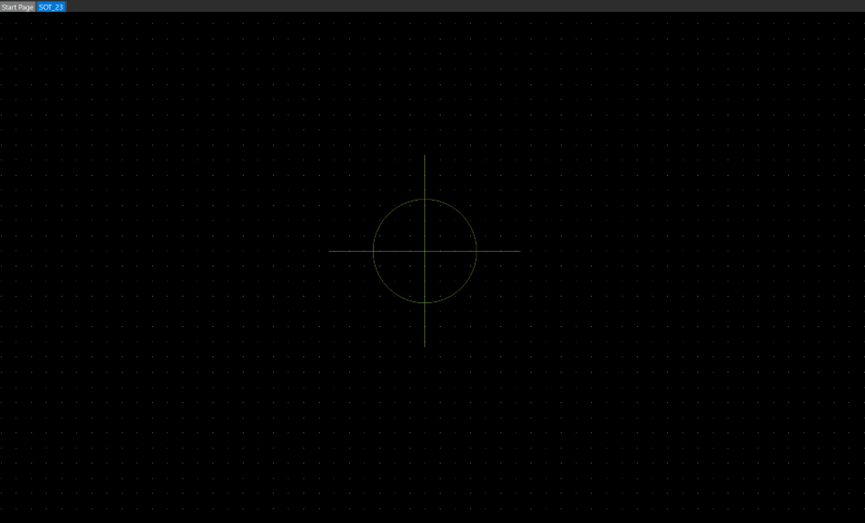

- 显示原点

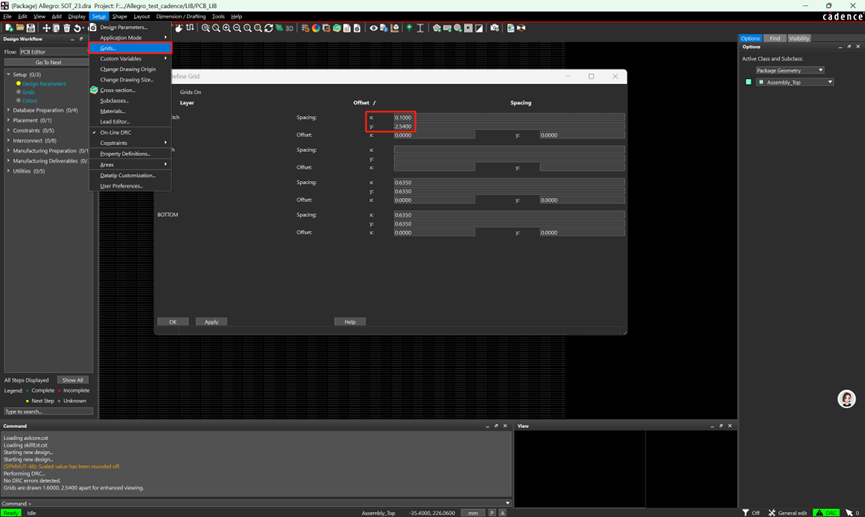

- 格点设置,默认是2.54,可以改为0.1*0.1

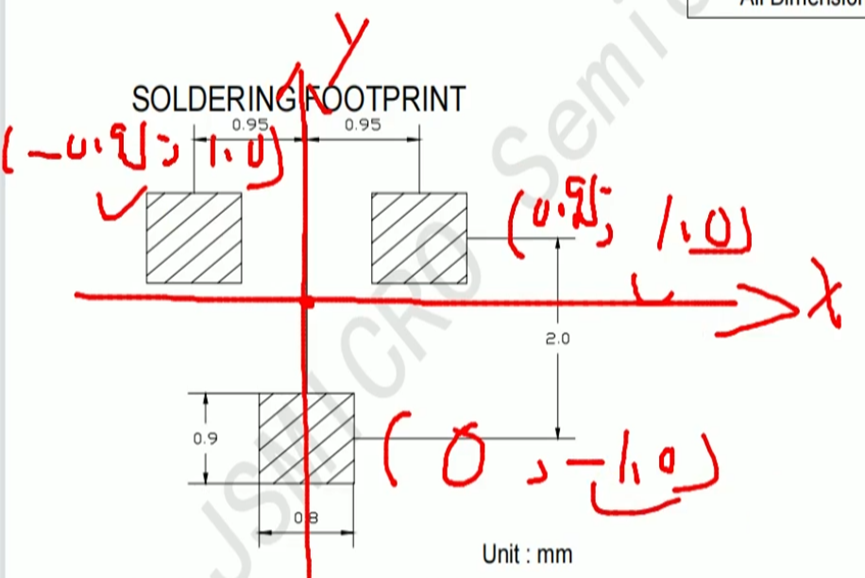

- 根据手册计算焊盘基于原点的坐标

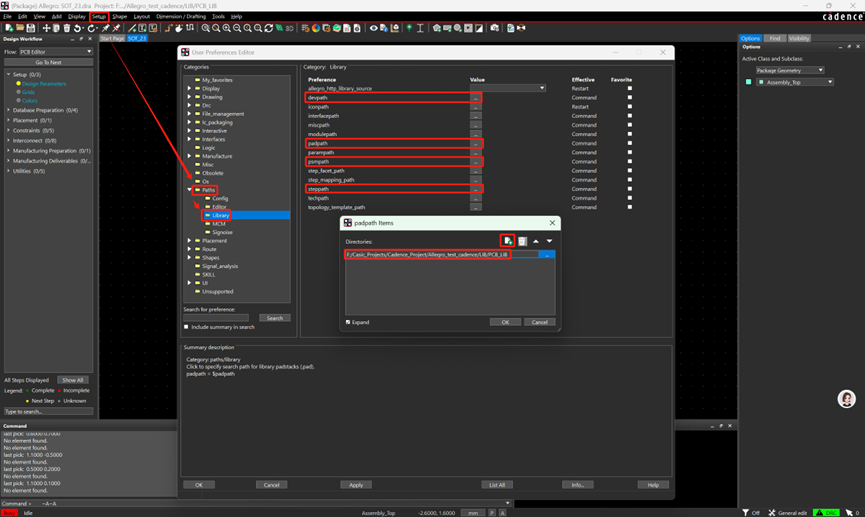

- 指定封装库路径

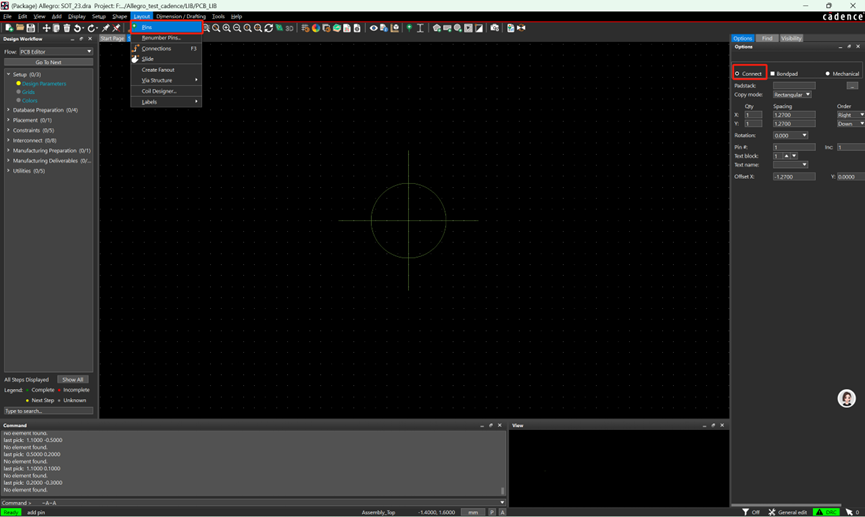

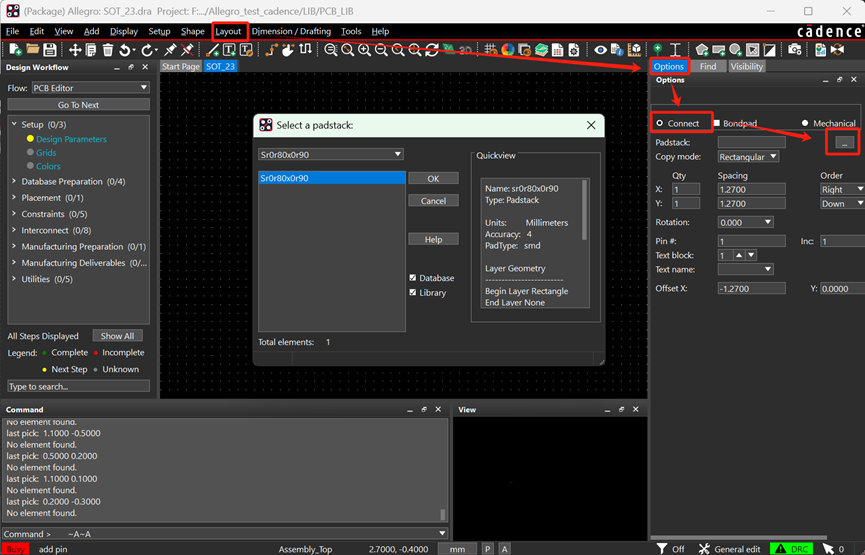

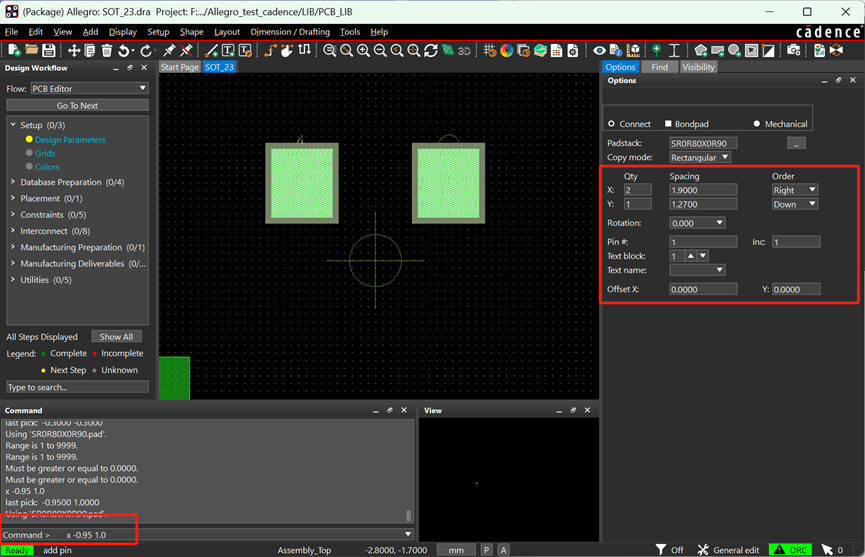

- 添加焊盘【Layout】-【Pin】

15.先放两个焊盘【Options】,Qty:横向放两个,Spacing间距,两个焊盘之间的距离0.95+0.95。

- 输入坐标(小写字母x + 空格 + 坐标)x -0.95 1.0

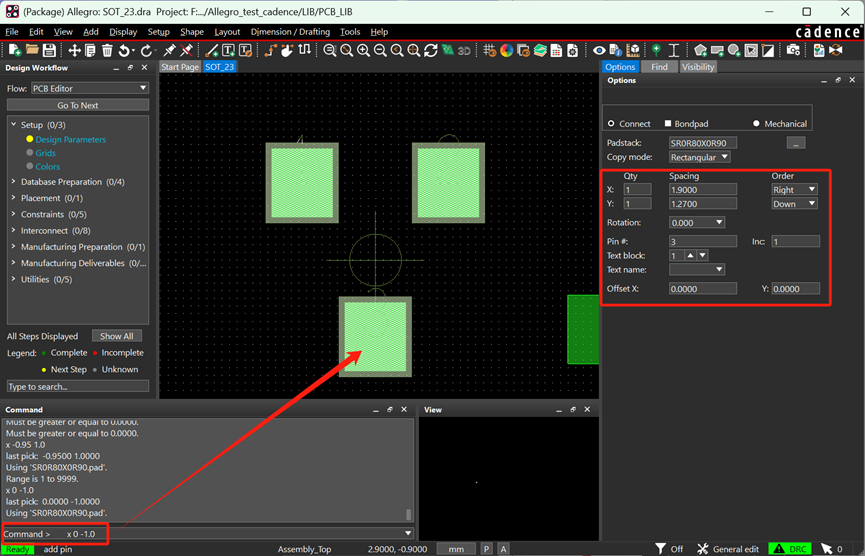

- 放置第三个焊盘

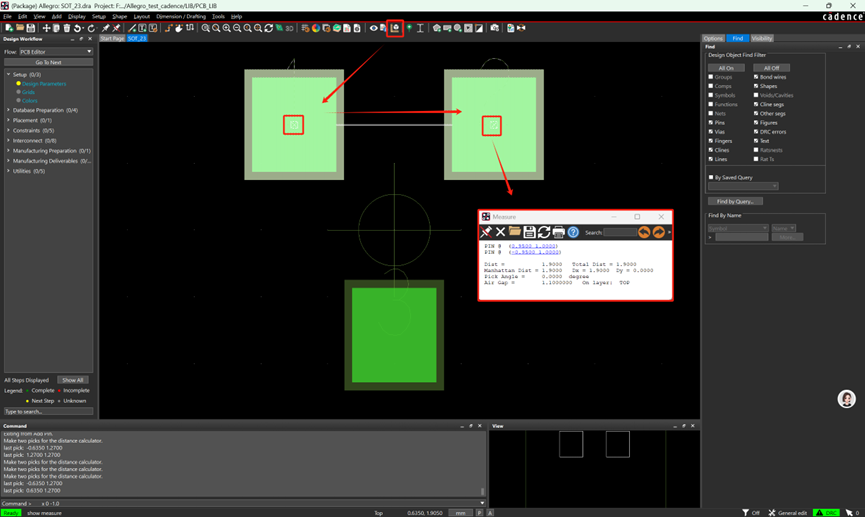

- 测量检查,点击焊盘中心

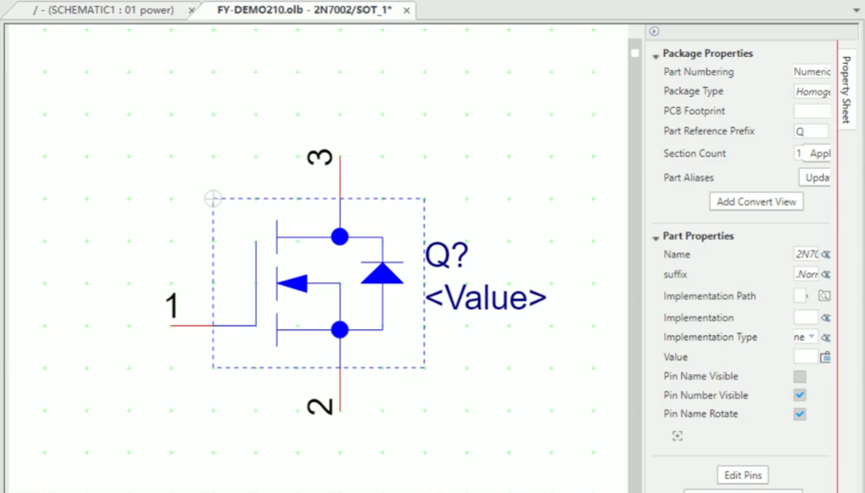

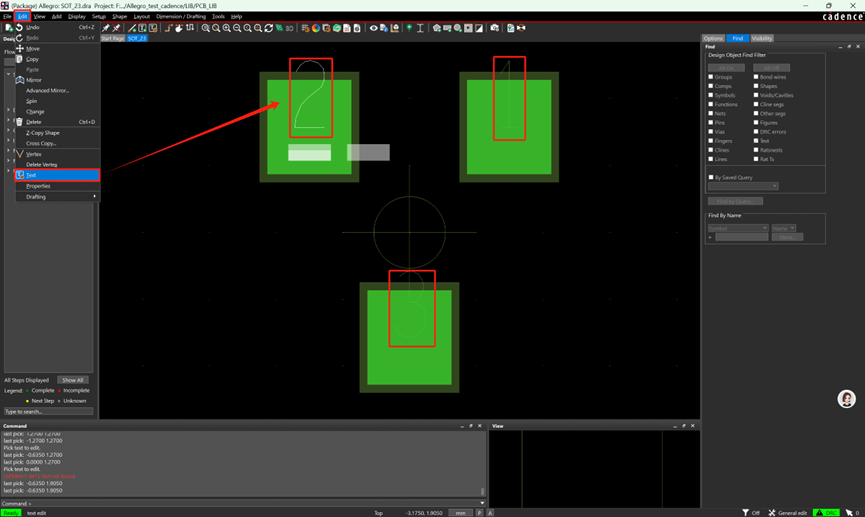

- 修改焊盘引脚号,根据手册或原理图确定

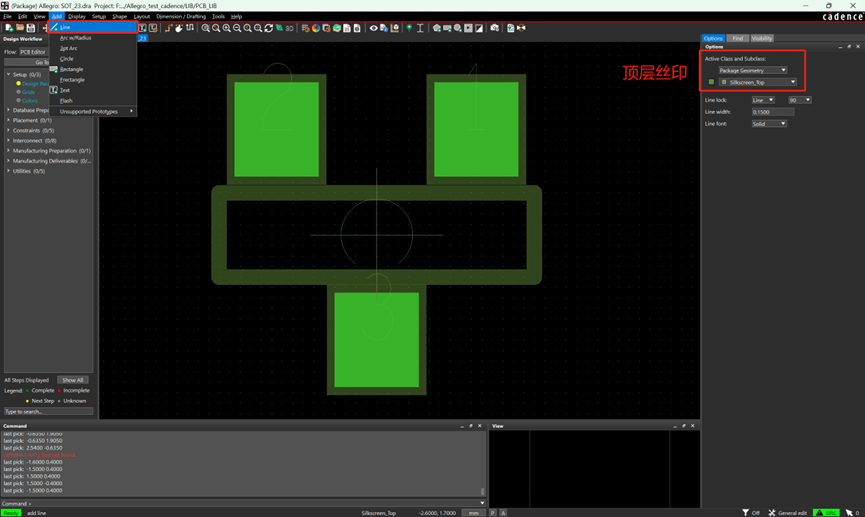

- 添加丝印,选择【Package Geometry】-【Silkscreen Top】

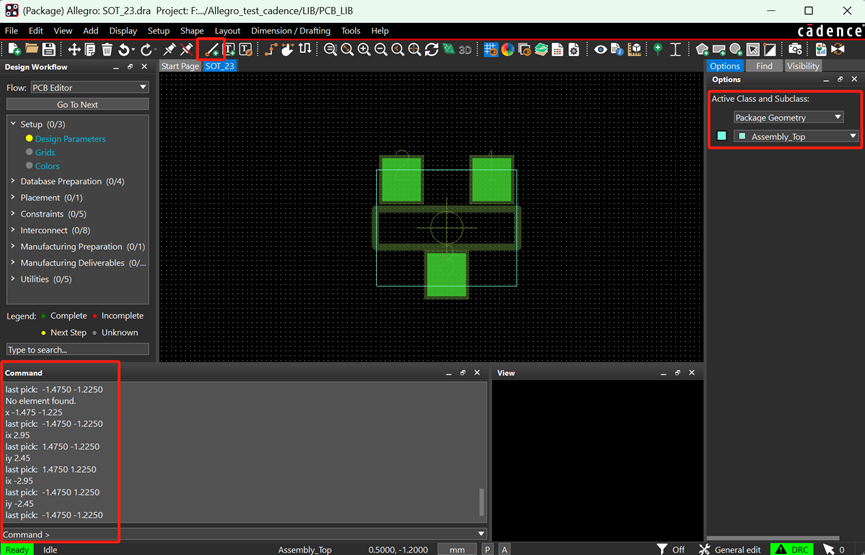

- 装配线(实际尺寸A * K 2.95 * 2.45)

装配线是给装配的工人去看的,无需印刷在PCB板上,所以可以用零线宽,2.95/2 * 2.45/2

层选择:Assembly_Top(装配层,无需印刷)

定起点:x -1.475 -1.225

偏移量:ix 2.95

偏移量:iy 2.45

位号字符分为:丝印位号(用于匹配原理图),装配位号(用于贴装放置中间),Val位号(无需印刷)

三、丝印位号及标识添加

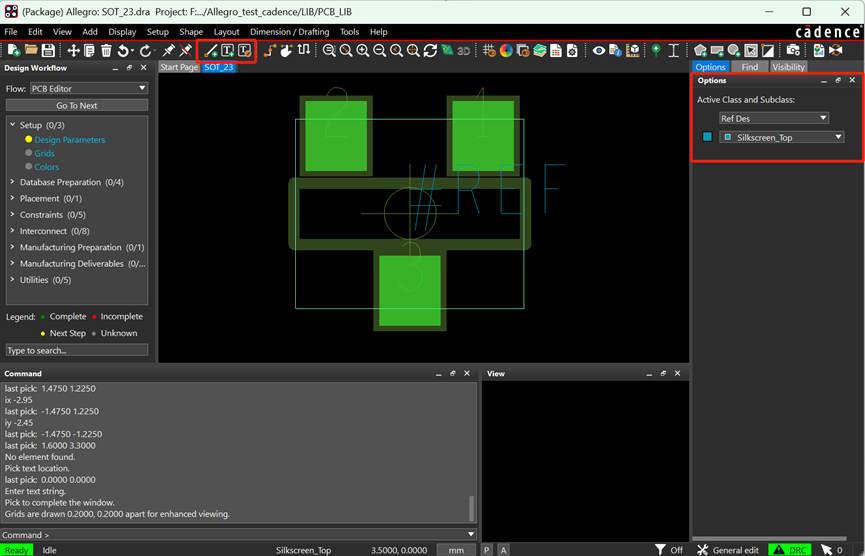

- 添加丝印位号【Ref Des】-【Silkscreen_Top】

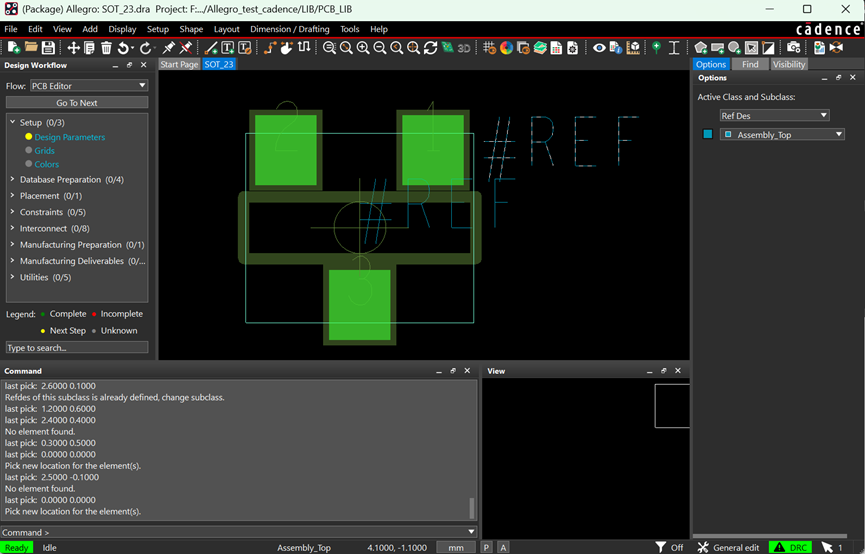

- 添加装配位号【Ref Des】-【Assembly_Top】

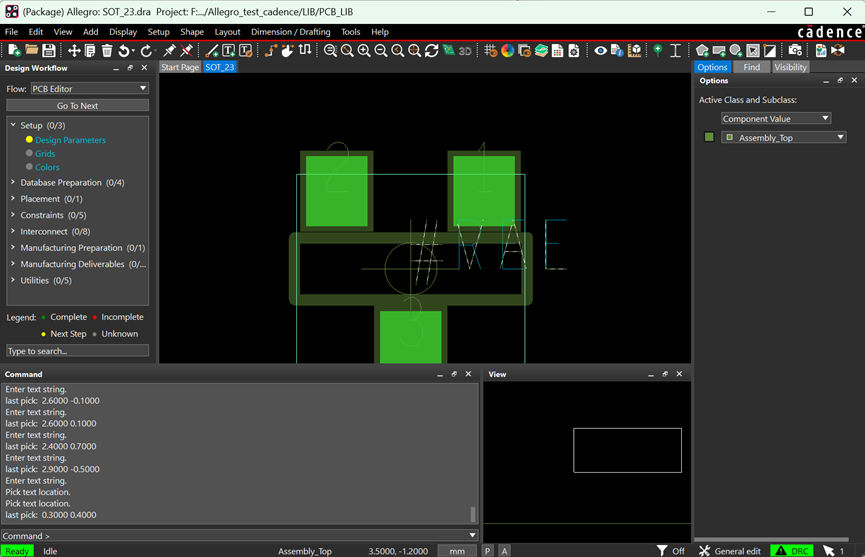

- 添加val值【Component Value】-【Assembly_Top】

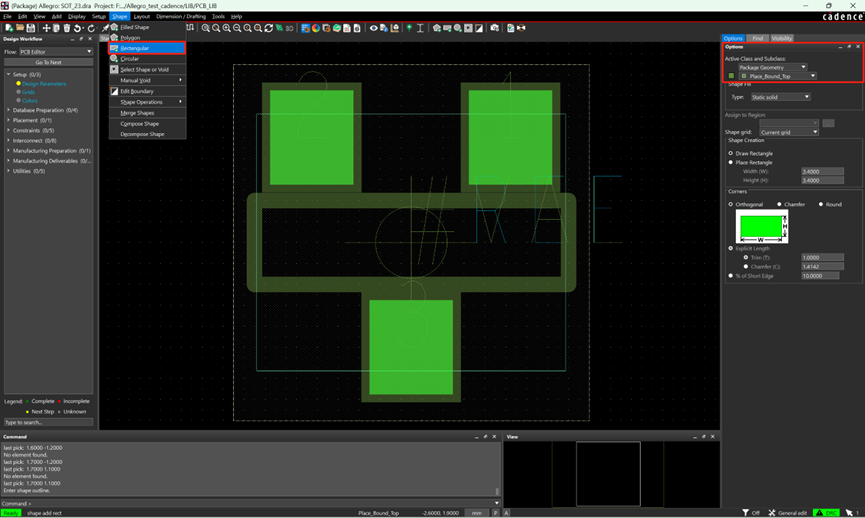

- 添加占地面积【Package Geometry】-【Place_Bound_Top】全部覆盖

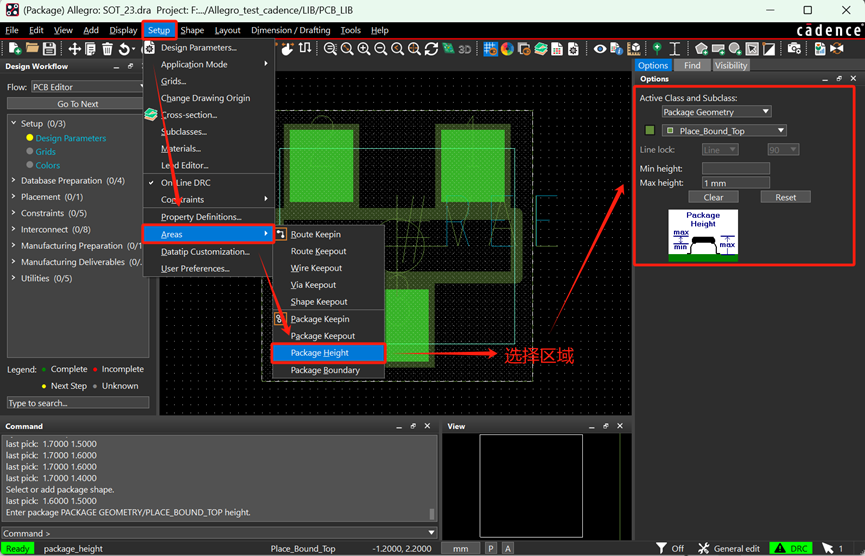

- 最大高度标识

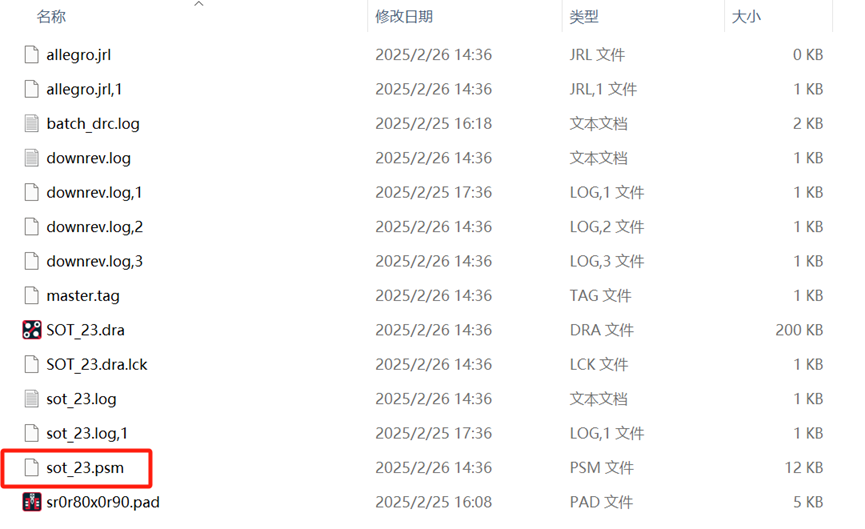

- SAVE生成.psm文件

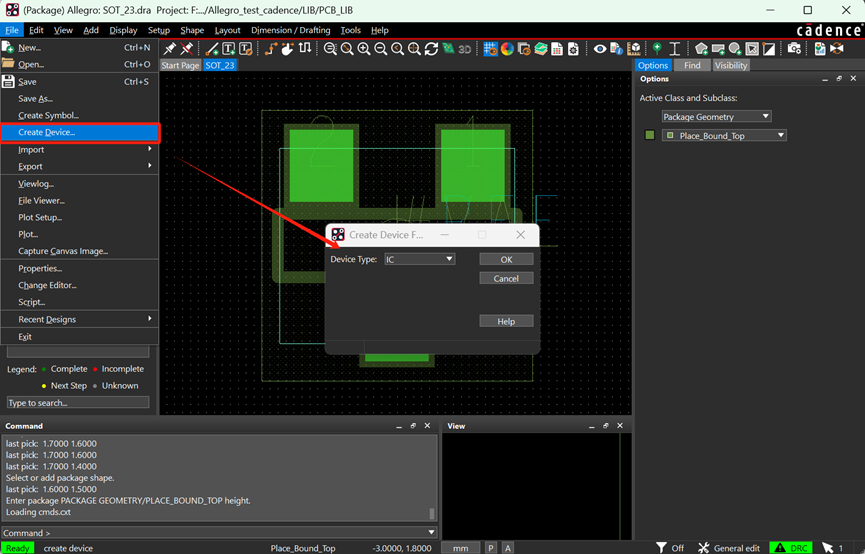

- 导出第三方网表

在PCB封装设计领域,Cadence Allegro 与 Altium Designer(AD)是两款主流的工具,但它们在功能定位、适用场景和专业性上有显著差异。

Allegro:高密度封装支持:对BGA、QFN、Microvia(微孔)、HDI(高密度互连)等复杂封装的参数化设计支持更专业,尤其适合 芯片封装(如SiP、Chiplet) 和 高速高密度PCB。焊盘堆栈(Padstack)精细控制:通过Padstack Editor可定义多层焊盘结构(如盲埋孔、背钻)、阻焊补偿、热风焊盘等,支持 制造工艺补偿(如蚀刻补偿)。可通过Skill语言实现封装设计的自动化(如批量生成焊盘、规则检查),适合企业级标准化流程。可定义复杂的物理规则(如焊盘间距、钻孔到铜皮距离)和电气规则(如阻抗控制),确保封装设计与PCB布局无缝衔接。支持与PLM(产品生命周期管理)系统集成(如Cadence Pulse),适合大型团队协作和版本控制。

最后

更多内容见专栏:【硬件设计遇到了不少问题】

Cadence 笔记传送门:【Cadence从原理图到PCB设计】