同步电路与异步电路

本文主要参考:

- <SOC设计方法与实现>

- https://zhuanlan.zhihu.com/p/35103140

- 异步电路设计-陈虹

采用同步电路设计的方法是目前SOC设计的基本要求,但在一个功能复杂的SOC系统中,难免会有异步信号与同步电路交互的问题。在由许多核组成的SOC中,通常采用“全局异步、局部同步”的设计。

同步电路设计

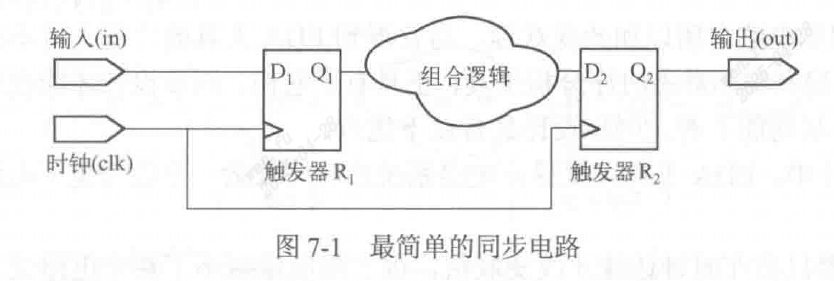

定义:电路中所有受时钟控制的单元,全部由一个统一的全局时钟控制,并建议采用统一的触发方式(上升沿触发或下降沿触发)

时序收敛条件:可以看到,同步电路的最大工作速度是由最长的组合逻辑路径延时决定的。

优点:

- 在同步设计中,EDA工具可以保证电路系统的时序收敛,有效避免了电路设计中的竞争冒险现象

- 由于触发器只有在时钟边缘才改变取值,很大限度上减小了整个电路受到毛刺和噪声影响的可能。

缺陷:

- 时钟偏斜、时钟抖动

- 功耗:时钟网络持续翻转

异步电路设计

定义:异步电路中的数据传输可以在任何时候发生,电路中没有一个全局控制时钟。因此,异步电路有时也称为无时钟(clockless)或者自定时(self-timed)电路。

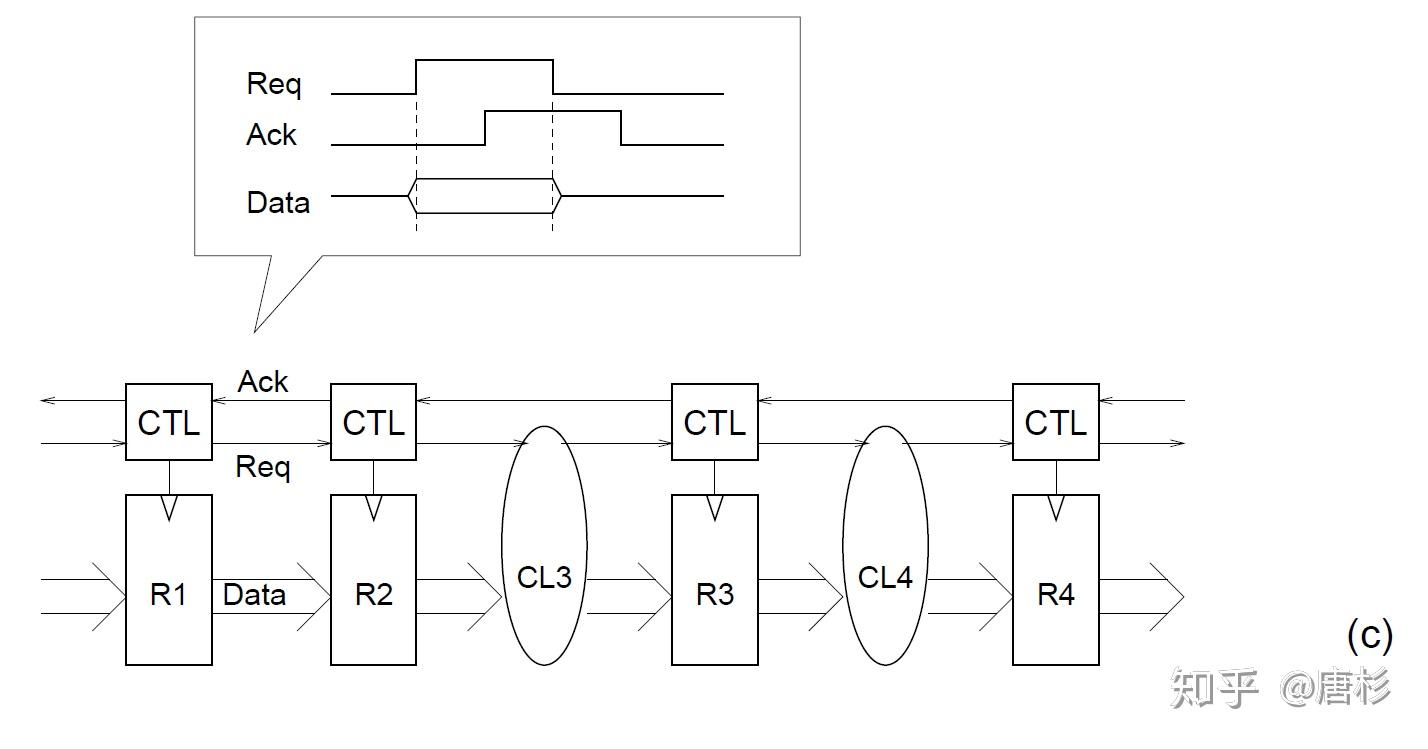

设计方法:如下图所示。在异步电路中,没有一个统一的时钟,前后级直接告知对方能否接收数据。具体来说,就是通过前后级直接发送握手信号(Request和Acknowledge)来保证数据传输的正确性。Bundled-data 是这种机制的一个标准术语,其含义是数据和控制信号捆绑在一起,而其中控制信号则起到了在同步电路中时钟信号所起的作用。

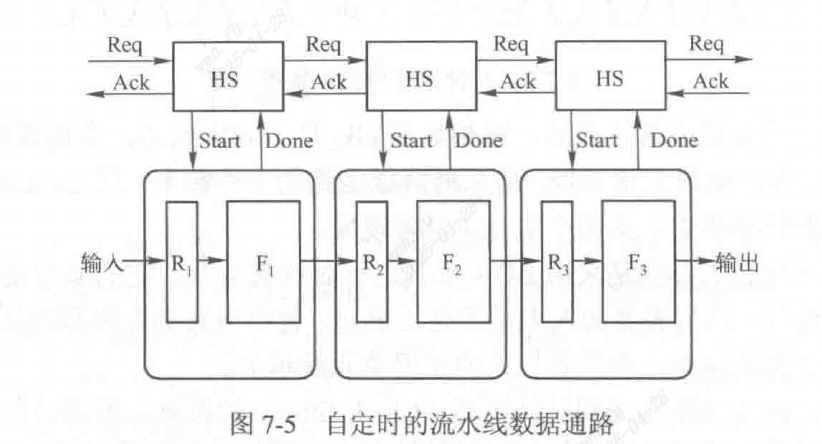

自定时方法(基于握手协议):自定时方法要求每个逻辑单元,都能通过一个开始(Start)信号来启动,从而开始对输入的数据进行计算,一旦计算完毕,它又会产生一个完成(Done)信号。自定时方法工作方式描述如下:

- 首先,一个输入字节到达,F1的Req信号上升,如果F1此时没有运行,输入缓冲器R1接收数据,HS发出Ack,激活发出输入字的前级模块

- 然后,Start信号上升,F1开始运行。

- 一段延迟后,Done信号升高,表明运算完成

- 接着,F1的HS模块向F2发出Req信号

- 由此,数据一步一步向下传播,实现了流水功能。

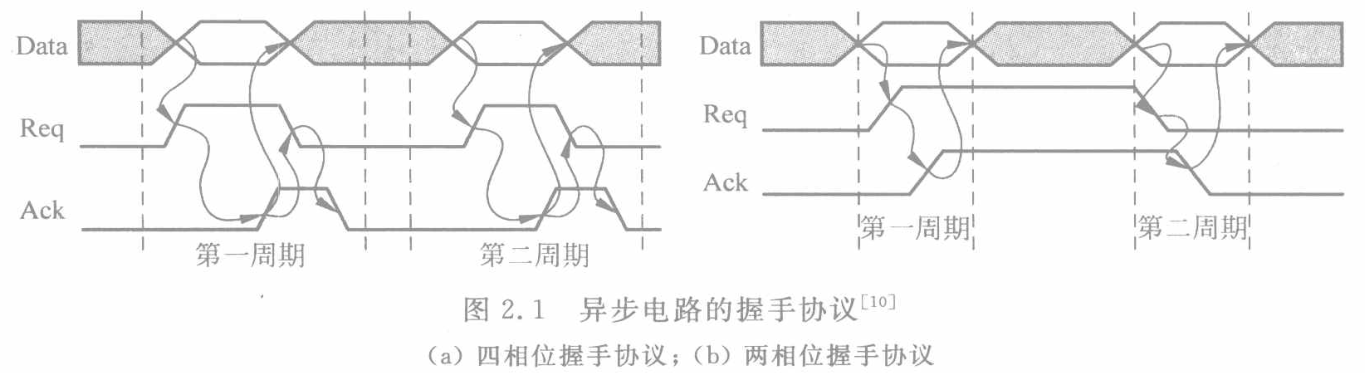

Bundled-data使用的控制协议包括两种:

- 四相位握手协议:也称为归零 (return-to-zero, RTZ)握手协议。这里的相位指的是通信动作的次数:

- 发送端准备好数据后会将请求信号 (Req)置高

- 接收端接收数据后将应答信号 (Ack)置高

- 发送端将请求信号(Req)置低作为响应

- 接收端通过将应答信号(Ack)置低来做出应答

- 两相位握手协议:四相位握手协议多余的归零翻转造成了不必要的时间和能量的损耗。两相位握手协议通过信号的跳变(toggle)来表示事件发生。典型信号包括:

- Request(请求)信号从0跳变到1或1跳变到0表示请求事件;

- Acknowledge(确认)信号同样通过跳变表示确认事件。

- 每次跳变表示一个新的事件,没有固定的“高”或“低”状态含义,只有边沿变化有效。

两相位握手协议比四相位握手协议效率要高,但会造成电路死锁,其稳定性要远远低于四相位握手协议。

- 为什么会死锁:两相位握手协议通过信号跳变来表示事件,双方必须交替产生跳变以完成通信;如果一方因条件未满足或信号未正确跳变而停止响应,另一方会一直等待确认信号的跳变,导致双方互相等待无法继续,从而产生死锁。四相位握手采用了明确的请求(置位)和释放(复位)两个阶段,信号状态清晰且可区分,双方能准确判断当前通信进度,避免了双方同时等待对方跳变的僵局。此外,四相位握手通常配合超时和重试机制,能及时检测异常并恢复通信,从根本上防止死锁的发生。

优点:

- 模块化特性突出:异步电路的控制完全在本地进行,可以比较好的集成;只需满足模块间的异步通信协议,无需受到模块内部时钟的严格时序要求。

- 对信号延迟不敏感:使用握手信号通信,信号延迟只会影响工作速度,不会影响电路行为。

- 没有时钟偏移问题:使用本地时序信号取代整体时钟,避免了时钟设计问题。

- 潜在的高性能特性:在同步设计中,由于大家都在相同时钟下工作,最小的时钟周期必须保证电路在信号传输的最差情况(worst-case)下仍然能正确工作,所以整体性能被最差的点限制。而异步设计中,每一级完成操作的时间只和本级相关,整体性能是平均的结果,因此可能在整体上超过同步电路。可以说异步设计如果发挥“出色”,在性能上是可以超过同步设计的。

- 好的电磁兼容性:同步电路的时钟信号,在其时钟频率及其谐波处(或非常接近)的频带内产生大量EMI; 异步电路会产生EMI,但其模式在整个频谱上是均匀分布的

- 低功耗特性:在说异步电路的功耗低的时候,我们必须相当谨慎。首先,异步电路需要额外的控制信号,当使用某些编码时,异步电路可能需要更多面积,而更多的面积意味着更大的静态功耗。我们知道,CMOS工艺尺寸越小,静态功耗在整体功耗里所占比例越大。因此,异步电路虽然只在必要时工作,但整体在能耗上的表现还是需要认真分析才能有准确结果。第二,目前同步设计也会采用各种低功耗设计手段,比如门控时钟技术等等,对比的时候应该考虑这个因素。

缺点:

- 对噪声敏感:任何不需要的信号翻转都可能导致电路失效,因此要消除竞争冒险以及毛刺

- 增加了控制和用于DFT的电路,异步电路的面积开销可能高达同步设计的的两倍。

- 缺乏专用于异步设计的商用EDA工具

- 与异步设计相比,同步设计更易于测试和调试