【PZ-ZU47DR-KFB】璞致FPGA ZYNQ UltraScalePlus RFSOC QSPI Flash 固化常见问题说明

1 Flash 固化

Flash 固化需要先生成 BOOT.bin 文件,这边以裸机的串口工程进行讲解如何生成 BOOT.bin 文件及 Flash 固化操作。

有读者会遇到,只使用 PL 端的情况,也需要进行 Flash 固化。我们需要添加 PS 端最小配置(包含 Flash 配置),因为 Flash 挂在 PS 端,必须需要 PS 端参与。

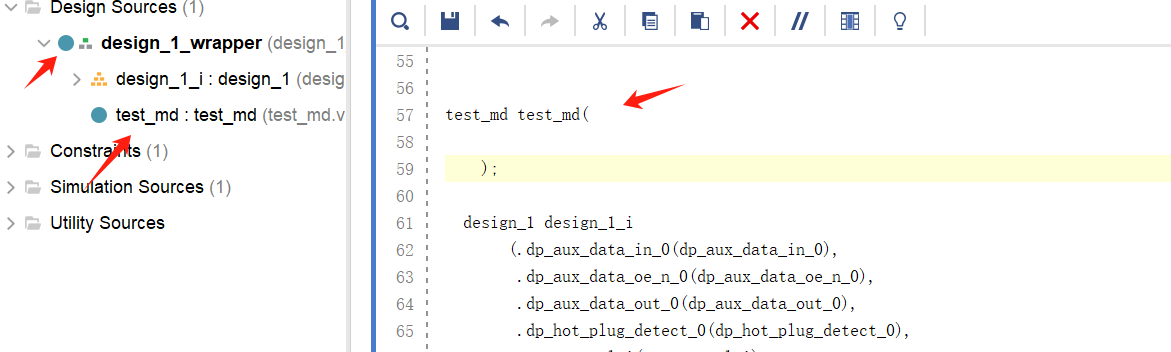

我们可以把 PL 的工程,作为子模块,加入到工程编译导出 XSA 即可,后续Vitis-SDK 操作是一样的,如下图(只是演示,未添加端口,读者根据自己的实际情况修改):

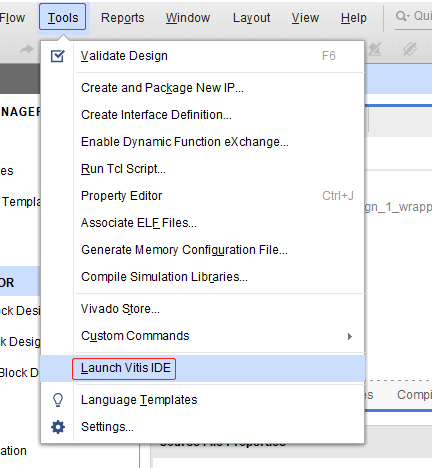

点击 Launch Vitis IDE

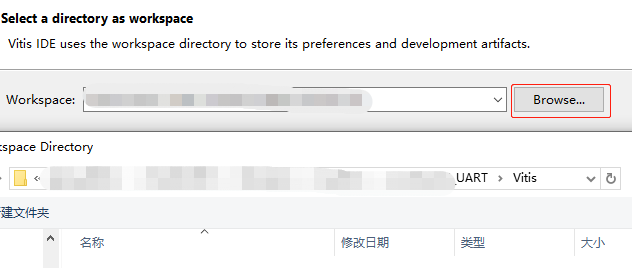

选择软件工程所在的文件夹,然后点击 Launch

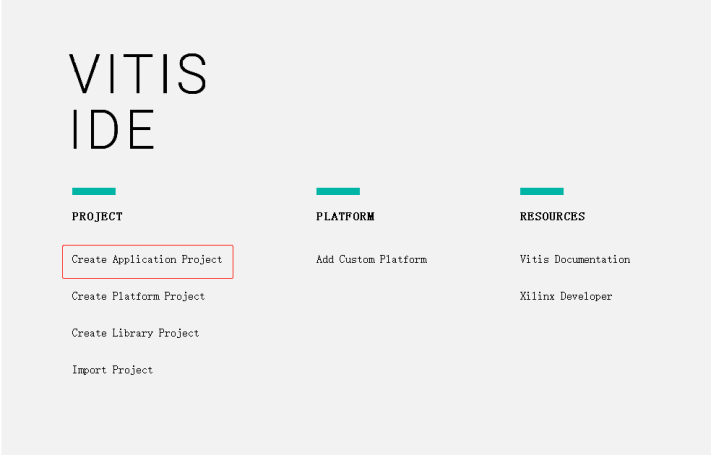

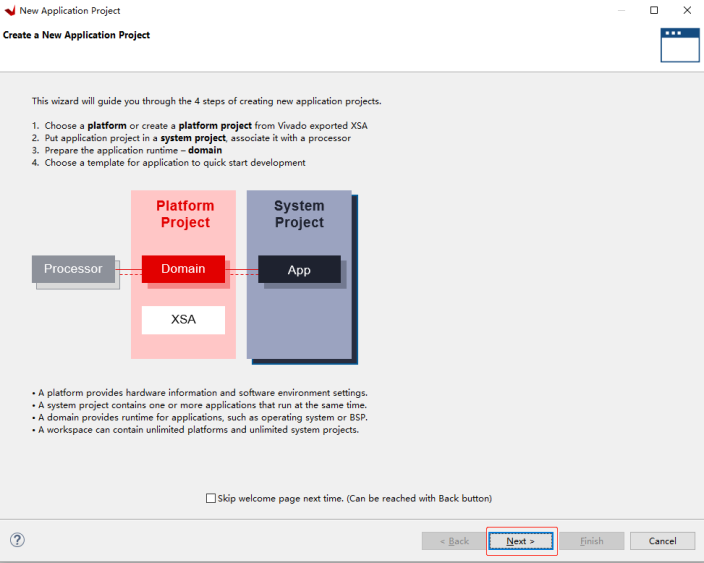

点击 Create Application Poject,创建应用工程

点击 Next

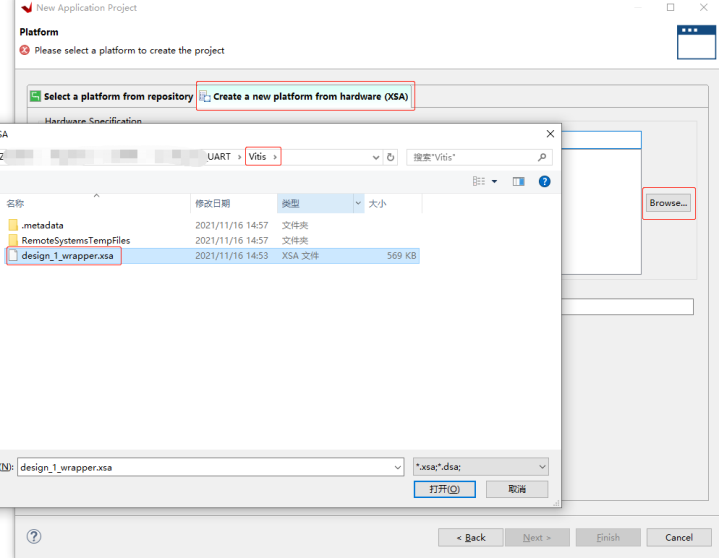

选择.XSA,然后点击 Next

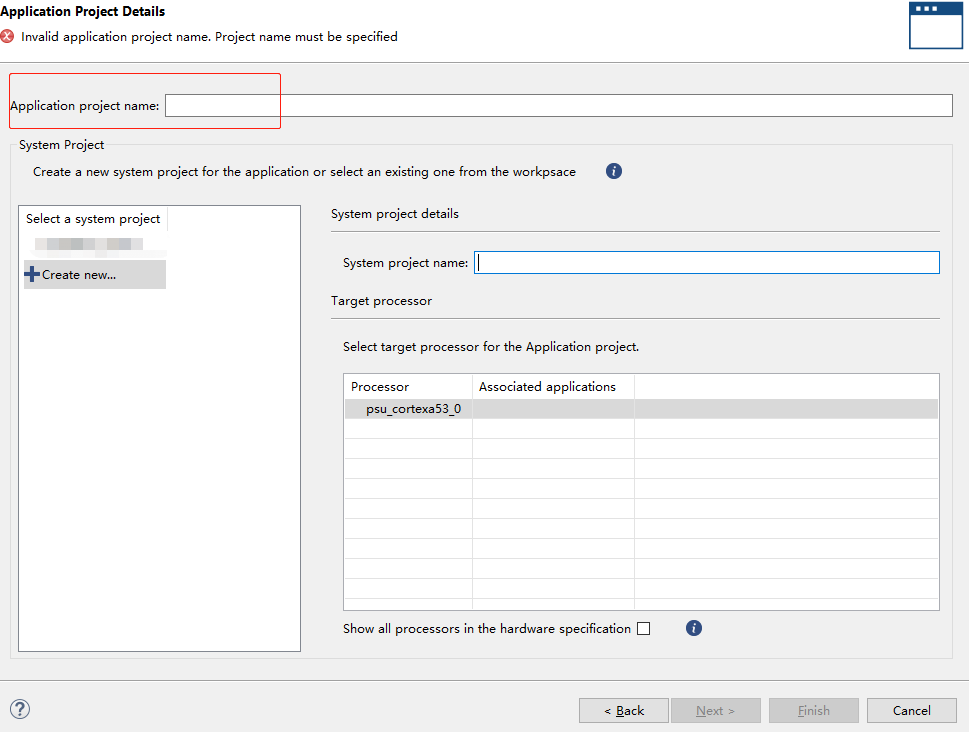

输入软件工程名字,然后点击 Next

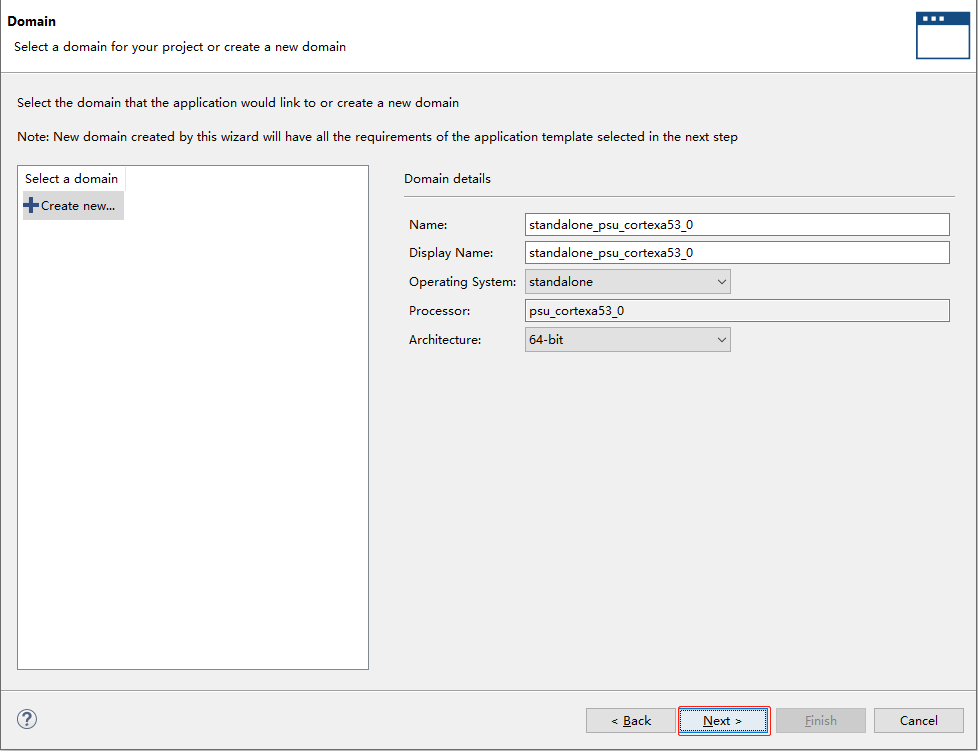

点击 Next

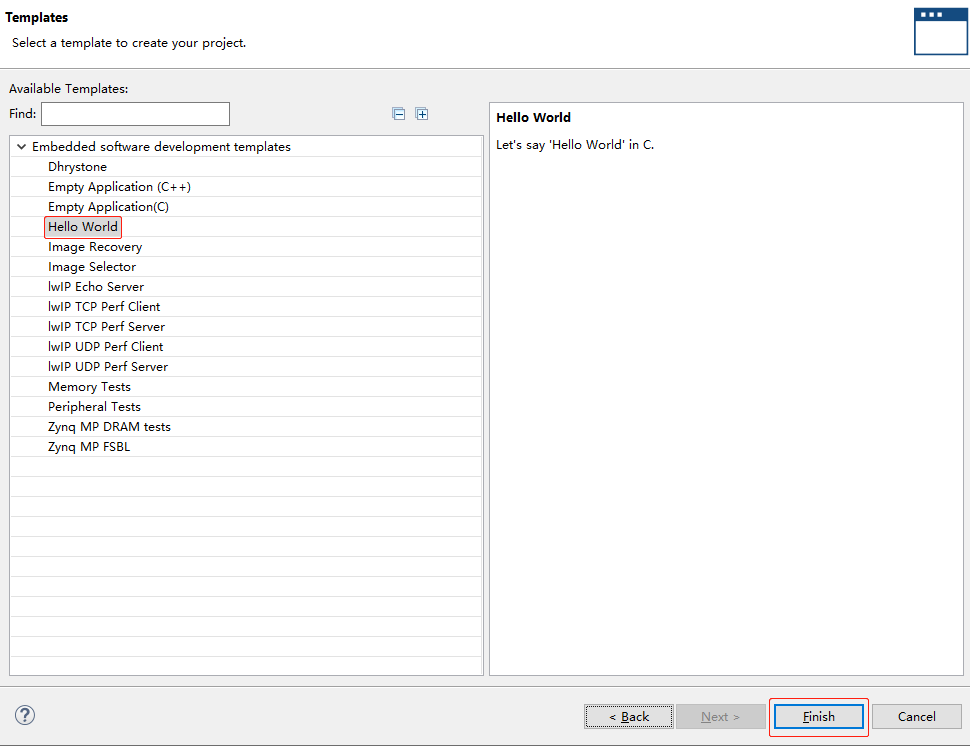

选择 Hello World 工程,点击 Finish

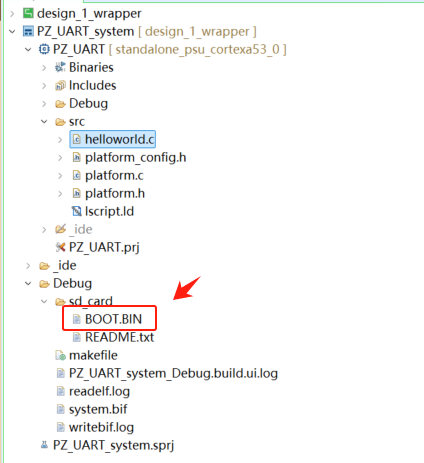

键盘输入 Ctrl+B,对整个工程进行 Build,然后在工程目录下,可以看到新生成的 BOOT.bin

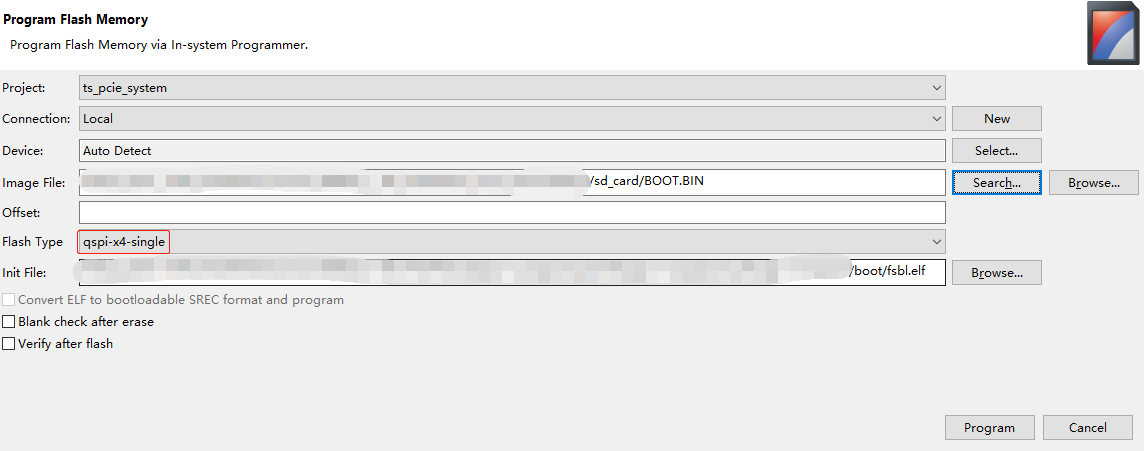

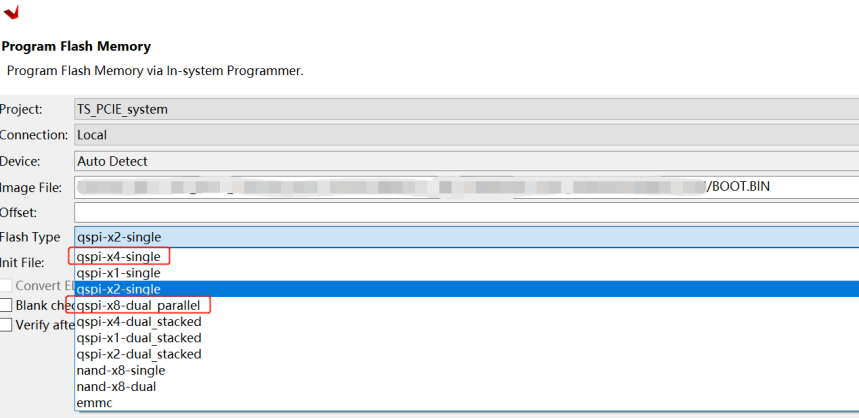

在 Xilinx 栏目下选择 Program Flash,然后选择 BOOT.bin 和 fsbl.elf 文件,选择完成之后,点击 Program,这样就完成了 Flash 固化

说明:1. Flash 固化的时候,需要把启动模式切到 JTAG 模式,固化完成之后,再切到 Flash 模式。启动模式切换参考核心板上的启动模式表格,拨码开关 ON 端对应 ON,另一端对应 OFF。

2. BOOT.bin 也可以拷贝到 SD 卡,然后把启动模式切到 SD 卡模式,也可以 SD 卡启动

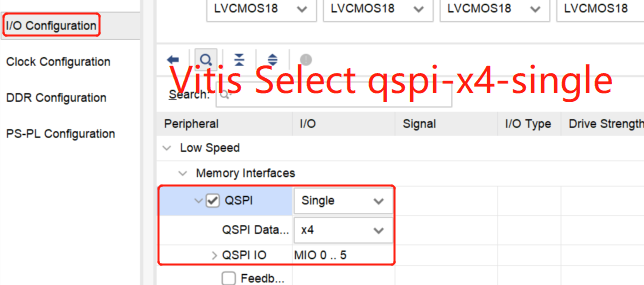

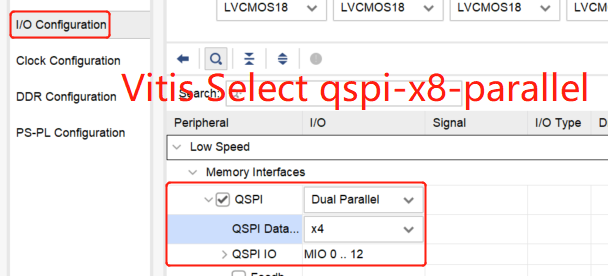

3. 我们的硬件支持 qspi-x4-single 和 qspi-x8-parallel,选择的时候,根据 Vivado 的配置和硬件决定(注意:需要看下硬件是否有两片 Flash, qspi-x8-parallel 需要两片 Flash,部分硬件不支持)

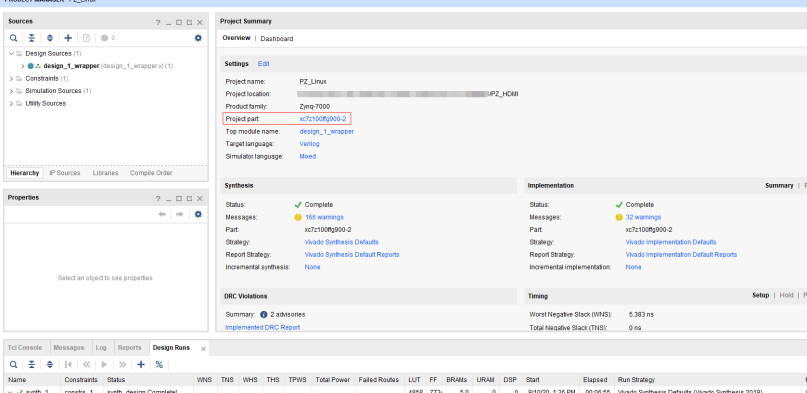

2 工程芯片型号更改

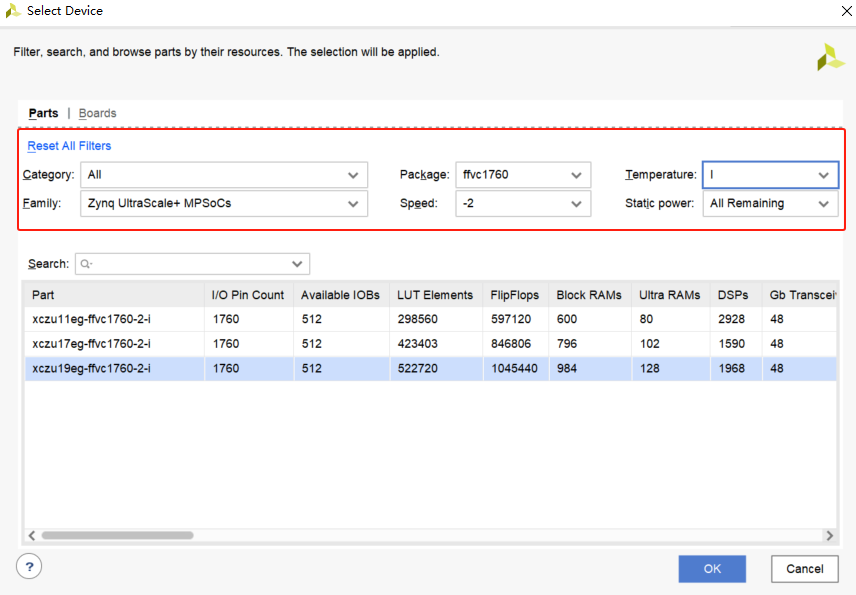

先打开 Vivado 工程,然后点击芯片型号

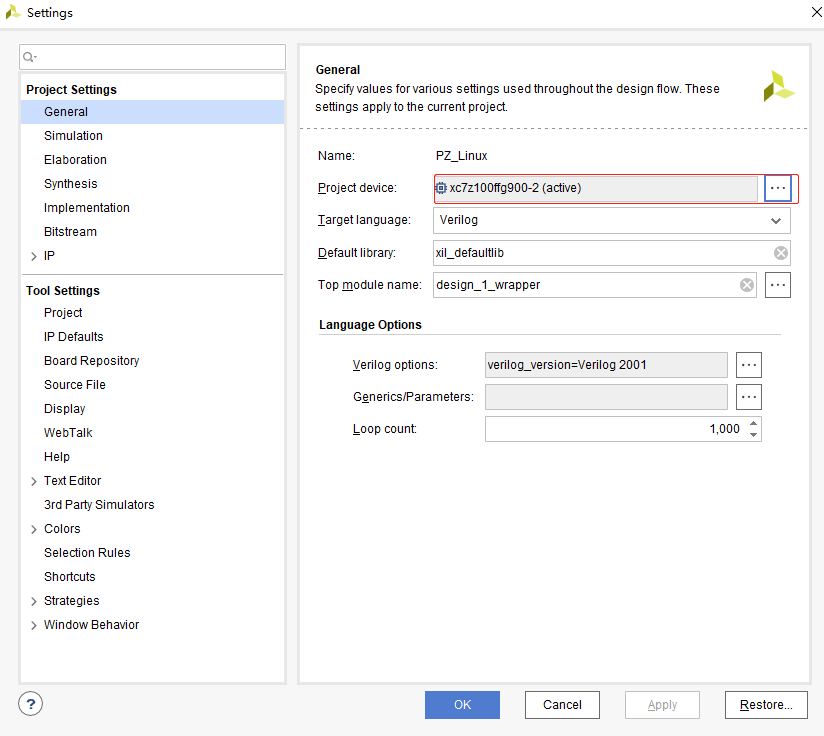

点击...

读者根据筛选条件选择需要的特定型号,然后点击 OK

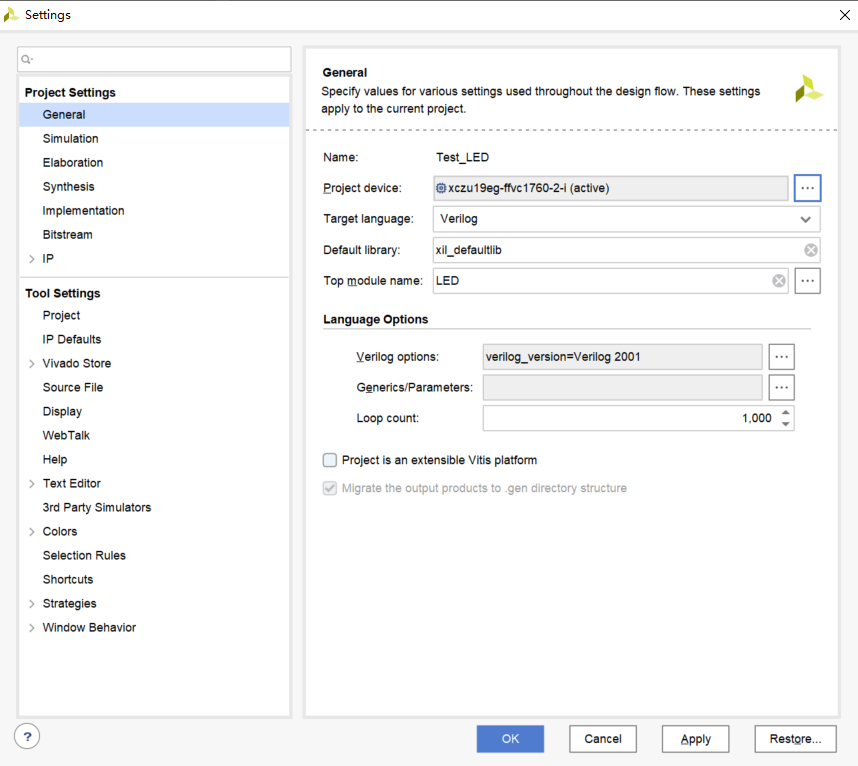

选择完成之后,点击 OK

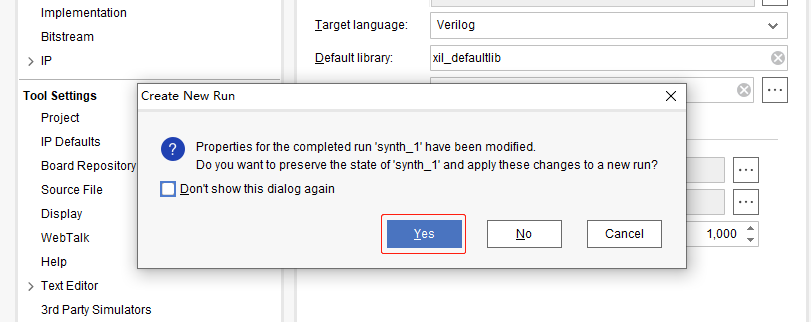

继续点击 Yes、OK

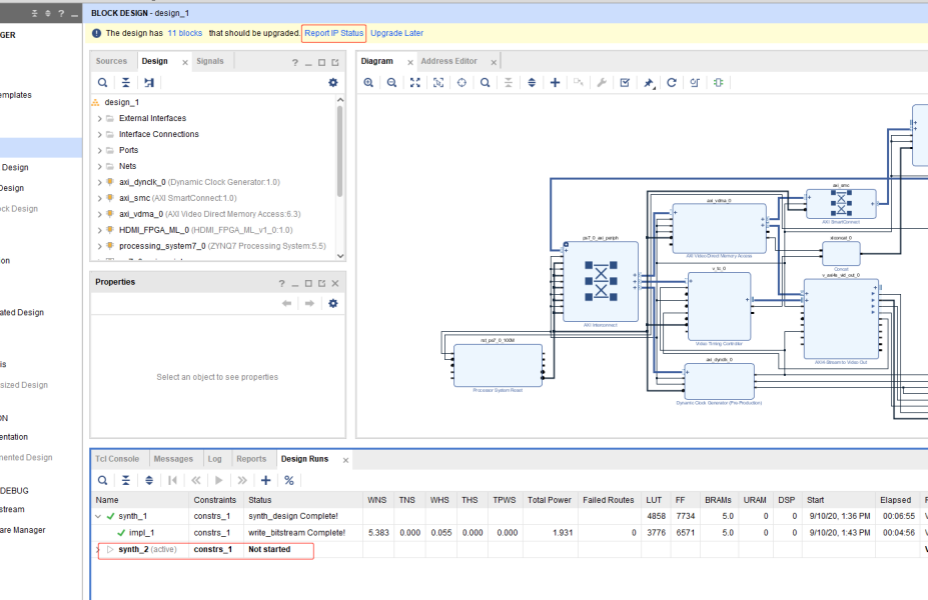

synth_2 就是更改芯片之后状态, synth_1 是之前芯片的(可以删除掉synth_1),点击 Report IP Status,更新 IP

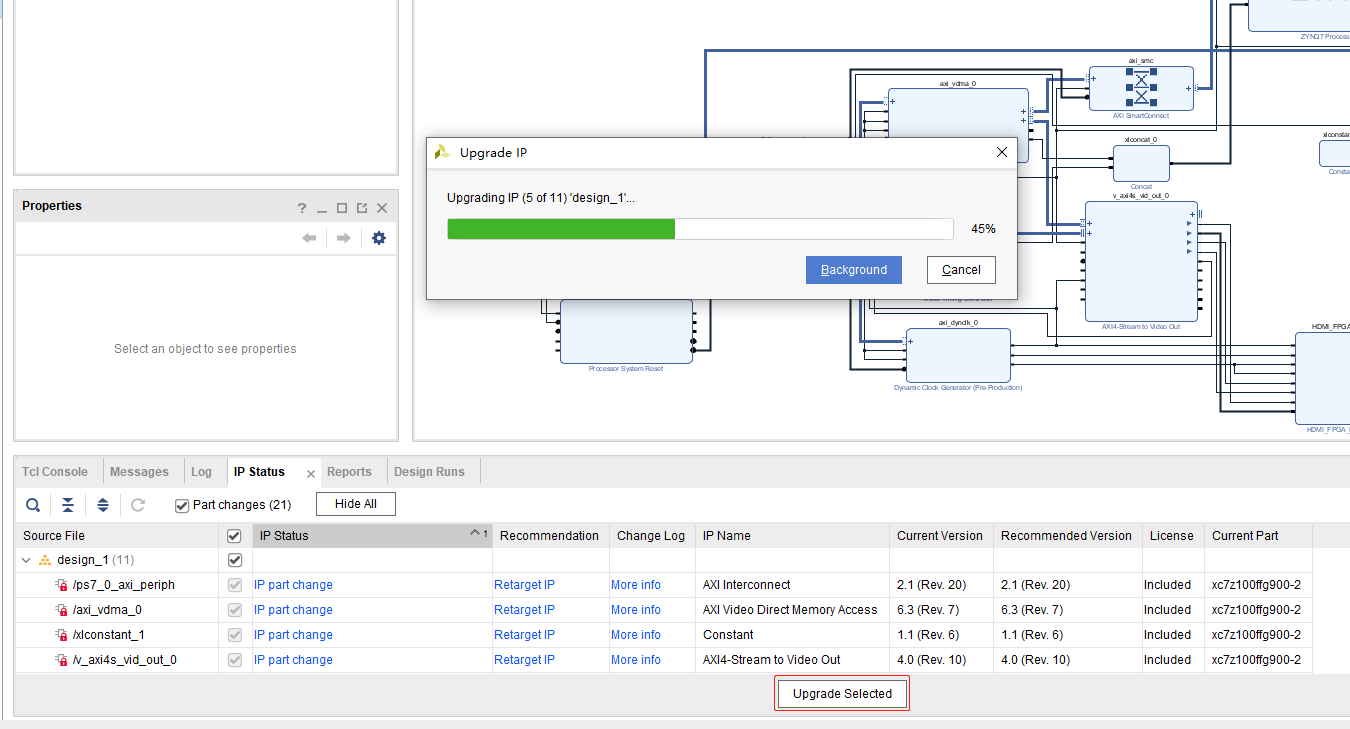

点击 Upgrade Selected,然后点击 OK,需注意,有部分 IP 更改后,可能会

有变化或者不支持,因为主芯片有差异,读者还需要根据实际情况进行修改。一般硬件管脚兼容的芯片,只需要 Upgrade 就可以了。

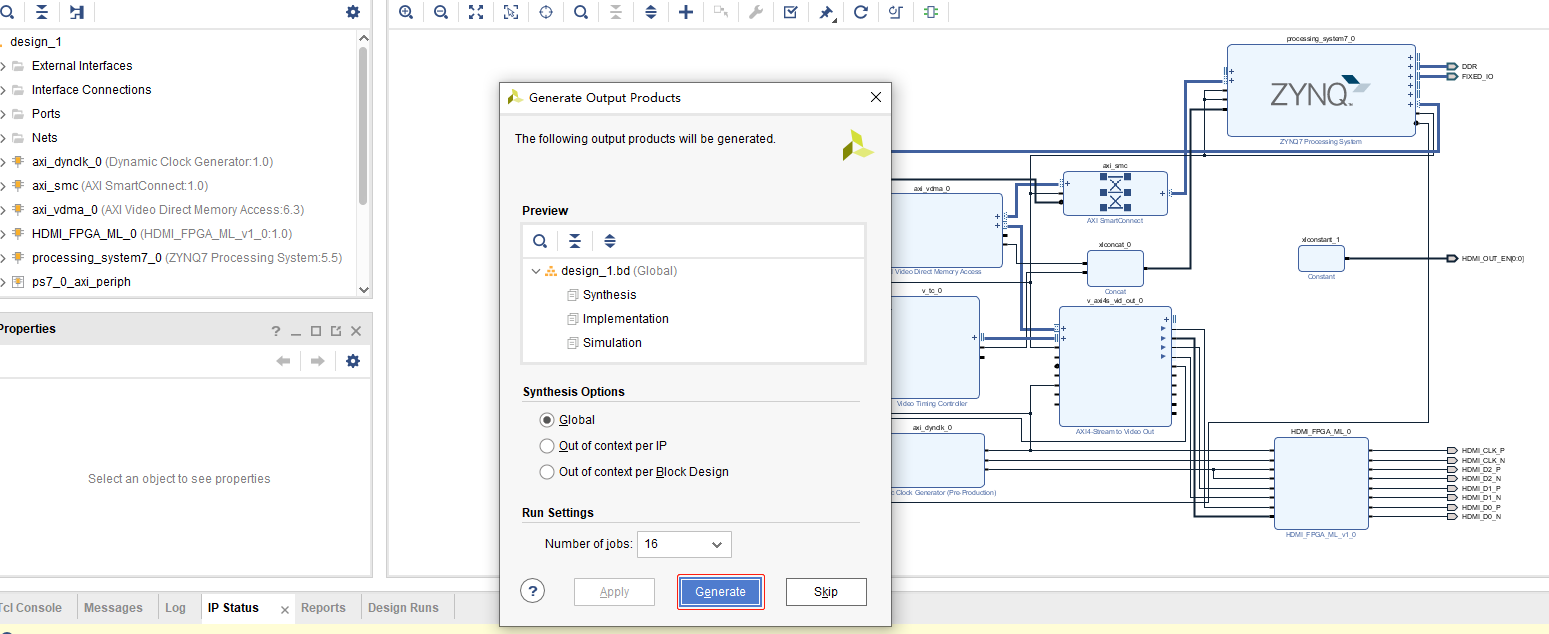

然后 Generate 一下

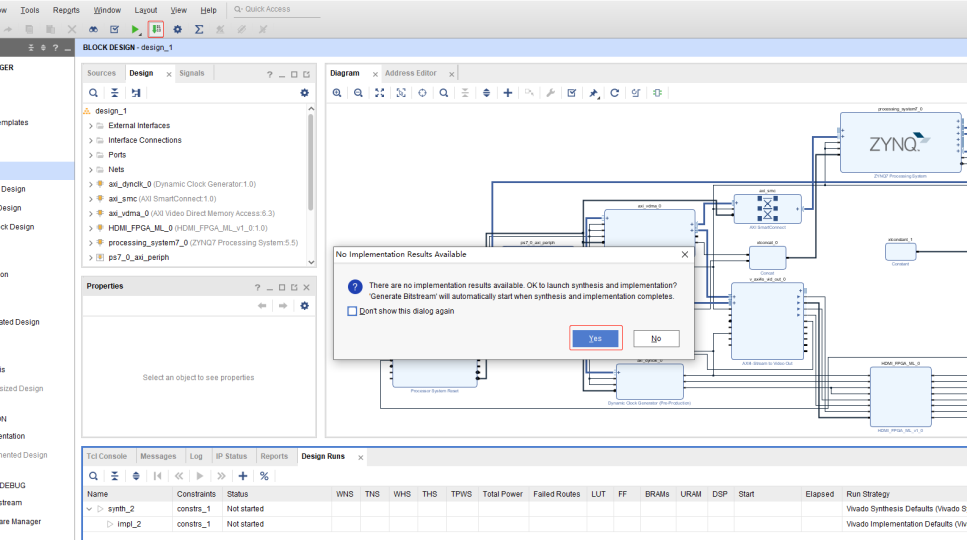

然后重新生成 bit 文件,到此型号更改完成

3 Vitis-SDK 路径更改问题

Vitis-SDK 裸机工程拷贝之后,路径会发生改变,build 会提示错误,如下图(同时也需要注意,Vitis 工程放的路径不要太长,不然会报错):

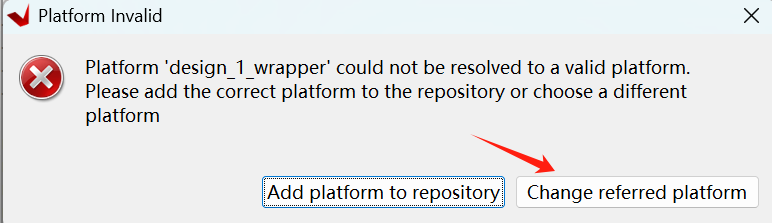

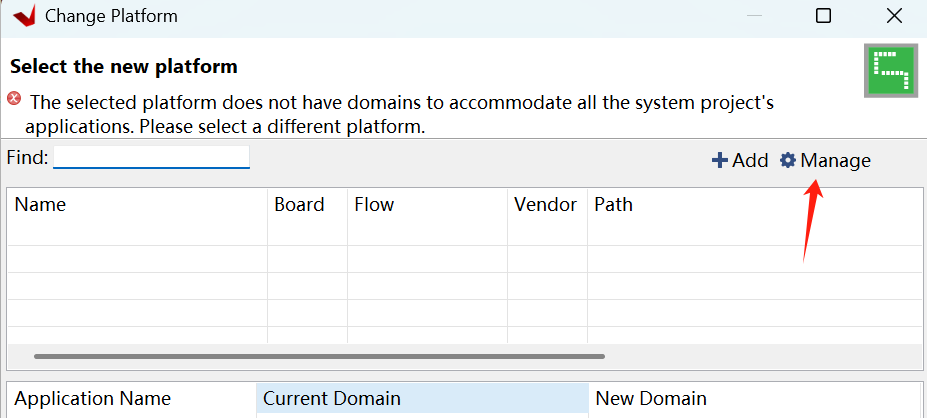

这是由于路径改变,导致 Vitis-SDK 找不到 platform 的路径,我们点击Change referred platform 进行路径修改,如下图:

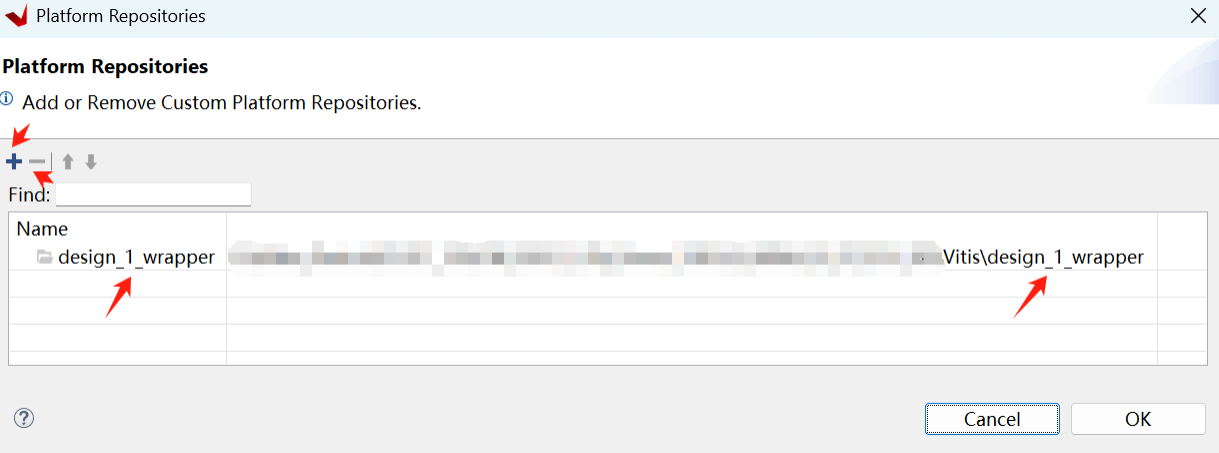

先删除旧的路径,然后添加新的实际路径(读者根据自己的实际路径进行添加),如下图:

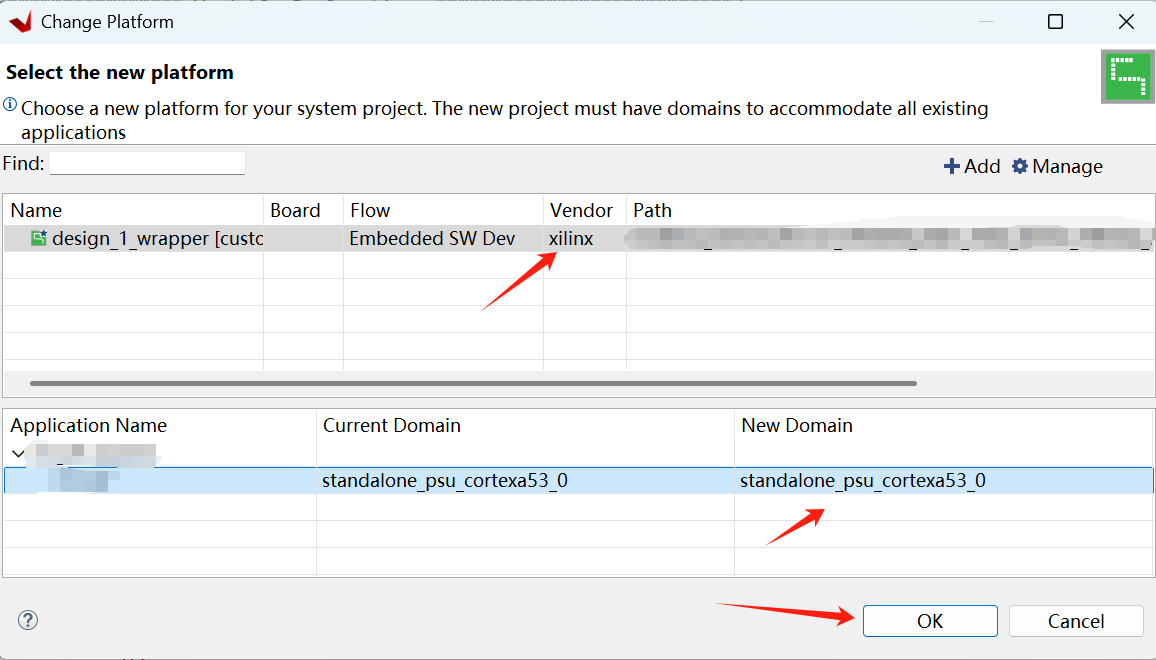

先添加完成后,点击下裸机应用,刷新出 standalone_psu_cortexa53_0 即可,如下图:

完成后,Vitis-SDK 工程就可以进行build all 操作了,然后可以进行调试等操作,路径修改到此就完成了。