xilinx 7系列底层可配置逻辑块CLB资源简介

xilinx 7系列底层可配置逻辑块CLB资源简介

目录

前言

一、CLB概述

二、LUT

三、FF

总结

前言

在Xilinx FPGA 架构中,CLB(Configurable Logic Block,可配置逻辑块)作为最基本的逻辑单元,是实现复杂逻辑功能的核心。CLB 的主要组成包括查找表(LUT)和触发器(Flip-Flop, 简称 FF),它们协同工作,实现组合逻辑与时序逻辑的有效结合。理解 LUT 和 FF 的工作原理及其在 CLB 中的组织方式,对于优化逻辑资源使用、提高设计性能具有重要意义。本文将深入介绍 Xilinx CLB 中 LUT 与 FF 的结构特点、作用机制以及它们在实际设计中的应用策略。

提示:以下是本篇文章正文内容

一、CLB概述

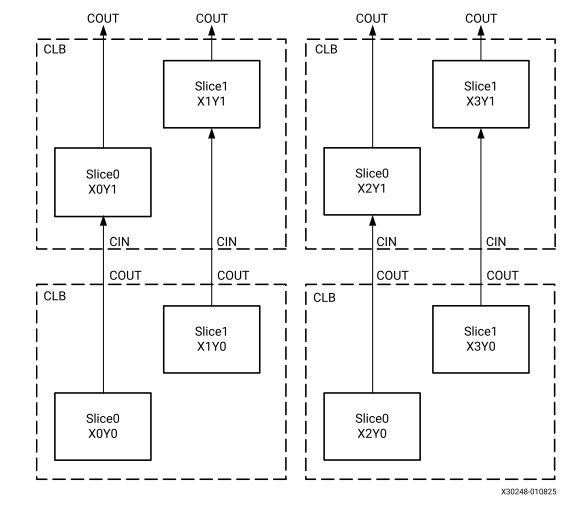

CLB的全称是configurable logic block,可配置逻辑块。xilinx 7系列的每个CLB里面包含一对SLICE,可以是两个SLICEL,也可以是一个SLICEL加一个SLICEM。

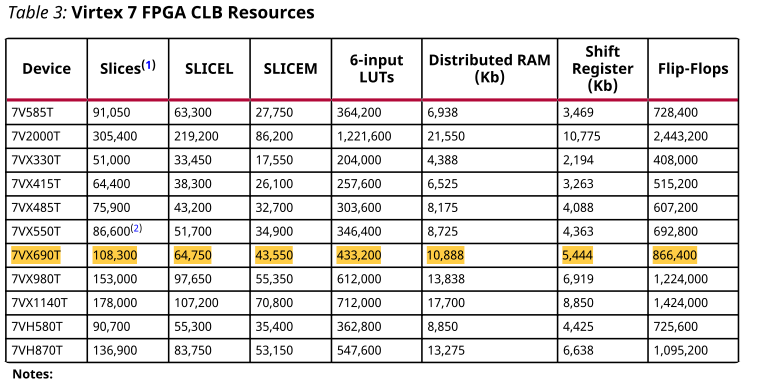

每个7系列FPGASLICE由4个6输入LUT和8个FF、MUX、进位链组成。大约三分之二的片是SLCEL逻辑片,其余的是SLICEM。SLICEM中可以使用它们的LUT作为分布式64位RAM或32位移位寄存器(SRL32)或两个SRL16,SLICEL的LUT则不支持。

下表中彩色字是V7 690t的资源。可见,SLICES=SLICEL+SLICM,LUT=SLICES*4,FF=SLICES*8。

通过这张表,还能看到资源最大的是2000t,LUT122万,触发器244万,确实丰富,价格估计也挺贵的。

xilinx官方也给了一些建议便于高效率地使用这些资源。下面是笔者觉得有用的信息:

触发器资源比较丰富,在设计时利用流水线设计以提高性能;

在专用资源(块RAM、DSP)的输出端使用专用触发器;(专用触发器IP核配置界面可选择)

避免使用路由全局复位信号,并尽量减少使用本地复位,以最大限度地利用FPGA资源;

仅在必要时使用控制信号;

避免在同一个触发器上同时置位和复位。

避免在小型移位寄存器和存储阵列上使用控制信号,使用LUT而不是触发器,以最大限度地提高利用率并最大限度地降低功耗。

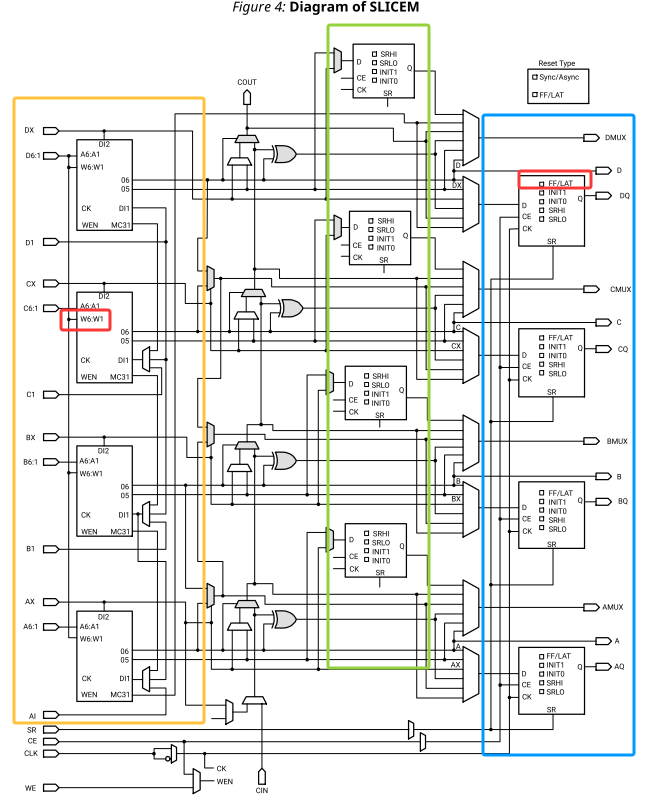

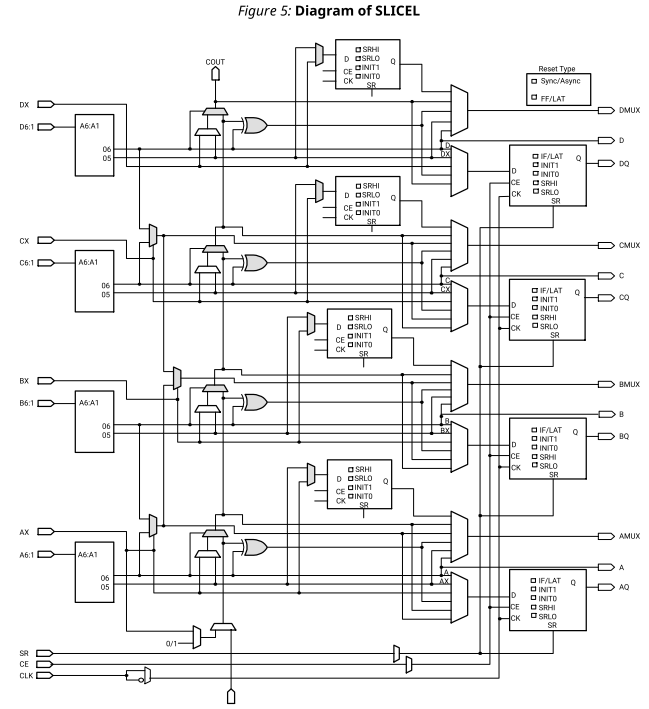

下面分别是SLICEM和SLICEL的框图。

二、LUT

对于片内的四个LUT(A、B、C和D),每个函数发生器都有六个独立的输入(A1至A6)和两个独立的输出(O5和O6)。每个LUT可以配置成一个六输入布尔函数,也可以配置两个任意定义的五输入布尔函数,只要这两个函数共享公共输入。

除了基本的LUT之外,切片还包含三个多路复用器(F7AMUX、F7BMUX和F8MUX)。这些多路复用器用于联合收割机,最多可组合四个函数发生器,以在一个片内提供七个或八个输入的任何函数。

具有八个以上输入的函数可以使用多个切片来实现。切片之间没有直接连接,以形成CLB内大于8个输入的函数发生器。

从上面的图片可以看出SLICEM有地址线W6-W1,而SLICEL没有,这就是为什么SLICEM中可以使用它们的LUT作为分布式64位RAM或32位移位寄存器(SRL32)或两个SRL16,而SLICEL的LUT则不支持的原因。

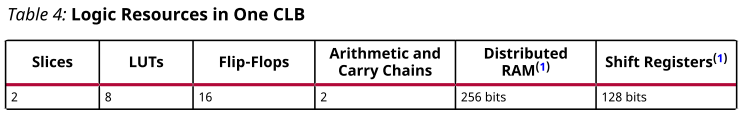

下图是一个CLB里面的资源。

1个LUT可以作为分布式64位RAM或32位移位寄存器,那么4个LUT可以作为分布式256位RAM或128位移位寄存器。

三、FF

每个SLICE片有8个FF。其中4个可配置为边沿触发D型触发器或电平敏感锁存器,如前面SLICEM框图中蓝色框起来的4个所示。另外4个FF只能配置为边沿触发的D型触发器,如前面SLICEM框图中绿色框起来的4个所示。这里需要注意的是,当蓝色框起来的4个FF被配置为锁存器时,另外四个FF就不能被使用了。

控制信号时钟(CLK)、时钟使能(CE)和置位/复位(SR)对于1个SLICE片中的所有存储元件是公共的。所以只有这些控制信号相同的FF才有可能被放置在同一个SLICE中。CE和SR信号都是高电平有效。

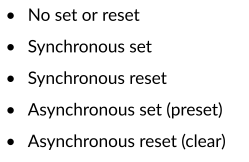

寄存器或能够用作锁存器的四个存储元件的置位和复位功能的配置选项为:

需要更多关于分布式RAM用法或进位链说明的可以自行参考xilinx官方的ug474手册。

总结

本文介绍了 Xilinx CLB 中 LUT 与 FF 的结构特点,有利于我们代码的设计,提高资源利用率。