Spyglass:跨时钟域同步(同步使能)

相关阅读

Spyglass![]() https://blog.csdn.net/weixin_45791458/category_12828934.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12828934.html?spm=1001.2014.3001.5482

简介

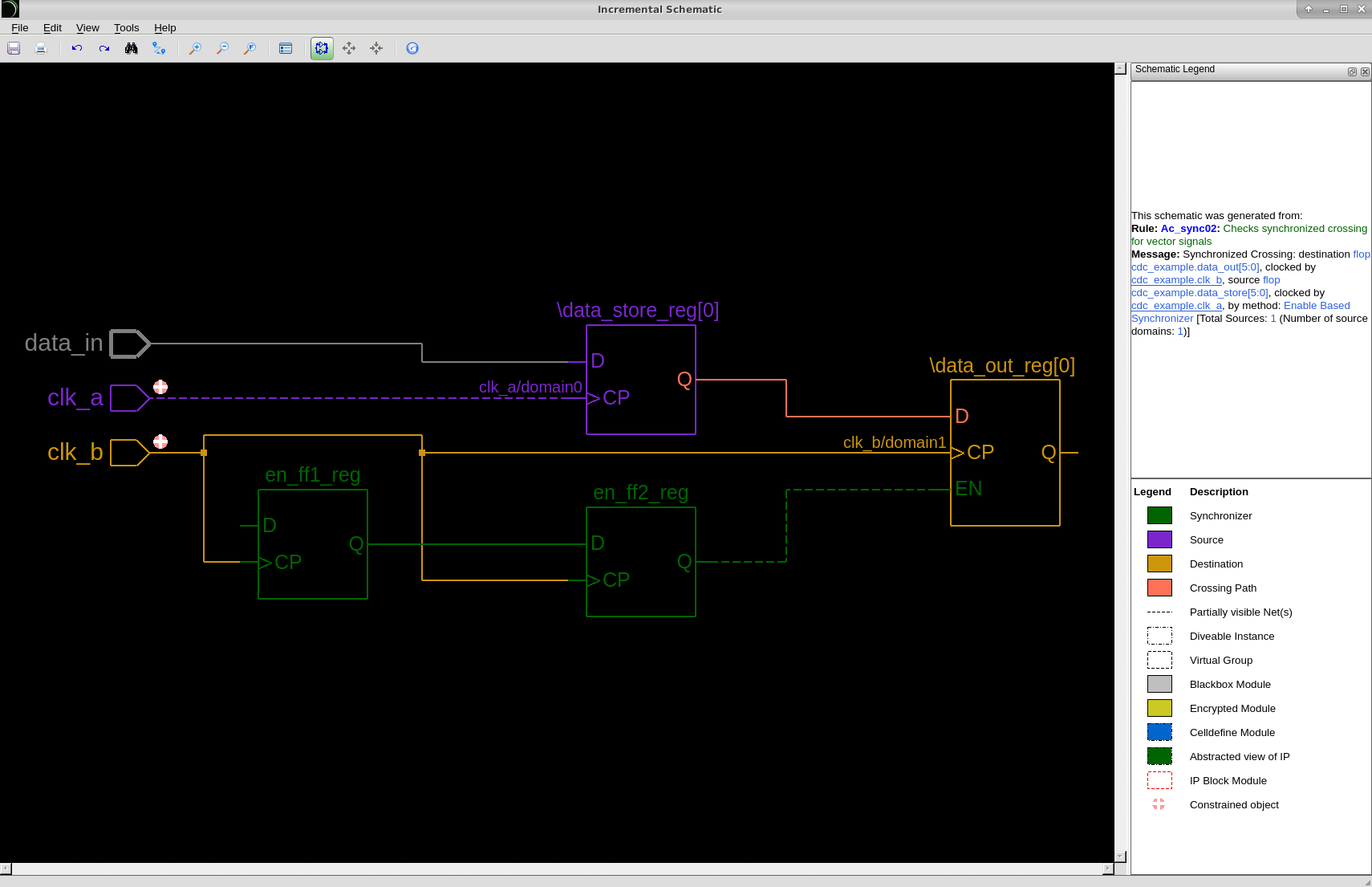

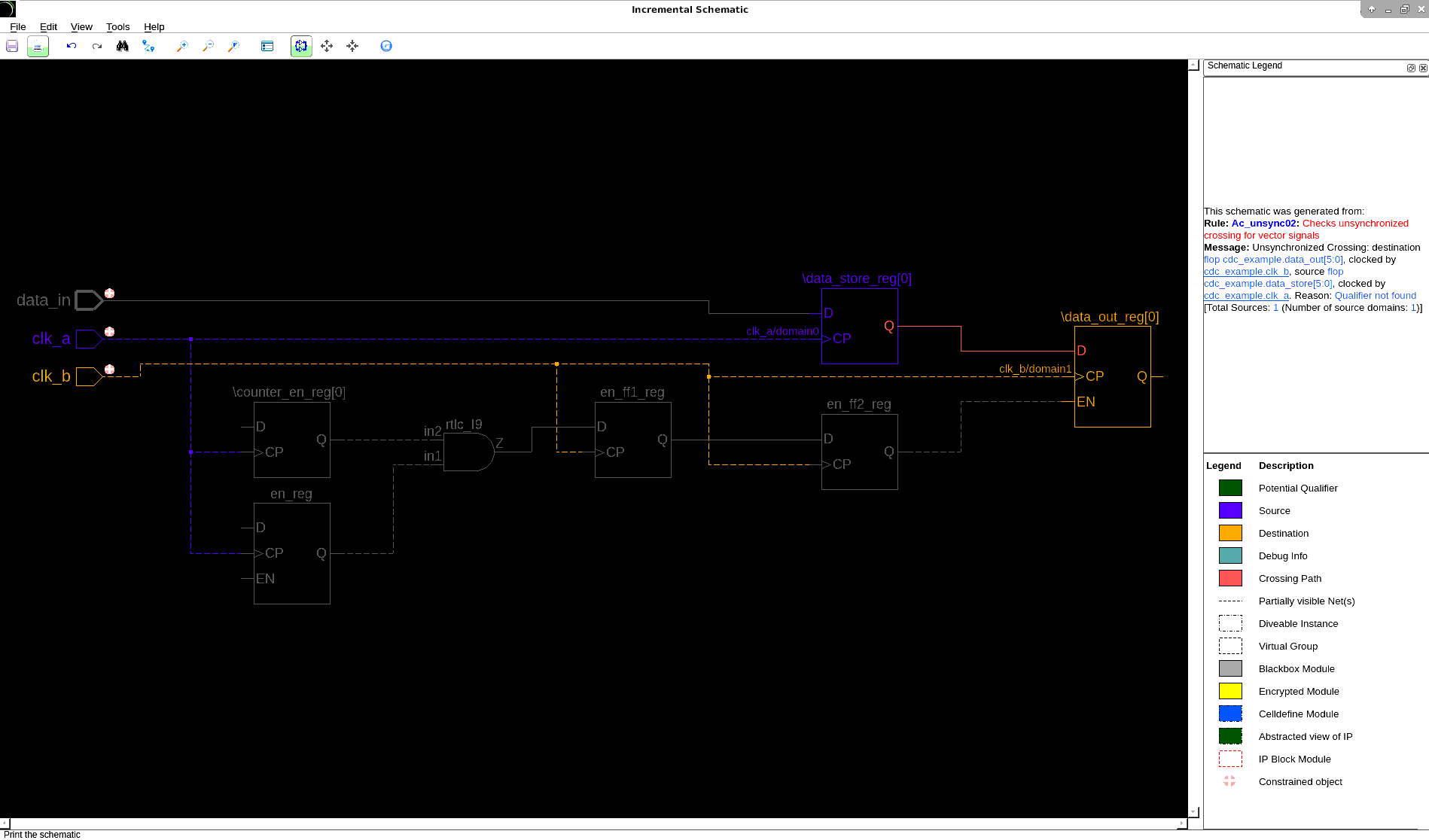

同步使能方案主要用于数据信号跨时钟域同步,该方案将一个控制信号同步至目标时钟域并用其作为数据信号的捕获触发器的使能信号,如图1所示。

图1 同步使能方案

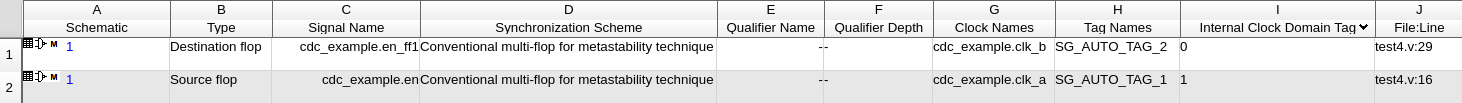

图2是Ac_sync01规则提供的Spreadsheet,其中展示了控制信号跨时钟域相关细节,如果该信号同步失败,数据信号的同步也会失败。

图2 Ac_sync01规则提供的Spreadsheet

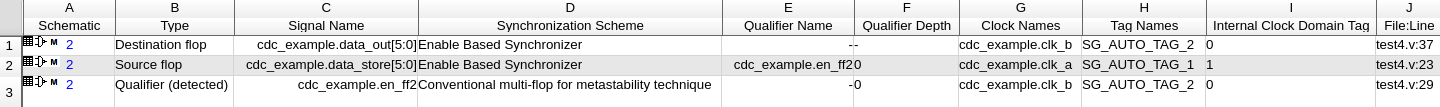

图3是Ac_sync02规则提供的Spreadsheet,其中展示了数据信号跨时钟域相关细节,主要到控制信号ee_ff2被识别为了Qualifier。

图3 Ac_sync02规则提供的Spreadsheet

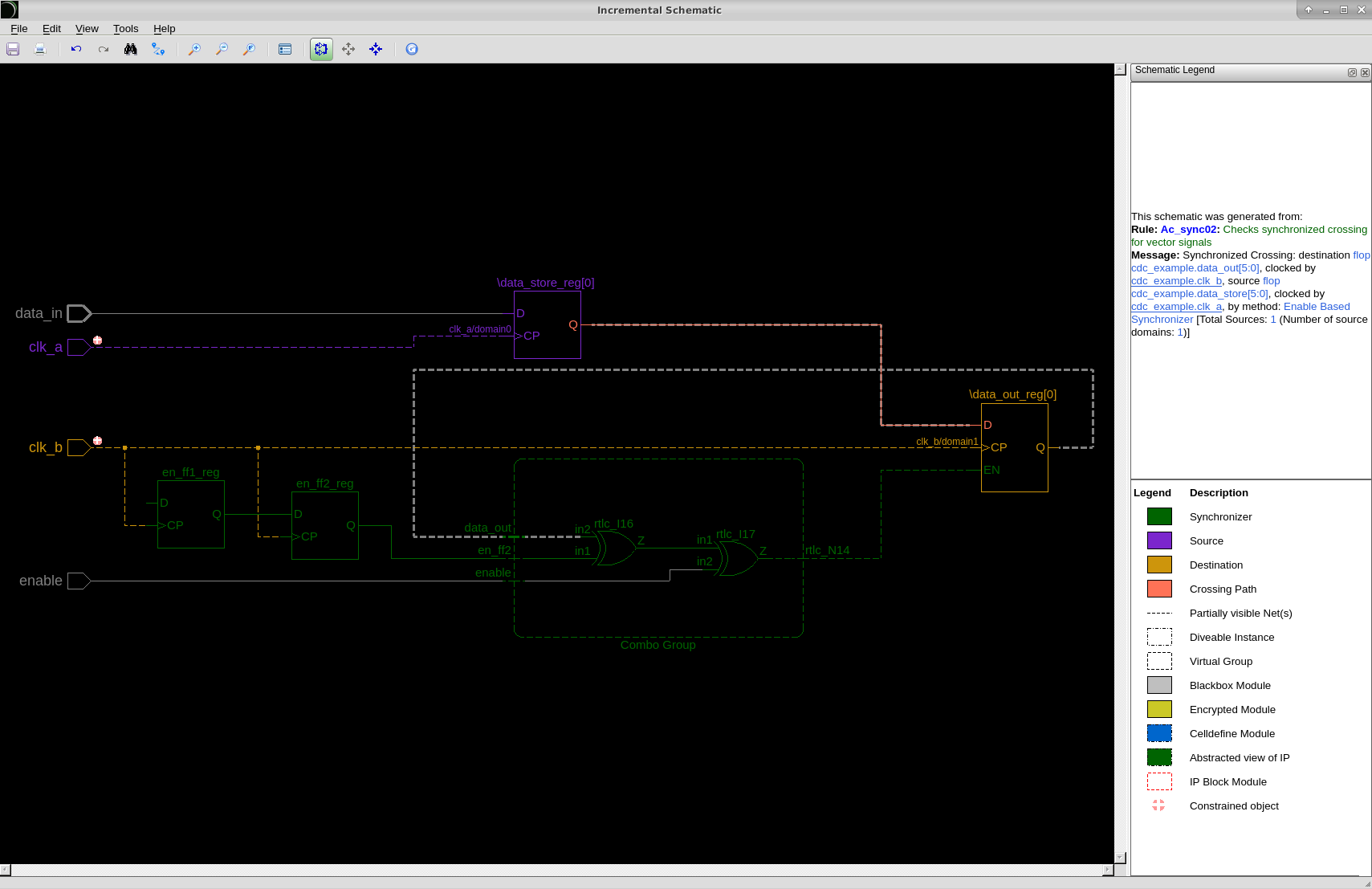

除了图1所示的情况,Spyglass允许捕获触发器的使能信号的扇入中存在目标时钟域的触发器或输入端口(但一定需要一个由源时钟域同步来的控制信号),如图4所示。

图4 同步使能方案

相关参数或约束

enable_sync_cell参数

allow_combo_logic参数

默认情况下,Spyglass允许通过组合逻辑跨时钟域,将allow_combo_logic参数设置为no可以禁止这种情况,下面给出了一个例子。

// test.prj

set_parameter allow_combo_logic no图5展示了这种情况下通过组合逻辑跨时钟域时出现Ac_unsync01错误(实际上,即使allow_combo_logic参数设置yes,也只是不出现Ac_unsync01错误,但Ac_glitch03错误会出现,即Spyglass识别到毛刺)。

图5 组合逻辑跨时钟域错误

最后顺带一提,该跨时钟域方案支持源对象为触发器或黑盒,目标对象必须为触发器。