ADC-工业信号采集卡-K004规格书

1.产品说明

1.1产品简介

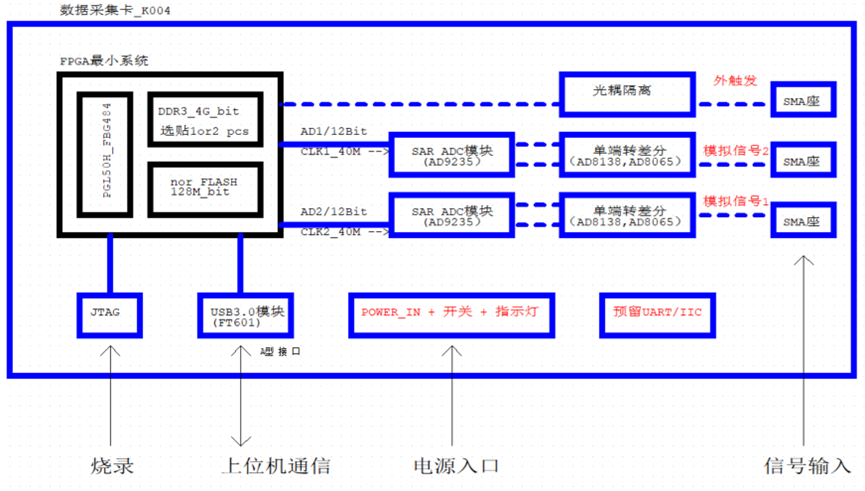

此工业采集卡,采用国产FPGA芯片,紫光的PGL50H_FBG484,搭配ADI的AD9235进行ADC采集,在通过USB3.0接口(FT601)和上位机通讯。

核心优势:

- 用户灵活选贴单通道/双通道ADC_12Bit采集方案。(独立通道,不干涉)

- 可代码配置定长触发采集或连续采集模式,搭配了大容量Flash和DDR3,DDR可根据需求选贴1~2片,存储方式多样,为客户提供更多选择。

- USB3.0通讯接口提供5.0Gbps传输速度,高效而稳定。

- 输入模拟量可经过FPGA软件算法滤波处理后传输给上位机。

- 适合工控类和医疗类采集。

- 板内FPGA供电采用大电流,高开关频率,低纹波,片内电感的高端电源芯片,有效降低空间辐射,单个DCDC输出电流最大能支持6A,满足并解决了FPGA瞬态电流大的通病。

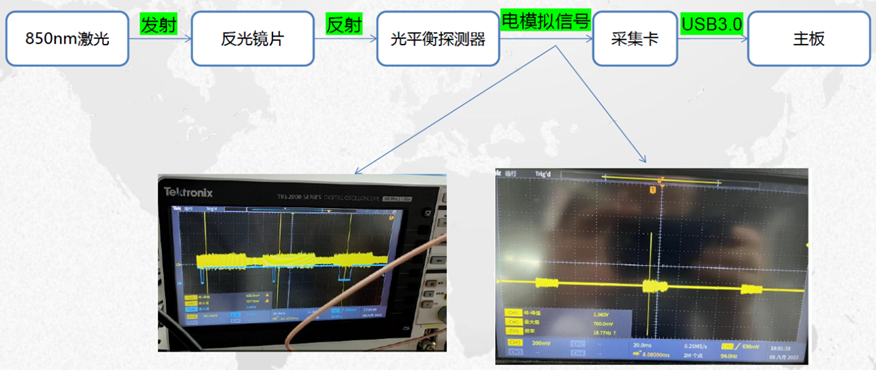

(图1)

1.1项目背景

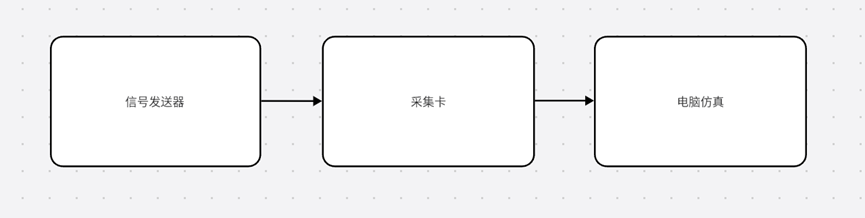

此采集板,设计是专门作采集模拟信号功能的子板。 主板即上位机,可以是其他微控制器或者电脑PC。

采集卡在整个流程中,相当于专人专员,承担了高精度高效的采集模拟量的工作。

(图2)

(图2)

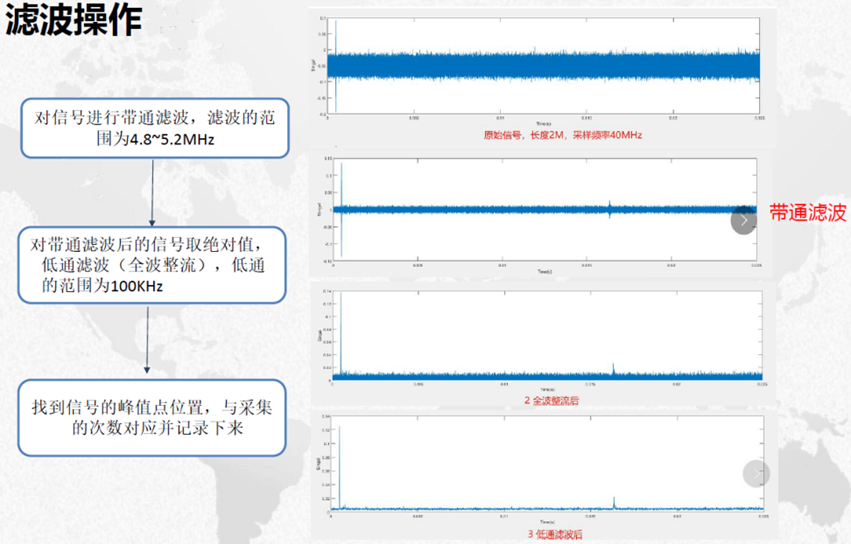

而采集卡的工作,不仅仅是将模拟数据量快速采集传输给上位机,还能将采集的数据进行算法的低通/带通滤波等处理。

(图3)

(图3)

1.2参数表

| FPGA | 308个用户IO,支持1.2V/1.5V/1.8V/2.5V/3.3V电平标准 支持MIPI-D-PHY,支持LVDS 内含10bit_1Msps_ADC,内含温度传感器 内含高速串行收发器HSST模块 支持DDR2,DDR3,LPDDR 支持JTAG配置,目前采集卡版本上电后配置完成时间需1.3S Tj=-40℃~100℃(工业级) |

| ADC | 采样率40Msps/20Msps/10Msps |

| 采样精度12bit/8bit | |

| 输入电压范围-5V~﹢5V | |

| 触发信号输入范围:0~5V,低脉冲触发 | |

| 支持连续采集或者定长采集,定长采集支持外触发或者软件触发,采集数据长度最高100MB/8bit或50MB/12bit | |

| USB | 支持USB3.0 TO FIFO Bridge ,传输速率5Gbps ,即400MB/s |

| 支持USB2.0,传输速率480Mbps | |

| 支持USB1.1,传输速率12Mbps | |

| 存储大小 | DDR3:4/8Gb,norflash:128Mb |

| 电源 | 5V2A |

| 功耗 | 整板静态功耗2.5~3W @5V |

| 整板工作温度 | -20℃~80℃ |

备注:

- 实际高低温测试,板子经过双85测试,产品稳定可靠。

- 板子主要温度来自于FPGA发热,建议结构针对FPGA做好热设计,尽量靠近整机排热扇或者接近进风口。

2.使用说明

2.1接口定义

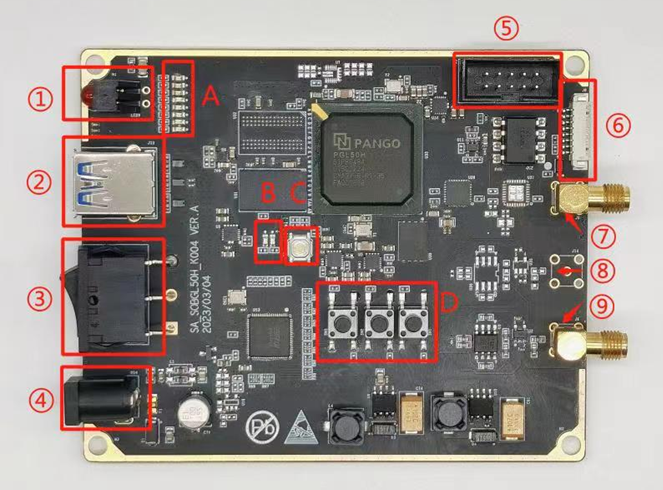

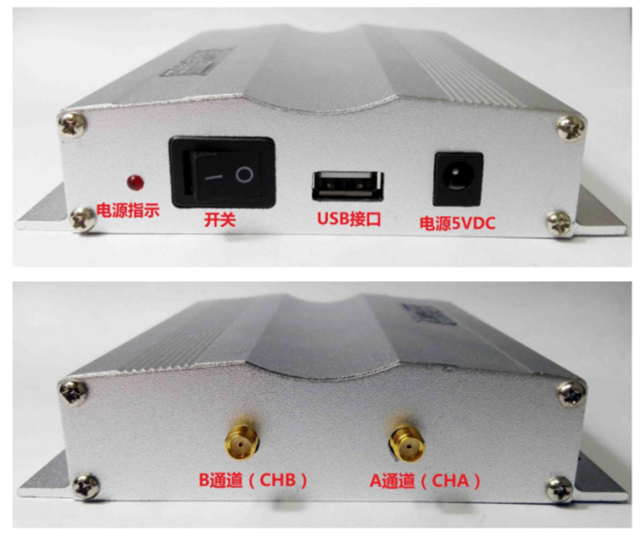

(图4)

(图4)

| 序号 | 说明 | 备注 |

| ① | 电源指示灯 | 是5V总输入电源的指示灯 |

| ② | USB3.0接口 | TYPE-A接口 |

| ③ | 电源开关 | 总输入电源开关 |

| ④ | 5V2A直流输入 | 圆头,内径2mm,外径6.3mm |

| ⑤ | JTAG接口 | FPGA的烧录调试口,支持热插拔 |

| ⑥ | 预留UART/IIC接口 | UART还是IIC由FPGA的IP core定义。

|

| ⑦ | CHA,外触发接口 | 光耦隔离,板内输入口3.3V上拉,低有效触发 |

| ⑧ | CHC,预留独立模拟输入2 | NC |

| ⑨ | CHB,独立模拟输入1 | 输入范围-5V~5V |

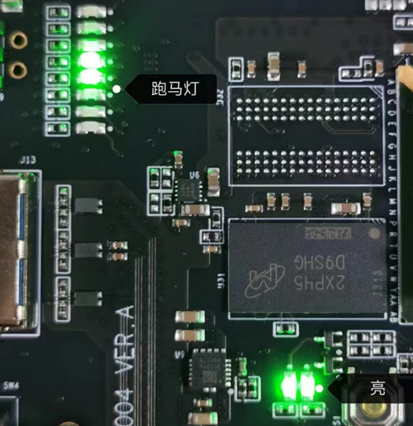

| A | FPGA程序跑马灯 | 用来观察FPGA程序运行情况 |

| B | FPGA配置状态灯 | FPGA的配置状态灯和内部CRAM清空指示灯 |

| C | FPGA复位按键 | 仅调试阶段用 |

| D | 预留按键 | 仅调试阶段用 |

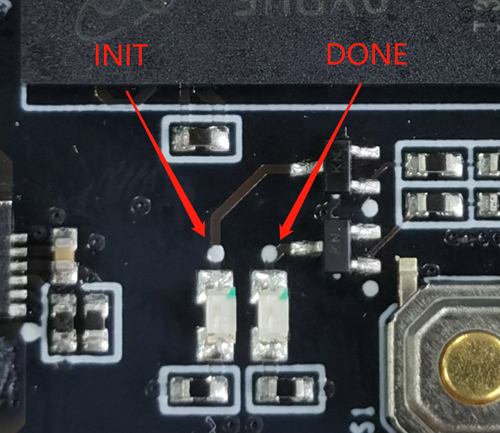

2.1.1 状态灯

状态灯有①,A和B三个部分。而①是电源指示灯,上电应该是常亮的。A是FPGA初始化配置相关的指示灯,有如下两个:

(图5)

当正常烧录好软件的板子上电时,INIT灯将保持常亮,而DONE灯将保持暗灭。然而,大约1.3秒后,DONE灯将亮起,表示FPGA内部的配置已完成。DONE信号的低电平状态代表FPGA正在进行配置过程中,而一旦DONE信号变为高电平,表示配置已成功完成。

在配置完成后,若FPGA出现配置错误,INIT灯将保持低电平状态。而当程序烧录完毕后,B部分的灯将开始循环展示跑马灯程序,这是一种直观的方式来验证板子上的程序是否正常运行。

(图6)

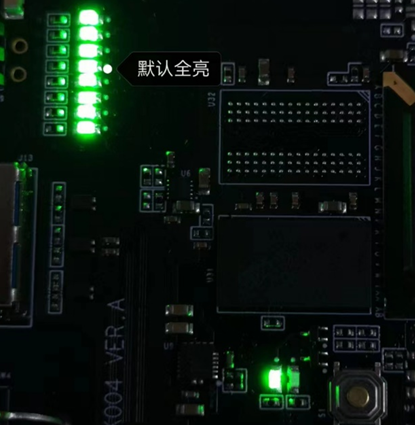

需要注意,板子没烧录程序时:跑马灯默认全亮,INIT灯常亮,DONE灯常灭。如下图7所示。正常烧录好的板子会在上电1~2秒后,指示灯会由图7转变为图8状态。

|

|

|

| 上电默认状态 | 上电1.3s后,配置完成,done灯亮,跑马灯运行 |

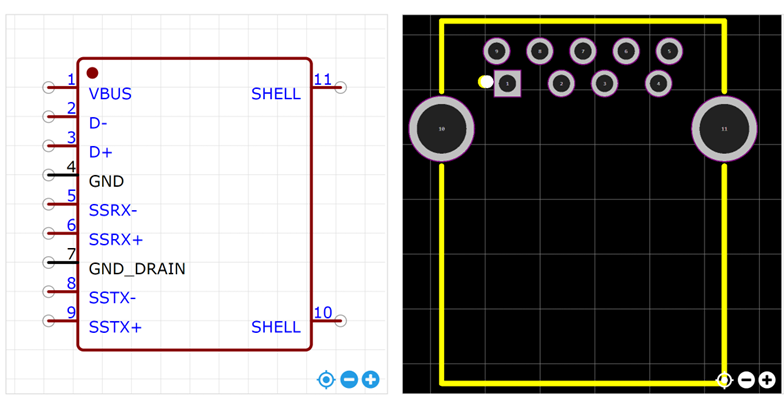

2.1.2 USB接口

USB接口的定义如下:TXN和TXP之间串联了100NF的电容,接口采用TYPE-A(9针插件),同时接口引脚并联了ESD防静电管,以提供更好的电气保护。

(图9)

(图9)

2.1.3 JTAG接口

JTAG接口是一种烧录调试口,使用者可以使用我们公司推荐的烧录器Pango USB Cable 来连接。

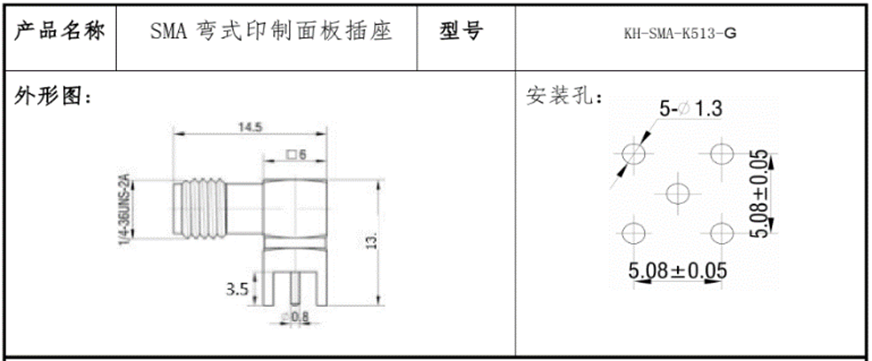

模拟输入和外触发接口机械图如下

(图12)

(图12)

使用者在使用时请选择公头(带针)射频线,单板SMA连接器规格为弯接母座。

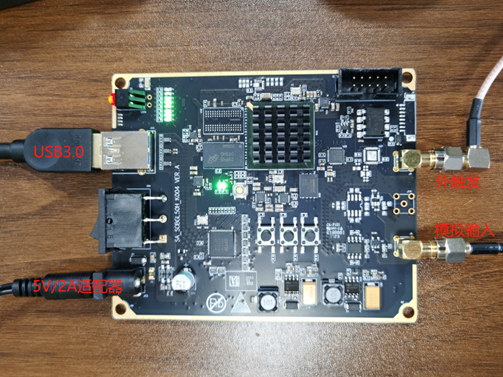

2.2物理连接

(图13)

| 输入 | CHA | 外触发接口,默认3.3V,低有效 |

| CHB | 模拟输入口1 | |

| CHC(器件NC预留) | 模拟输入口2(板子预留但没贴) | |

| 上位机通讯 | USB接口 | USB3.0接口 |

| 电源 | 5V2A适配器输入口 | 圆头,内径2mm,外径6.3mm |

| 其他 | 电源指示灯 | 5V输入电源_指示灯(红) |

| 电源开关 | 5V输入电源_船型开关 |

使用时,需要接5V2A适配器,连接USB3.0至上位机,模拟输入接CHB,触发信号接CHA即可,接法简单。

(图14)

需要注意电源不要误用12V的适配器,否则会有烧毁风险。同时注意模拟输入和外触发输入的电压范围。(板子的所有接口已做了防静电处理)

| 外触发输入电压范围 | 模拟输入电压范围 |

| 0~5V | -5V~+5V |

而外触发信号的设置,可以参照如下图:

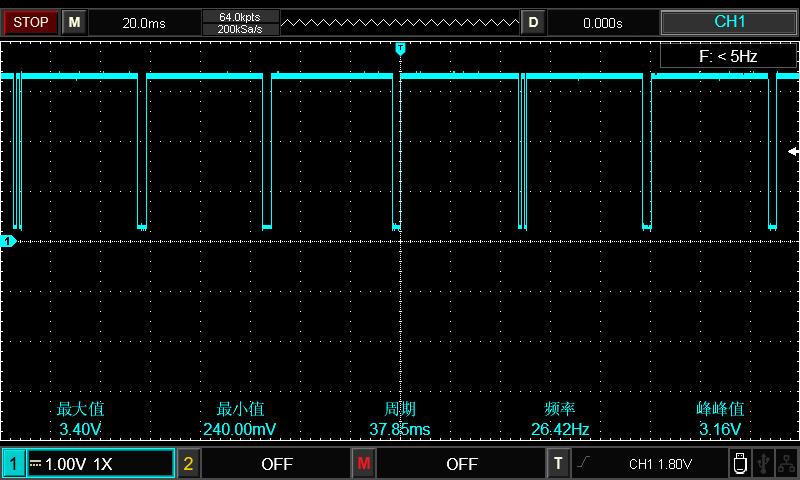

(图15)

采集卡还支持软件触发功能,即使没有外部触发信号,您仍然可以进行数据采集。触发波形和触发方式可以根据不同的应用场景进行调整,如果您需要进行二次开发或需求升级,也可以与我们的公司联系。我们将提供相应的支持和服务。

2.3自检与调试

在设计上位机主板之前,当您获得采集卡板子时,您也可以直接通过电脑读取采集到的数据。通过使用仿真软件,您可以将采集到的模拟量数据进行仿真并生成图形展示。采集卡的信号源可以通过连接信号发生器或函数发生器来提供模拟量输入。这样,您可以在没有设计上位机主板的情况下进行数据读取和仿真展示。

(图16)

关于电脑仿真软件需要下载MATLAB和下载USB3.0驱动等软件环境

- 如何下载详看-附图二

采集卡通过USB3.0和电脑连接,您需要准备如下工具:

- 电脑一台(已安装好软件环境)

- 采集卡和电源适配器

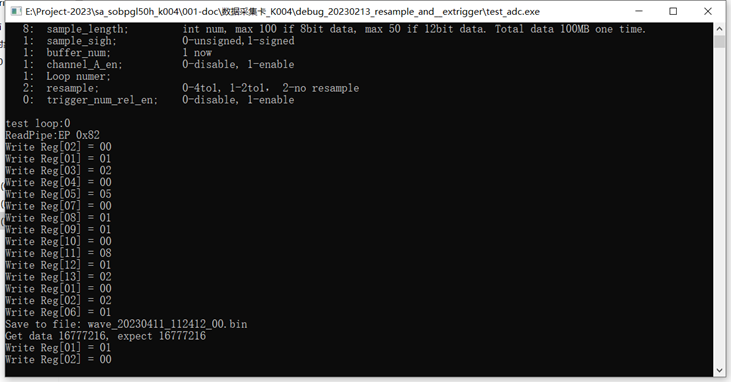

- 测试脚本debug_20230213_resample_and__extrigger(可向我司索要压缩包)

- 需要一台信号发生器/函数发生器

- 需要一条两头TYPE-A接口的USB3.0线

(图17)

准备好以上物件后,执行以下步骤:

- 将板子对接好电源,连接好USB接口和信号发生器输入接口

(软件触发可以不接外触发接口),接线可参考(图14)

- USB连接电脑,检查设备管理器---通用串行总线控制器,是否识别到USB设备

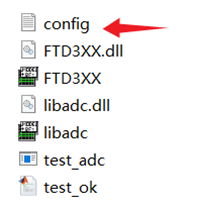

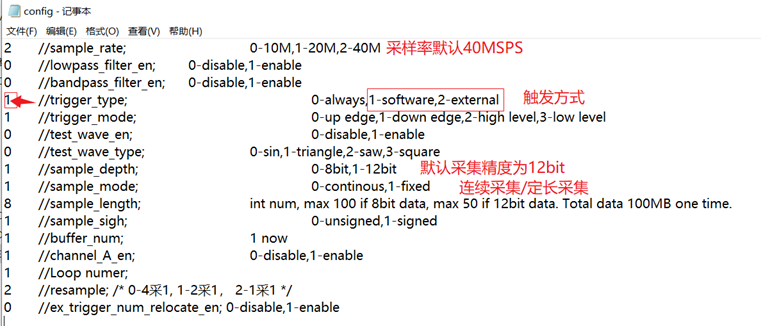

- 打开debug_20230213_resample_and__extrigger文件夹,配置config。

(图18)

(图19)

一般我们只用改触发方式,不接外触发设备,我直接配置为软件内部触发就行,如图19即可。

需要外触发时,只需要把第四行参数改为2 //trigger_type;

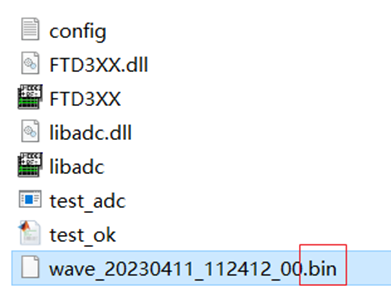

- 配置完后保存关闭config,双击 test_adc脚本,会生产一个.bin文件。

(图20)

(图21)

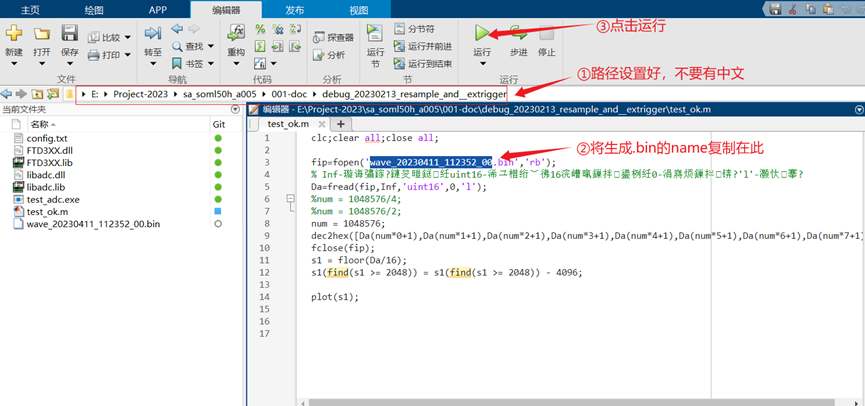

将这个.bin的name复制一下,等会会用到。(name每次生成都不一样)

这个.bin文件就是采集卡采集的数据,不能直接打开,要用到matlab。

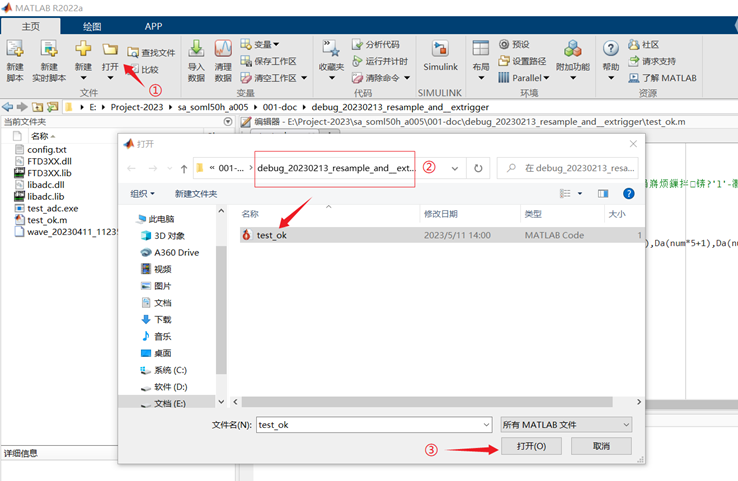

- 如何打开matlab软件,将采集到的.bin文件,变成能直观阅读的波形图表呢?

首先打开我们debug_20230213_resample_and__extrigger文件夹里的test_ok

(图22)

然后把我们上个步骤copy的.bin名称粘贴在这,点击运行

(图23)

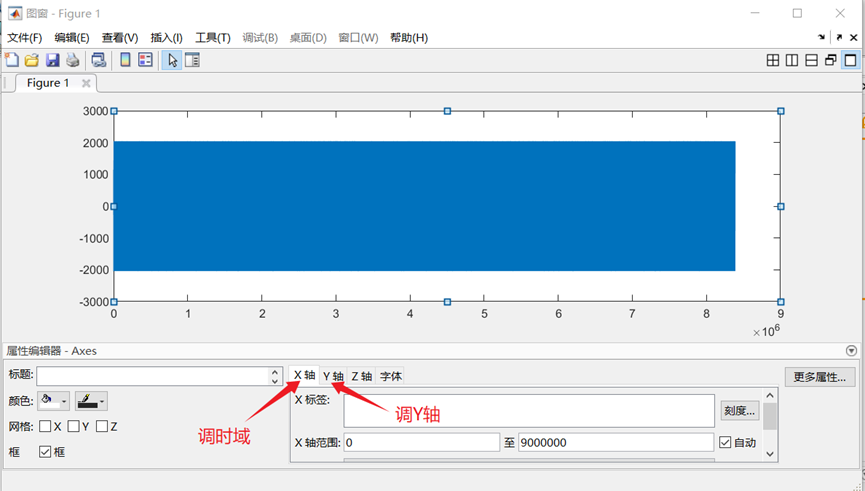

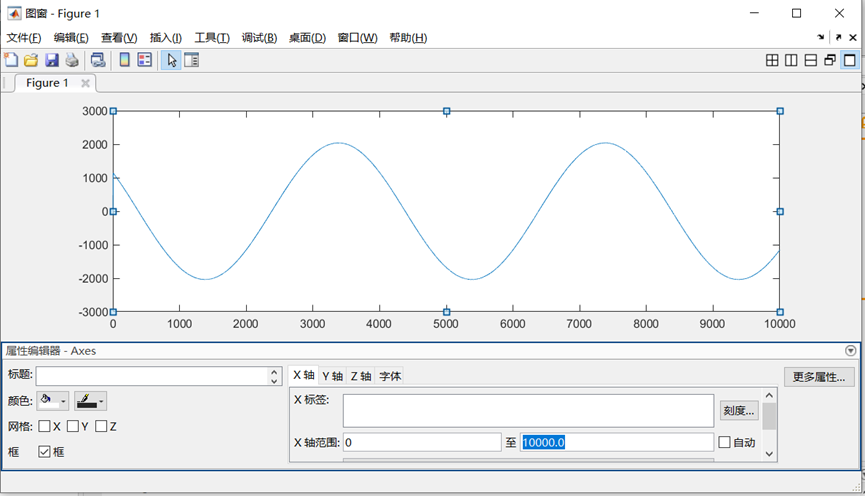

运行结果会有个figure 1弹窗,这就是我们采集卡测到的波形。

(图24)

现在看不出波形,我们要对横纵轴调整一下。X轴是时间,Y轴是电压(需要代入公式)。

点击figure1弹窗-----查看----属性编辑器,页面会变成如下图。

(图25)

将时间调整一下

(图26)

| X轴 | 一个单位代表25纳秒 | 如图26,周期为4000个单位,即T=0.1ms,是一个频率为10k的正弦波 |

| Y轴 | 一个单位代表10/4096 伏 | 如图正弦波最高点约为2000个单位,2000*10/4096=4.88V. |

而我们电脑生成.bin文件的时候,信号发生器输出给采集卡的波形,正是一个频率10K,-5V~+5V的一个正弦波。和我们仿真结果一致。

以上就是我们用电脑matlab去显示采集卡采集信息的方法和步骤。

3.单板介绍

3.1框图

(图27)

主要有三大模块:

| | FPGA模块 |

| | ADC模块 |

| | USB3.0模块 |

| 4. | 电源系统 |

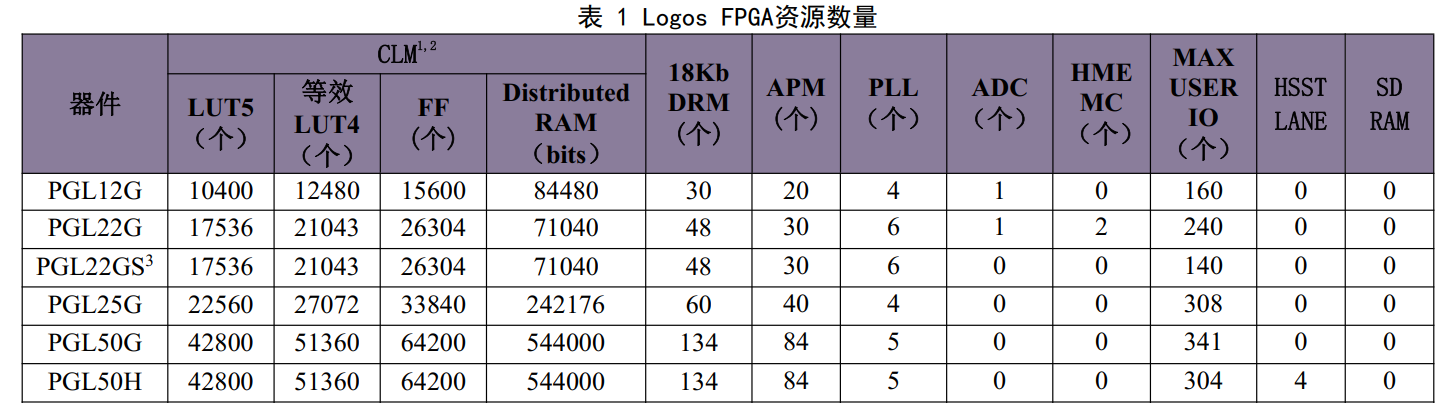

主控采用紫光同创的LOGOS系列的PGL50H_6IFBG484作为核心处理器。该处理器具备以下优势和特性:

1.架构和工艺: PGL50H_6IFBG484采用完全自主产权的体系结构和主流的40nm工艺,确保了高性能和可靠性。

2.高速串行接口和温度范围:该处理器具备HSST高速串行接口,可在-40C至100°C的温度范围内工作。

3.核电压: PGL50H 6IFBG484的核心电压为1.2V,提供稳定的电源供应。

4.模块功能: 处理器内部集成了多种功能模块,包括可配置逻辑模块 (CLM) 、专用的18Kb存储单元(DRM) 、算术处理单元 (APM) 、多功能高性能IO以及丰富的片上时钟资源等,以满足不同应用的需求。

5.硬核资源: 此外,PGL50H_6IFBG484还集成了存储控制器 (HMEMC) 和模数转换模块5(ADC) 等硬核资源,进一步增强了处理器的功能和灵活性。

6.配置和安全功能: 该处理器支持多种配置模式,并提供位流加密和器件ID (UID)等功能以保护用户的设计安全。

7.应用领域: 基于以上特点,PGL50H_6IFBG484适用于广泛的应用领域,包括视频、工业控制、汽车电子和消费电子等。

此外采集卡还兼容搭配了2~8G的DDR3可选焊,还预留了FLASH兼容焊盘,可更加需求焊接nand flash或者nor flash。

(图27)

备注:板子上电后FPGA需要配置时间1.35s

4.PCB

4.1尺寸

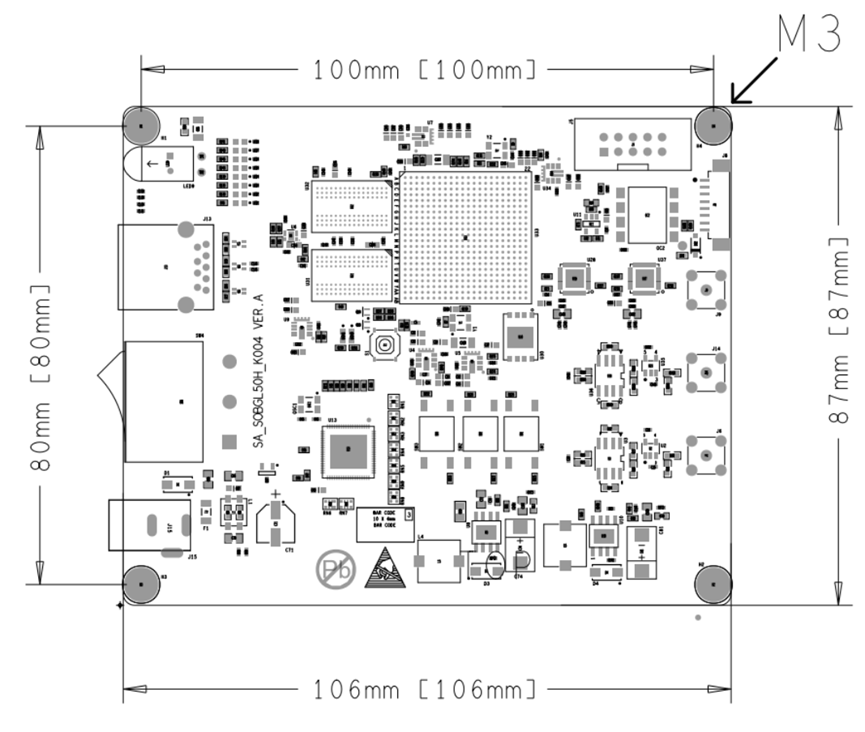

(图28)

- 尺寸:106MM*87MM

- 定位孔:100MM*80MM(M3金属化过孔)

- 板厚:1.6MM

- 层数:8层

- 填孔方式:电镀填平

- 测试:整板飞针测试,AOI测试,BGA/QFN Xray

- 是否阻抗控制:是

- 阻焊:哑黑油墨,白字

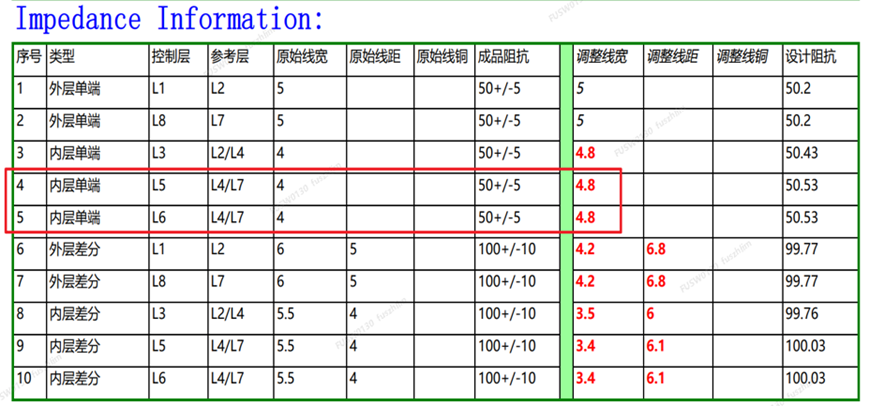

4.2 阻抗

(图29)

USB3.0接口均使用100欧姆的阻抗控制,单端走线使用50欧姆的阻抗控制。

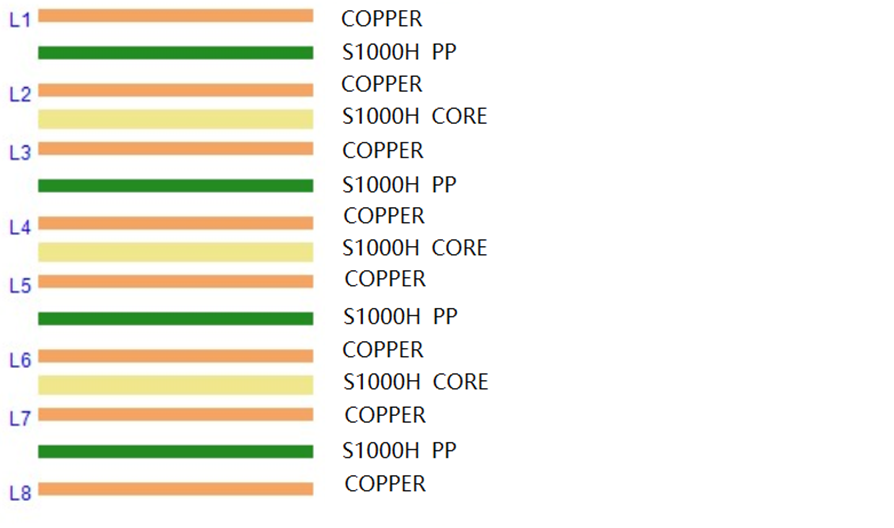

4.3叠层材料

(图30)

5.附录

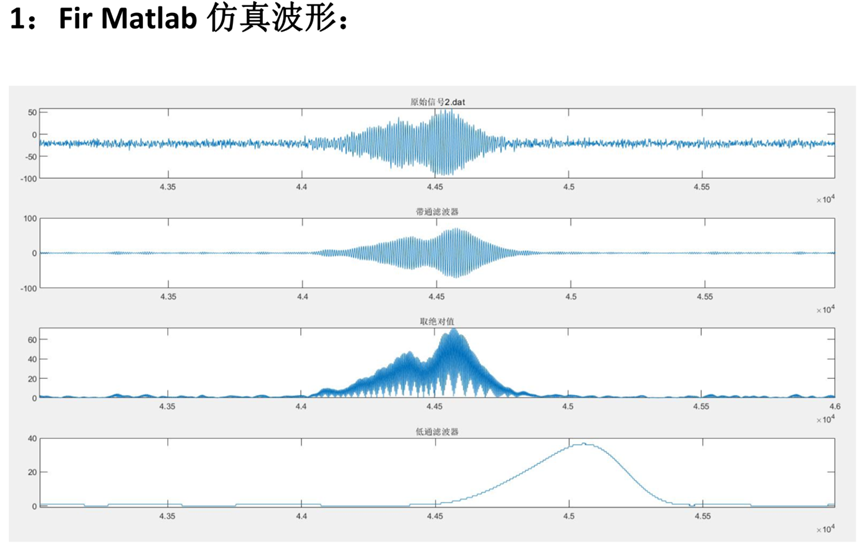

5.1附图一:

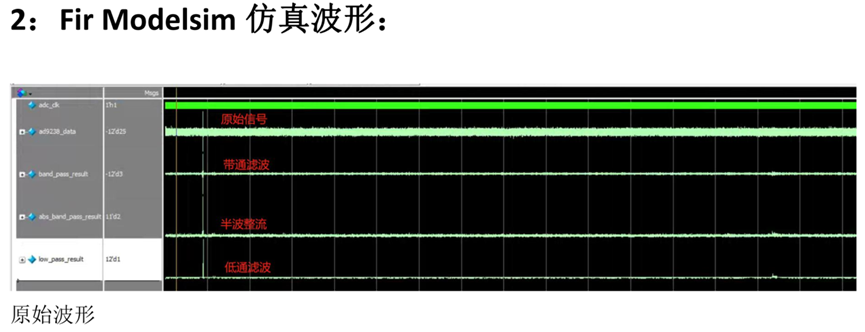

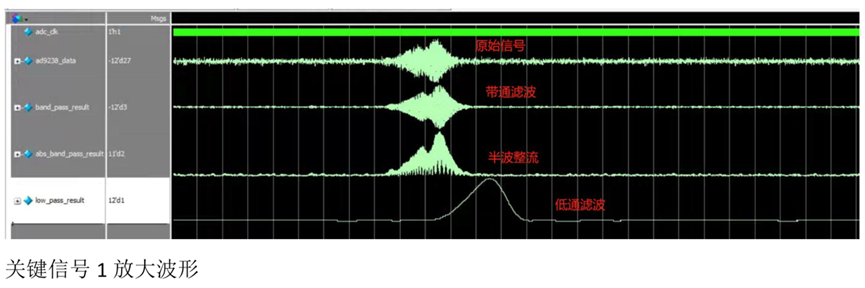

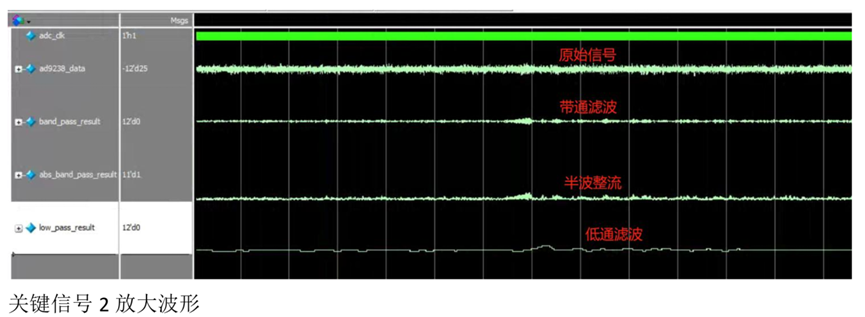

带通64阶,低通1024仿真波形

波形仿真测试步骤:K004波形仿真测试

喜欢谢工碎碎念~点赞~关注~

(图7)

(图7) (图8)

(图8)