实战案例-FPGA如何实现JESD204B最小确定性延迟

目录

简介

在204B中通过如下的三个特性来实现确定性延迟

204B实现确定性延迟的过程可以描述如下

RBD 的定义

RBD的设置实例

简介

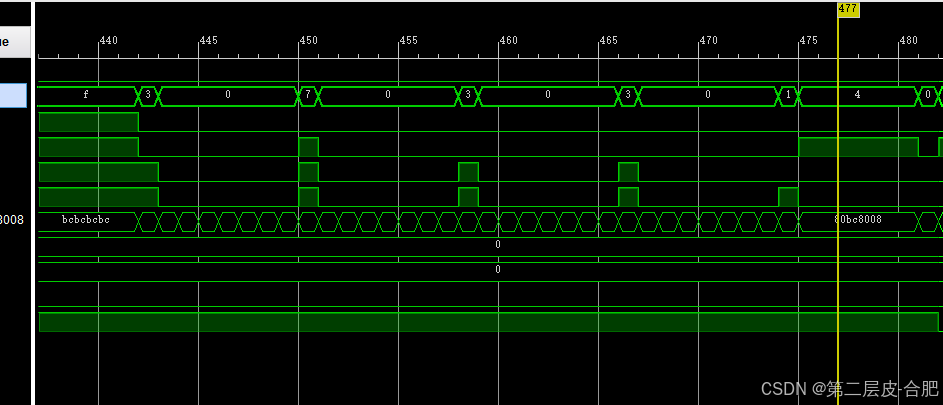

当JESD204B链路首次在子类1和子类2设备中建立时,接收器会输出所示的数据。在所有通道检测到有效数据后,数据会在LMFC交叉点输出。通过调整buffer_delay寄存器上的输入字节数,可以实现最小延迟。

buffer_adjust寄存器会显示最大允许延迟减少的指示,这反映了每个通道接收器弹性缓冲区写入和读取指针之间的差异。每个10位值中的字节数量反映了每个通道缓冲区的填充水平。最低的数值可用于计算一个值,该值可以编程到buffer_delay寄存器中,以减少相应数量的字节的整体延迟。

编程到buffer_delay寄存器的最大值必须考虑到《实现可重复延迟》中描述的八个字节余量,因此不应超过最低的buffer_adjust值减去八个字节。在修改后的延迟设置生效之前,必须重置JESD204接收核心并完成一次完整的链路重新同步周期。

在204B中通过如下的三个特性来实现确定性延迟

1. SYSREF用于所有器件中的本地多帧Local Multi-Frame Clock (LMFC)的同步。

2. 所有 TX在LMFC的边缘发送ILAS系列明确了数据的开始和结束。

3. 所有RX通过ILAS来判断出数据的开始和结束并和LMFC对齐,通过调整弹性缓冲器(elastic buffer:RBD)来补偿个条lane上的延迟,使得RX各条lane的数据对齐输出。 上述三点具体的实现过程,可以通过下图进行生动的描述

204B实现确定性延迟的过程可以描述如下

1. SYSREF用于同步TX/RX的本地多帧时钟LMFC。

2. TX侧当SYNC 变高后,所有的Lane在下一个LMFC的边缘开始发送ILAS系列。标注了数据的开始和结束。

3. RX侧的各条lane(有早有晚)在接收到ILAS系列中的R表示数据的开始从而开始按照RBD开设的缓冲器的大小缓存数据。

4. RX侧的所有lane在下一个LMFC的上升沿(RBD=K)开始释放所有的缓冲数据,从而实现了所有lane上的数据对齐。到此完成了同步。

RBD的设置是实现确定性延迟的关键

RBD 的定义

204B中RBD的定义是:

设置RBD的值,可以实现滑动数据释放点相对于LMFC上升沿的位置,例如: – 1 < RBD < K – RBD = K 表示的是所有RX lane上的数据在下一个LMFC的上身沿发出,对应上图15中的情形。

RBD = K-4表示的是所有RX lane上的数据在下一个LMFC的沿之前的4个帧周期发出。

通过修改RBD的值可以实现: – RX侧较早的释放数据来实现较小数据延迟。 – 选择一个最优的RBD值来保证确定性延迟。

RBD的设置实例

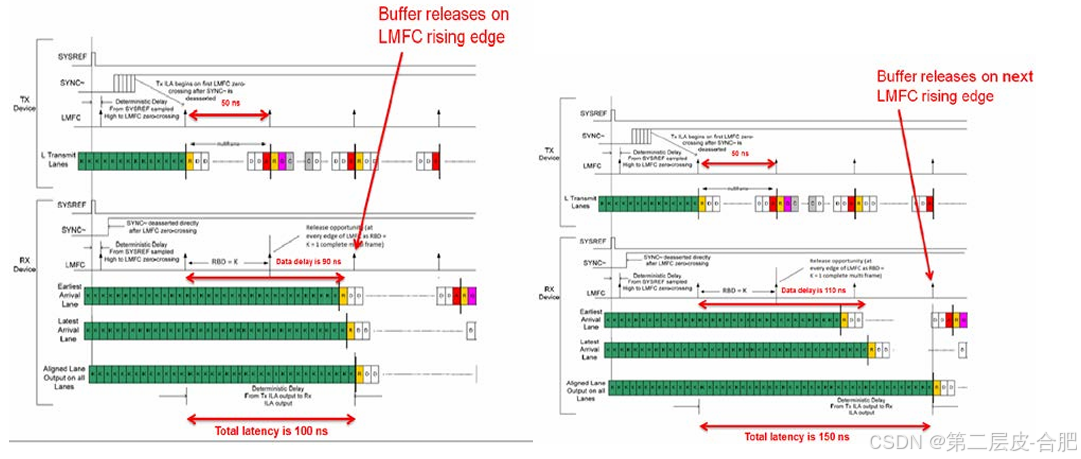

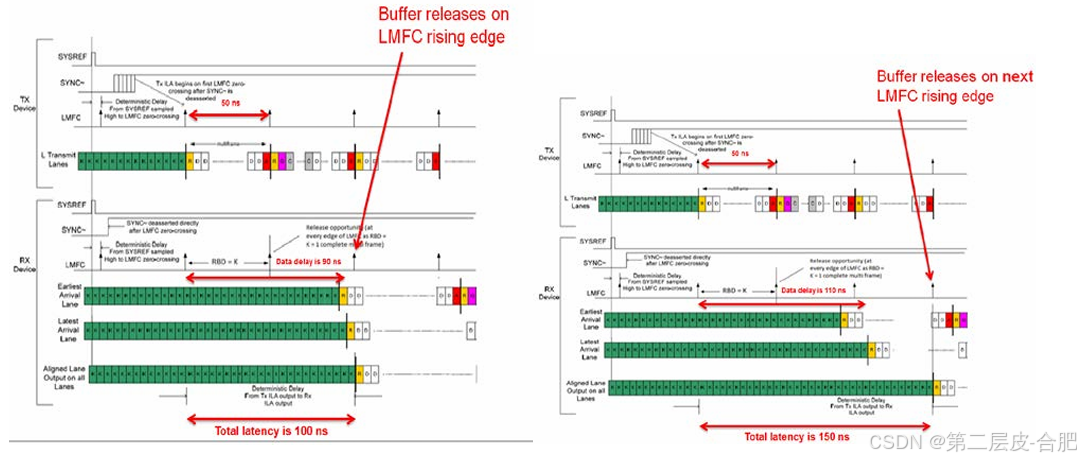

在实际使用中工程师往往简单的将RBD设置为K=32最大值,这样的设置实际运用存在风险,当Link的延迟发生变化时很可能导致不确定性延迟的产生。 设置为K=32仅仅能应对的是在各种情况下(如高低温)最短和最长lane之间的延迟在一个多帧的范围内,如果lane的最长和最短的延迟超过一个多帧,那么当Link的延迟发生变化时会导致延迟也产生了变化。下面将结合实例来说明。假设:

• The LMFC period is 50 ns

• The link delay is 100 ns +/- 10 ns

• Min link delay = 90 ns

• Max link delay = 110 ns

Case 1: 设置 RBD=K。 下图中左边是假设了Link delay 在最小90ns的情况下,右边图是Link Delay在最大110ns的情况下,可以看到如果设置K=32在两种情况下会导致延迟从100ns变化到150ns变化了一个多帧的时间。从而导致了延迟的不确定。 发生延迟不确定的原因是lane上的最短和最长延迟跨越了一个帧的边缘。

Case 2 : 设置RBD≠K。 可以尝试将RBD设置为K的一半来解决延迟的跳动。但在实际使用中需要搜索最优的RBD值, 下面将介绍如何搜索最优的RBD值。

RBD最优值搜索方法

RBD的最优值搜索如下:

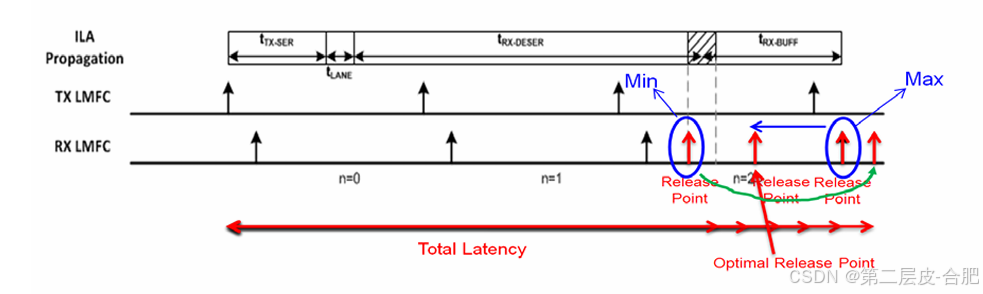

• 改变RBD的值从K~1 直到观察到延迟有一个LMFC周期的跳动。图中蓝色所示RBD的设置从大(Max)到小(min),那么延迟(total latency)的值也将从大到小的变化,但当RBD设置到Min的时候会发现Latency 并不是最小而是跳到了最大处(图中蓝色箭头所示)。

• 将观察到一个周期LMFC跳动点的RBD设置为边界值,再以不跳动的值的范围的一半为margin加上边界值做为最后的RBD值,如图中最优的RBD箭头所示。