[一生一芯] 如何基于iSTA 分析时序

安装环境

1. 下载代码

git clone git@github.com:OSCPU/yosys-sta.git

2. 安装oss-cad-suite

解压缩后, 将`path-to-oss-cad-suite/bin`加入到环境变量`PATH`中, 即可调用工具包中的yosys.

wget https://github.com/YosysHQ/oss-cad-suite-build/releases/download/2025-06-10/oss-cad-suite-linux-x64-20250610.tgz3. 安装依赖

sudo apt install libunwind-dev liblzma-dev # iEDA的依赖库

4. 安装iEDA

在 yosys-sta 目录下安装

make init # 下载预编译的iEDA和nangate45工艺库确认环境是否已经OK

echo exit | ./bin/iEDA -v # 若运行成功, 终端将输出iEDA的版本号运行示例

yosys 提供了一个用例。在yosys-sta 目录下运行如下命令。

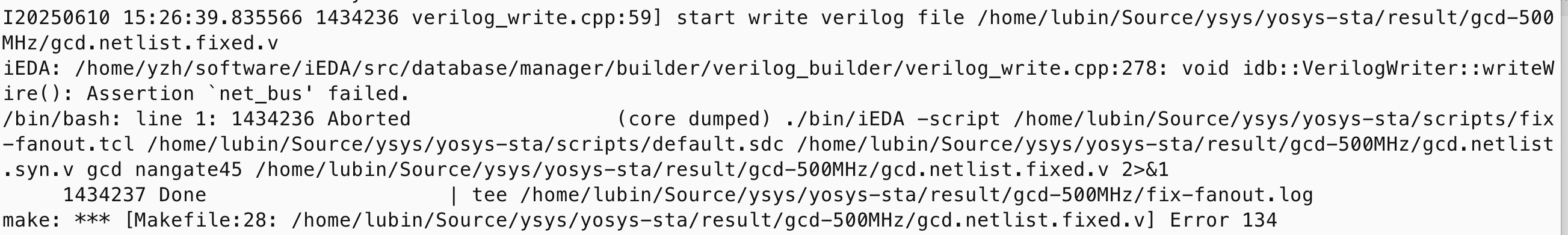

make sta但是存在 缺失修复后的网表问题,

先采用手动复制综合网表作为修复后的网表的方式,临时规避这个问题

cp gcd.netlist.syn.v gcd.netlist.fixed.v实战用例

1. 把需要进行分析的v文件拷贝到 example 目录

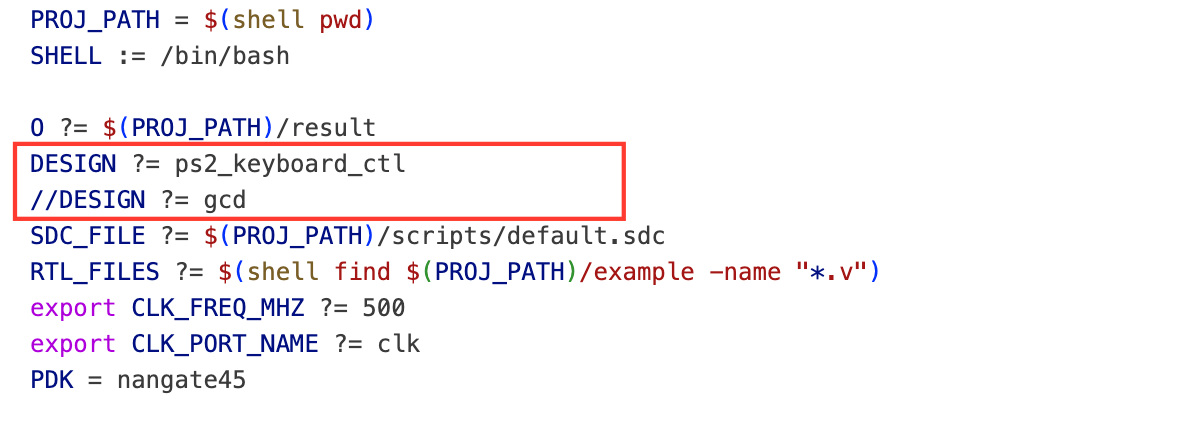

2. 修改 Makefile中的 DESIGN 字段,跟自己的模块明保持一致。

3. 最后执行

3. 最后执行

make sta