博图 SCL 编程技巧:灵活实现上升沿与下降沿检测案例分享(上)

博图 SCL 编程技巧:灵活实现上升沿与下降沿检测案例分享

在 PLC 编程中,检测信号从 0 变为 1 (上升沿) 或从 1 变为 0 (下降沿) 是最基础也是最关键的操作之一。它常用于启动单次动作、计数、状态切换等场景。在西门子 TIA Portal 环境中,虽然梯形图 (LAD) 提供了直观的 P (上升沿) 和 N (下降沿) 指令,但在 SCL (结构化控制语言) 中,我们拥有更灵活和强大的实现方式。本文将分享几种在 SCL 中实现边沿检测的方法及其适用场景。

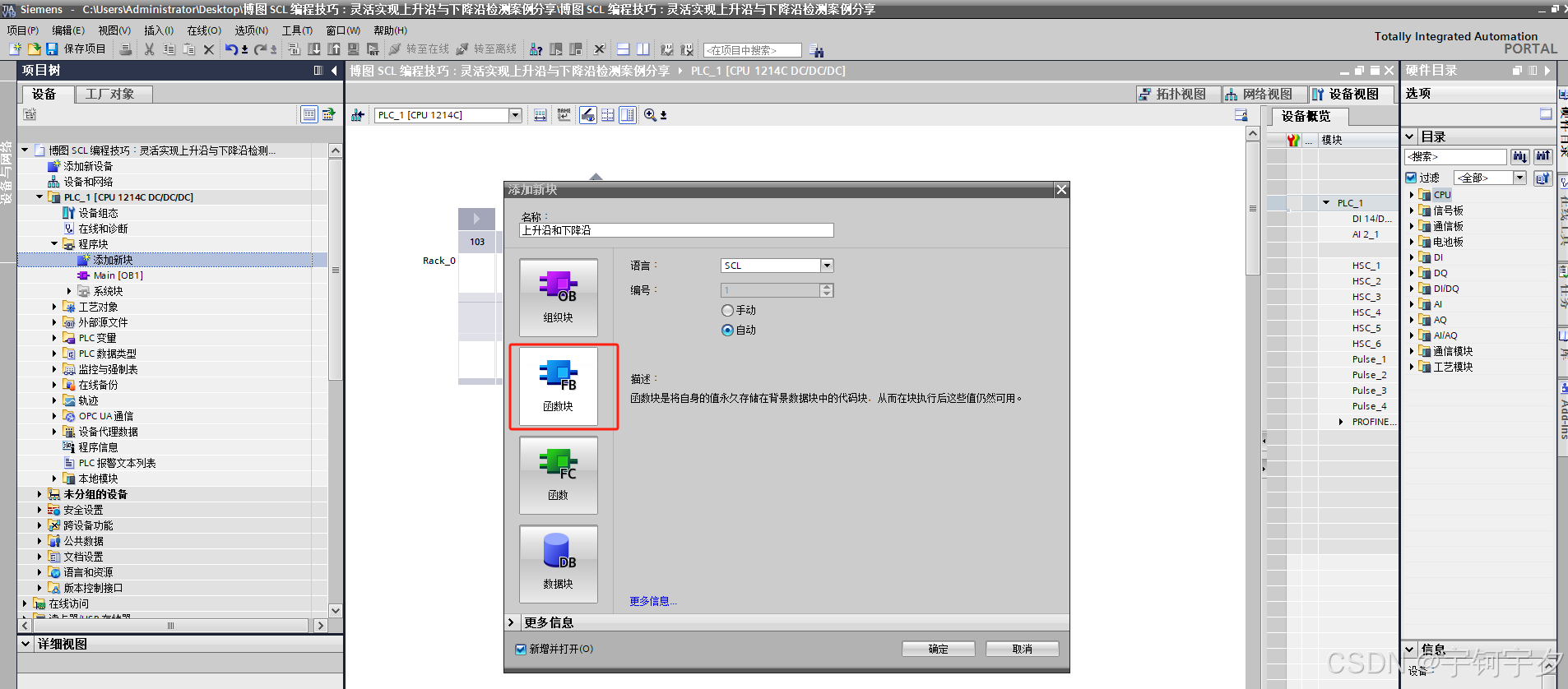

方法 1:使用标准系统函数块 (R_TRIG / F_TRIG)

这是最推荐、最符合 IEC 61131-3 标准且资源管理最清晰的方式。TIA Portal 提供了现成的边沿检测函数块。

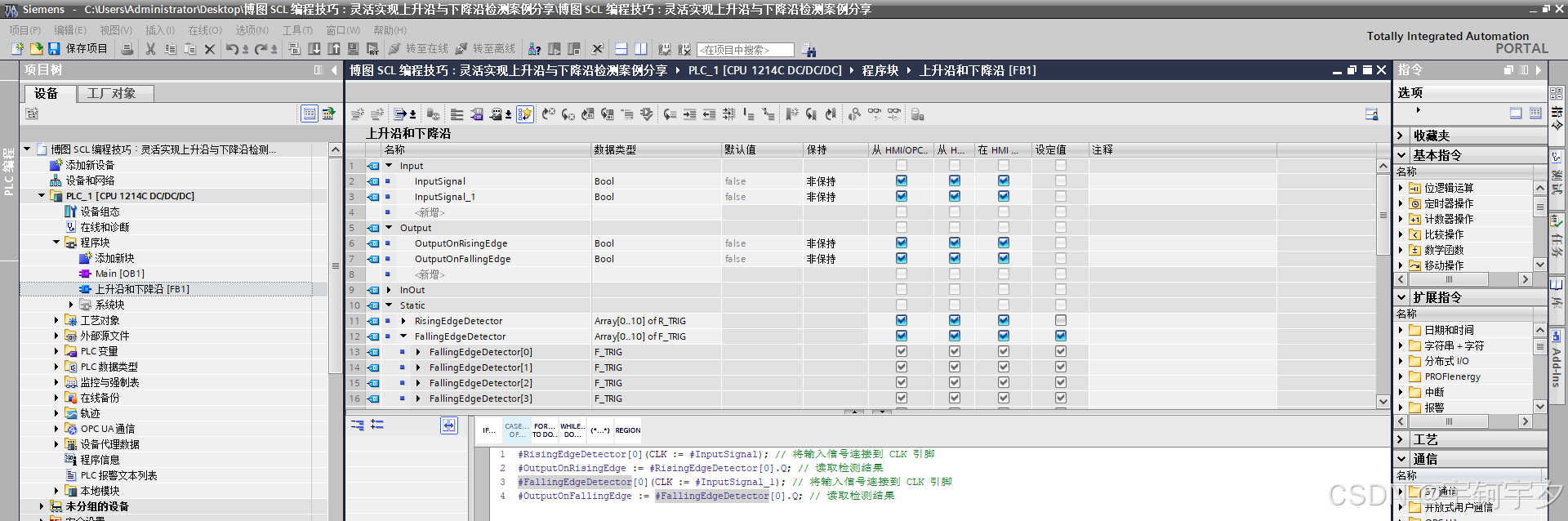

1.1 上升沿检测 (R_TRIG)l

VAR// 输入信号InputSignal: BOOL;// 实例化上升沿检测块RisingEdgeDetector: R_TRIG;// 输出 (检测到上升沿时为 TRUE)OutputOnRisingEdge: BOOL; END_VAR

// 主执行逻辑 RisingEdgeDetector(CLK := InputSignal); // 将输入信号连接到 CLK 引脚 OutputOnRisingEdge := RisingEdgeDetector.Q; // 读取检测结果

1.2 下降沿检测 (F_TRIG)

VAR// 输入信号InputSignal_1: BOOL;// 实例化下降沿检测块FallingEdgeDetector: F_TRIG;// 输出 (检测到下降沿时为 TRUE)OutputOnFallingEdge: BOOL; END_VAR// 主执行逻辑 FallingEdgeDetector(CLK := InputSignal_1); // 将输入信号连接到 CLK 引脚 OutputOnFallingEdge := FallingEdgeDetector.Q; // 读取检测结果

优点:

-

标准化: 符合国际标准,代码可读性高。

-

封装性: 边沿检测逻辑被封装在块内,隐藏了内部状态。

-

易维护: 块自动管理其内部存储(通常是静态变量),无需用户手动声明“上次状态”。

-

多实例化: 同一个函数块可以轻松创建多个实例检测不同信号。

缺点:

-

需要实例化一个单独的块,稍微增加一点代码量(但通常可以忽略)。

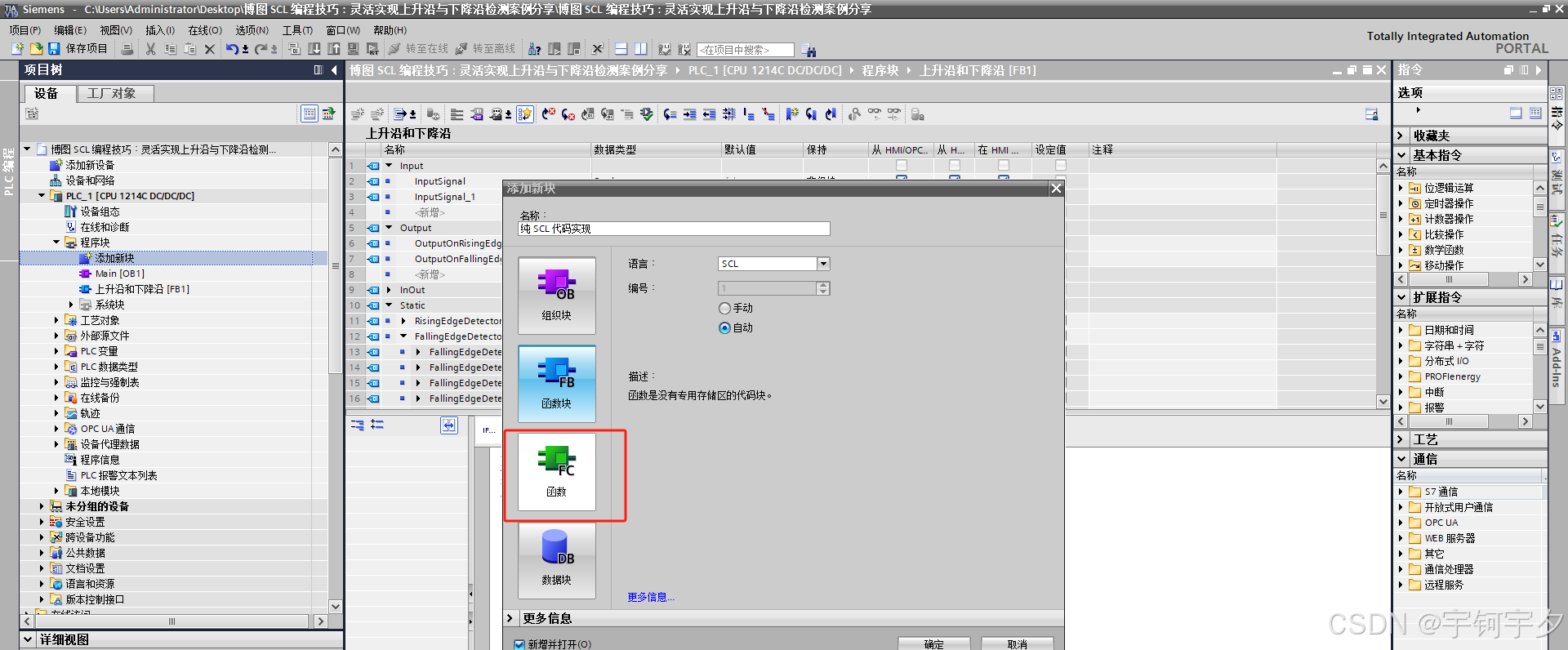

方法 2:纯 SCL 代码实现 (使用静态变量存储上次状态)

如果你不想实例化额外的块,或者需要在简单逻辑中快速实现,可以直接用 SCL 代码编写边沿检测逻辑。核心是使用静态变量 (STATIC) 保存信号在上一扫描周期的状态。

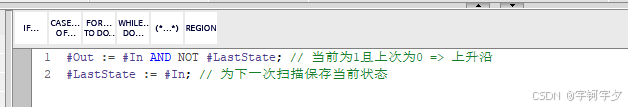

2.1 上升沿检测 (纯 SCL)

scl

VAR_INPUTIn: BOOL; // 输入信号 END_VAR VAR_OUTPUTOut: BOOL; // 检测到上升沿输出 TRUE (仅一个周期) END_VAR VARLastState: BOOL := FALSE; // STATIC 变量 (默认初始化 FALSE) 存储上一次状态 END_VAR

// 主执行逻辑 Out := In AND NOT LastState; // 当前为1且上次为0 => 上升沿 LastState := In; // 为下一次扫描保存当前状态

2.2 下降沿检测 (纯 SCL)

scl

VAR_INPUTIn_1: BOOL; // 输入信号 END_VAR VAR_OUTPUTOut_1: BOOL; // 检测到下降沿输出 TRUE (仅一个周期) END_VARVARLastState_1: BOOL := FALSE; // STATIC 变量 (默认初始化 FALSE) 存储上一次状态 END_VAR

// 主执行逻辑 Out_1 := NOT In_1 AND LastState_1; // 当前为0且上次为1 => 下降沿 LastState_1 := In_1; // 为下一次扫描保存当前状态

优点:

-

简洁: 对于单个信号的简单检测,代码非常紧凑。

-

无额外实例: 不需要创建

R_TRIG/F_TRIG实例。 -

理解底层原理: 帮助理解边沿检测的本质。

缺点:

-

状态管理: 需要手动声明和管理静态变量

LastState。 -

可读性稍差: 对于不熟悉此模式的读者,不如直接调用函数块直观。

-

复用性差: 如果需要检测多个信号,需要为每个信号复制一份类似的代码(声明单独的

LastState),不如函数块实例化方便。 -

易出错: 如果忘记更新

LastState或在错误的位置更新,会导致逻辑错误。