【详细记录】我的第一次裸片硬件尝试:stm32f103c8t6最小核心板一板成

目录

- 目录

- 器件选型

- 1. LDO,5V转3V3

- 2. 晶振

- 3. 复位

- 4. 烧录

- 5. BOOT

- 6. MCU

- 原理图绘制

- 布局

- 接线

- 下单+买元器件

- 焊接与测试

- 总结与后续

搞嵌软已有一段时间,软件方面已比较熟悉,但在硬件方面只设计过简单的模块拼接PCB,基本上都是连连看连对了即可使用的模块化设计。

嵌入式嘛,硬件还是得会一点的。为了提升硬件设计能力,决定跳出舒适圈,尝试从零开始制作裸片电路板。因此选择了最经典的STM32F103C8T6最小核心板作为第一个项目。

最终成功一板成,一次焊接通过。虽然过程中遇到了不少问题,但收获颇丰。以下详细记录整个制作过程:

器件选型

1. LDO,5V转3V3

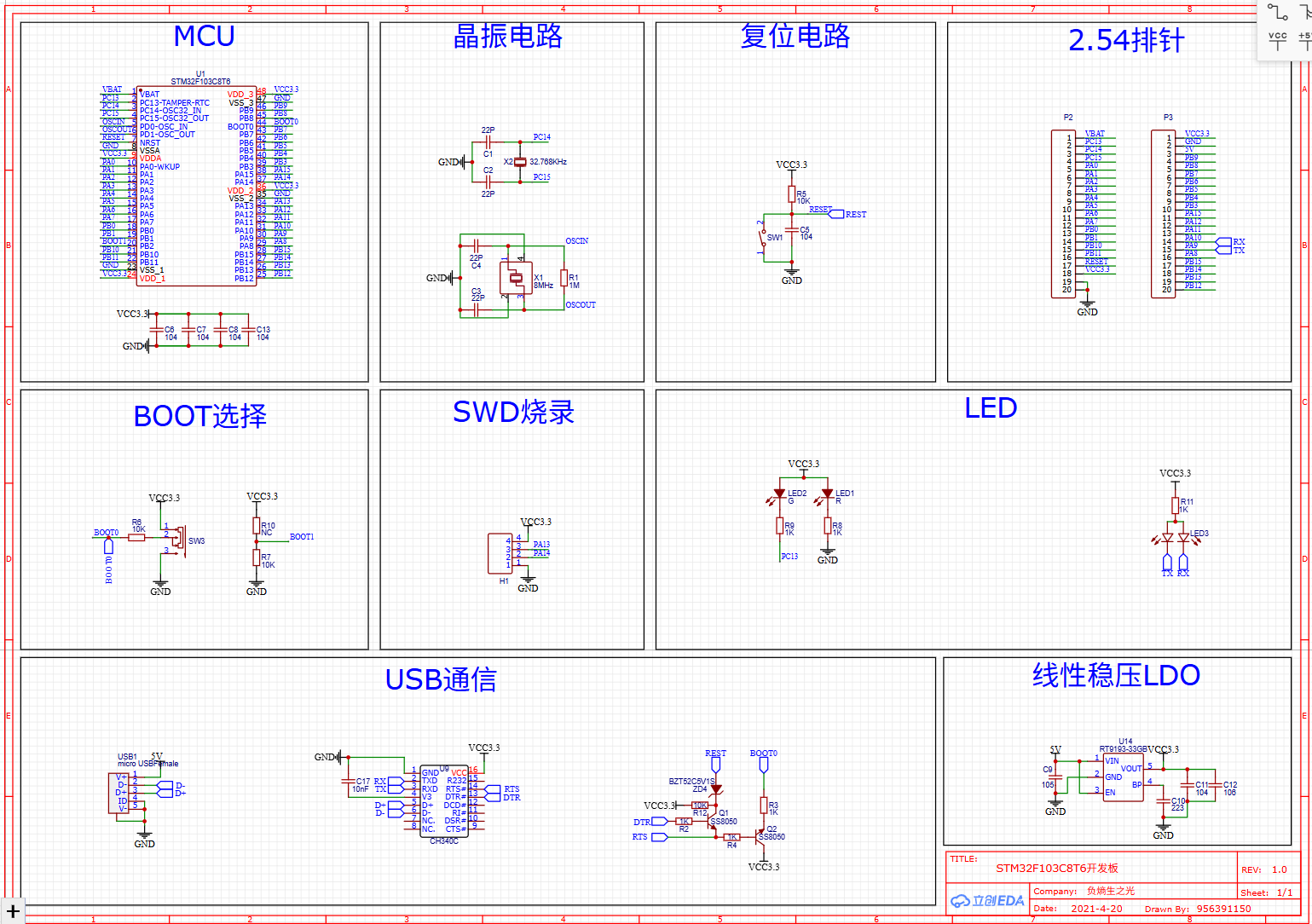

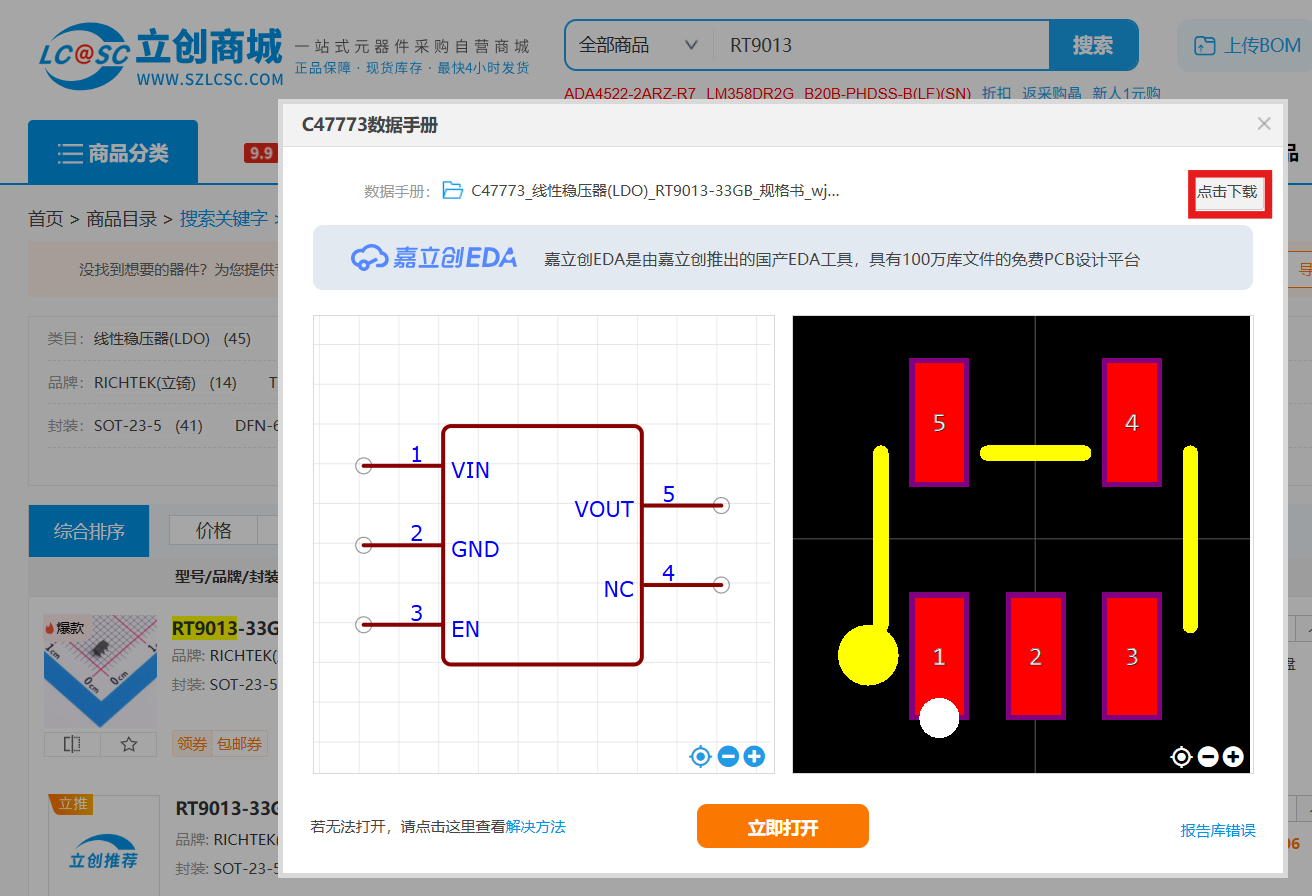

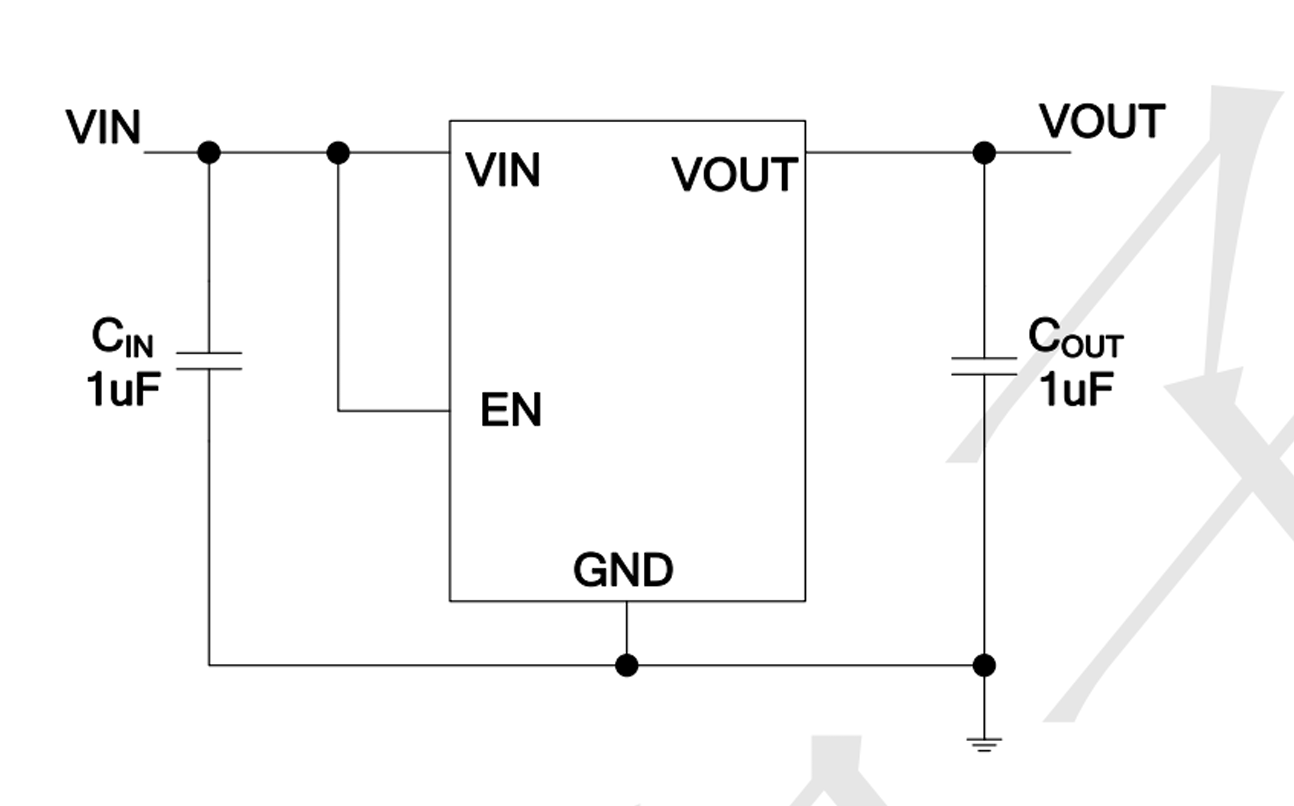

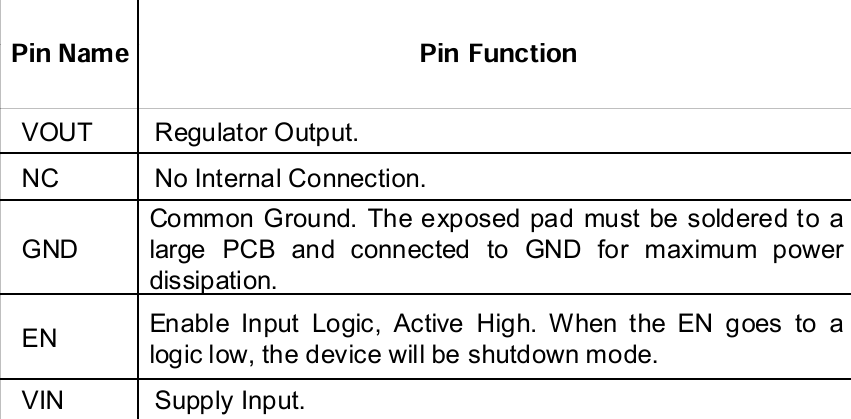

选择RT9013作为电源管理芯片。由于需要输出3.3V,因此选用RT9013-33GB型号。首先查阅立创商城的数据手册进行了解。

根据数据手册中的参考电路进行设计。电路需要两个1nF陶瓷电容和一个100kΩ电阻,统一采用0603封装的贴片元件。

|  |

|---|

对于外部电源方案,考虑到这是最小核心板设计,无需配置18650电池或航模锂电池等复杂供电系统。因此选择常用的Type-C接口提供5V电源输入。

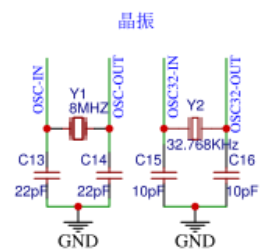

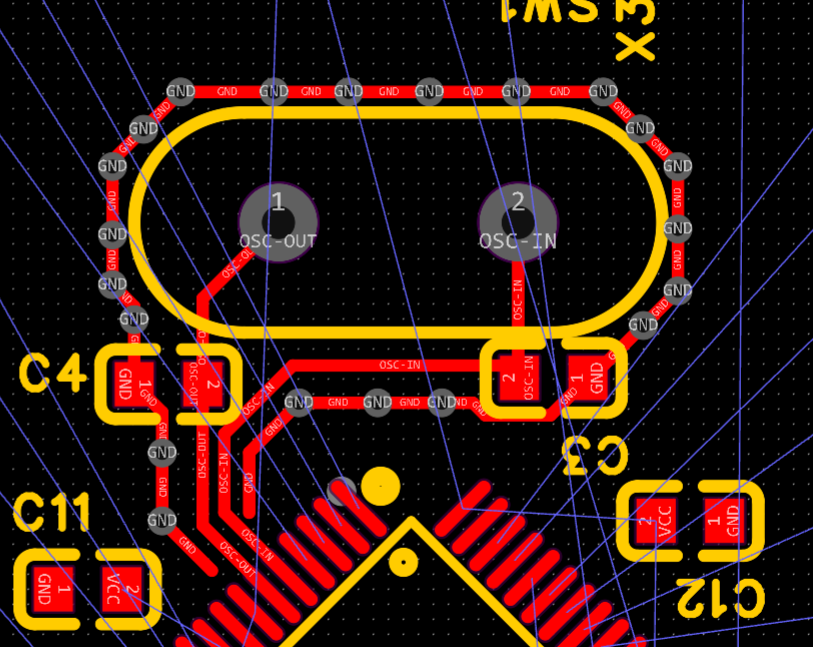

2. 晶振

设计中需要配置 8MHz 和 32.768kHz 两个晶振

- 8MHz 晶振:作为高速外部时钟(HSE)晶振,为MCU系统时钟提供基准频率。STM32内部的主要功能模块,包括定时器、串口通信(USART)、SPI通信、I2C通信等外设的工作时钟,通常基于此系统时钟进行分频或倍频获得。相比内部时钟源,外部晶振具有更高的频率稳定性和精度,是保证系统稳定可靠运行的重要选择。

- 32.768kHz 晶振:作为低速外部时钟(LSE)晶振,主要为MCU的实时时钟(RTC)模块提供时钟信号,用于实现精确的时间计时功能。设备中的日历功能、定时功能等都依赖于此晶振的精确计时。

两个晶振均选用无源晶振。

由于数据手册信息有限,按照常规电路进行设计,重点关注匹配电容的容值选择。参考电路如下:

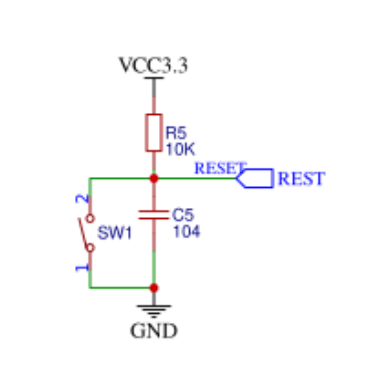

3. 复位

采用标准复位电路设计,按键型号可任意选择。需要注意该芯片采用低电平复位方式。

|

|---|

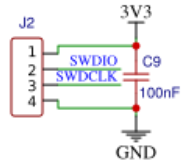

4. 烧录

烧录接口采用标准的4pin排针设计。

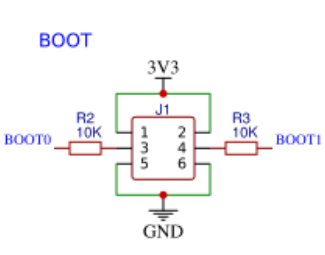

5. BOOT

| BOOT0 引脚 | BOOT1 引脚(或选项字节) | 启动模式 | 用途说明 |

|---|---|---|---|

| 0 | X(任意) | 主闪存启动 | 从内置Flash启动(用户程序存储区,默认模式)。 |

| 1 | 0 | 系统存储器启动 | 从系统存储区启动(内置Bootloader,用于串口/USB下载程序)。 |

| 1 | 1 | SRAM 启动 | 从内置SRAM启动(用于调试或临时运行代码,掉电后程序丢失)。 |

通常选择00/01配置。电路设计需要2个10kΩ电阻和1个2x3P排针。

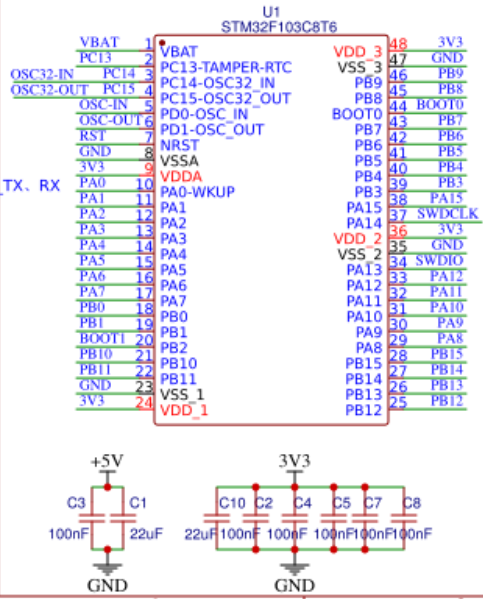

6. MCU

MCU接口按照标准设计,采用2个20P排针。

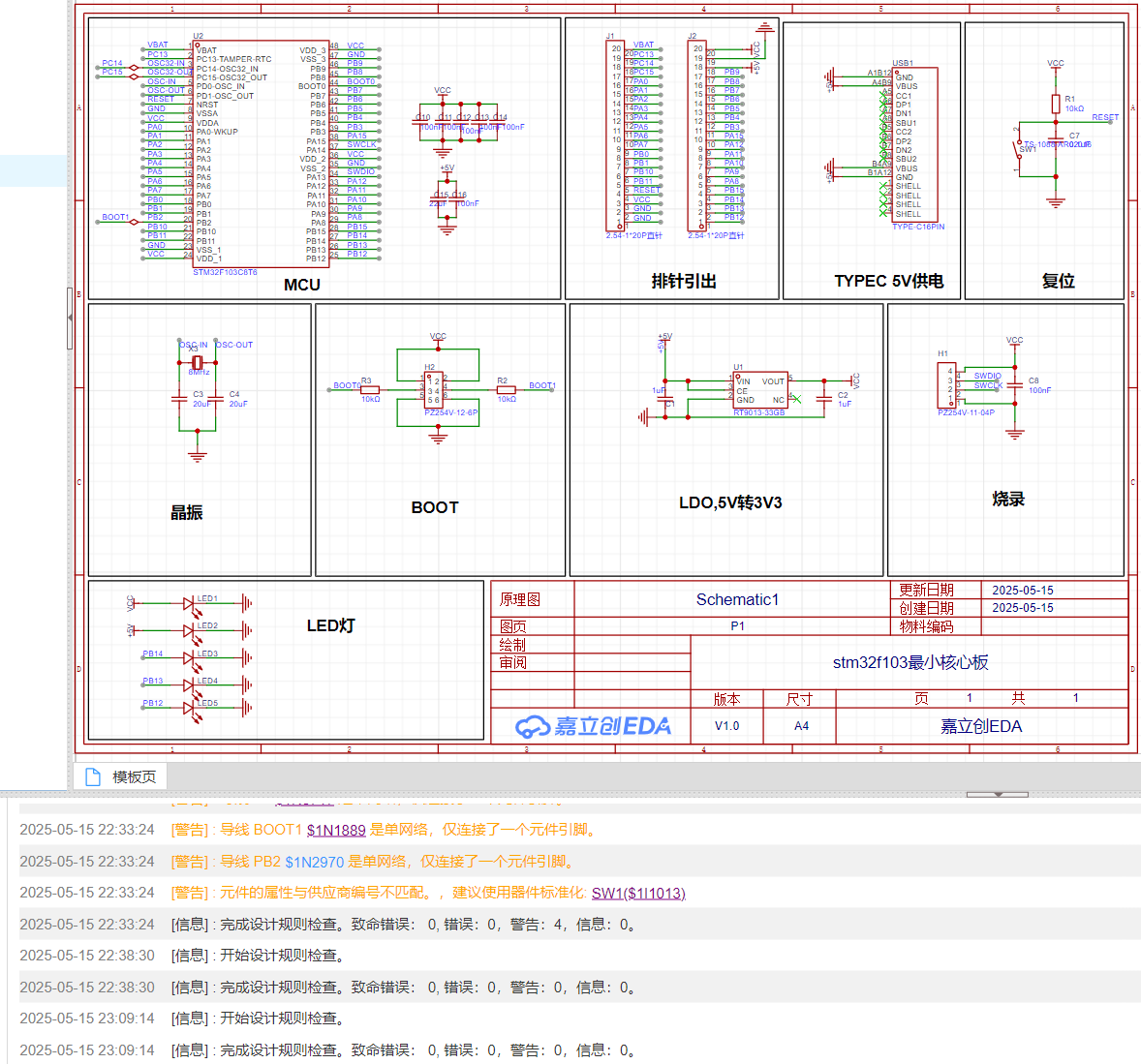

原理图绘制

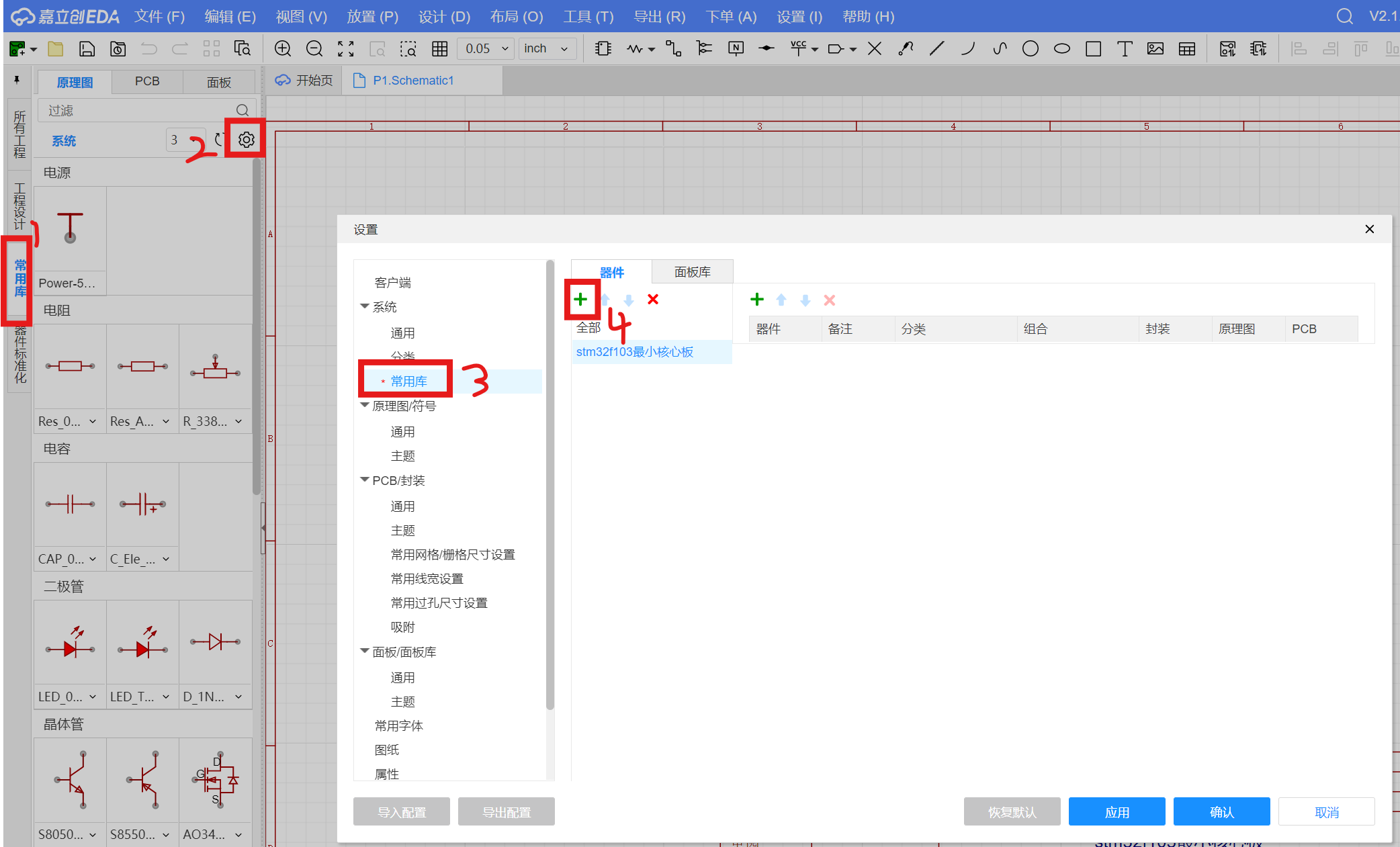

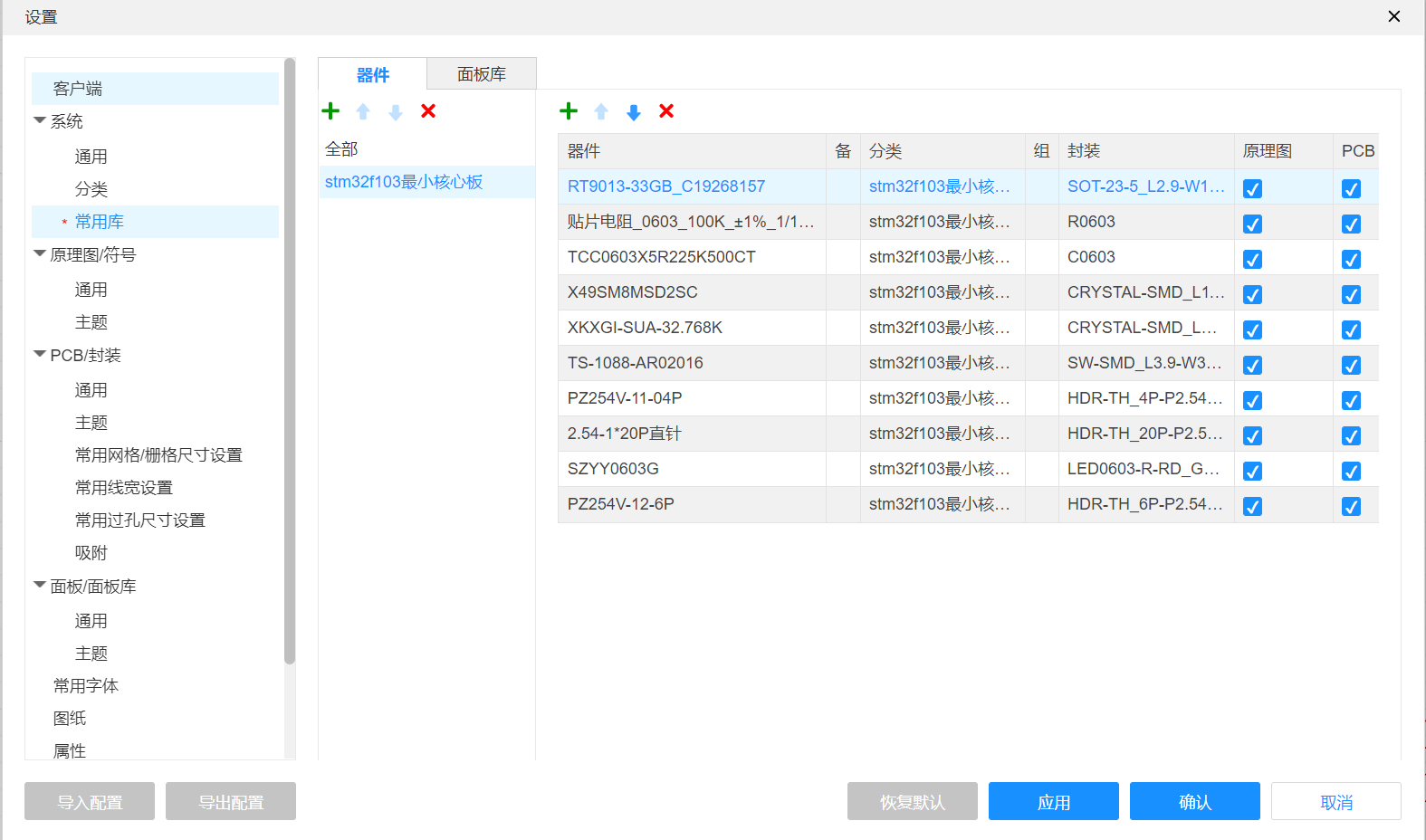

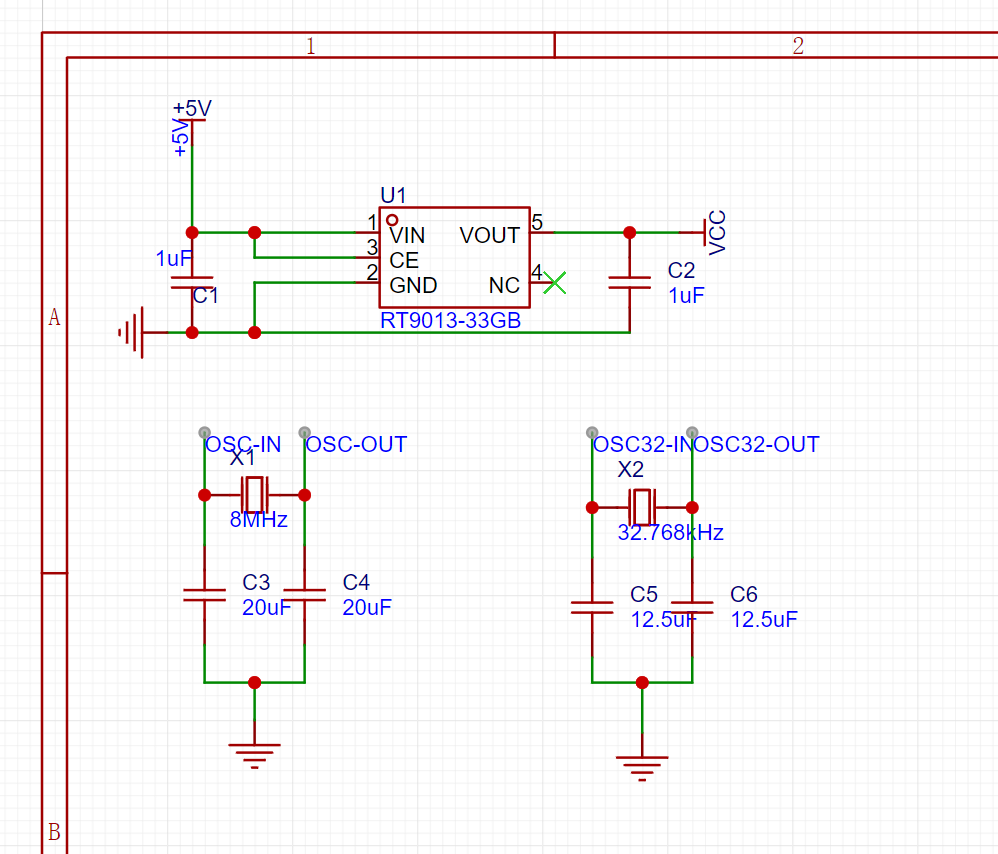

打开嘉立创EDA,首先建立常用元件库。

将上述所有需要的器件添加到库中。电阻电容统一选择0603封装,确保最终丝印标识正确、焊接无误即可。

器件选取完成。

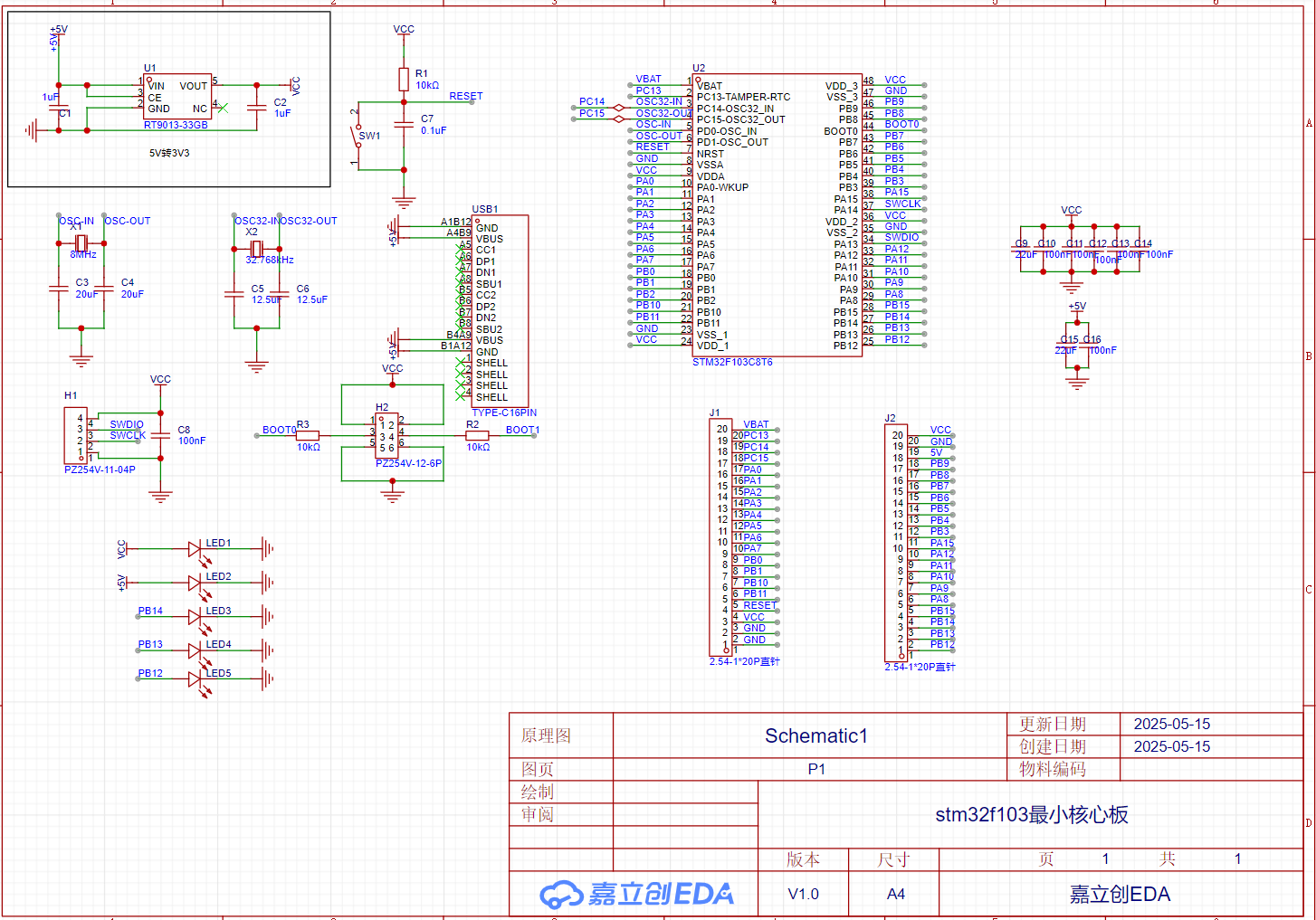

接下来绘制原理图,参考前面器件选型时的参考电路。

原理图绘制完成!

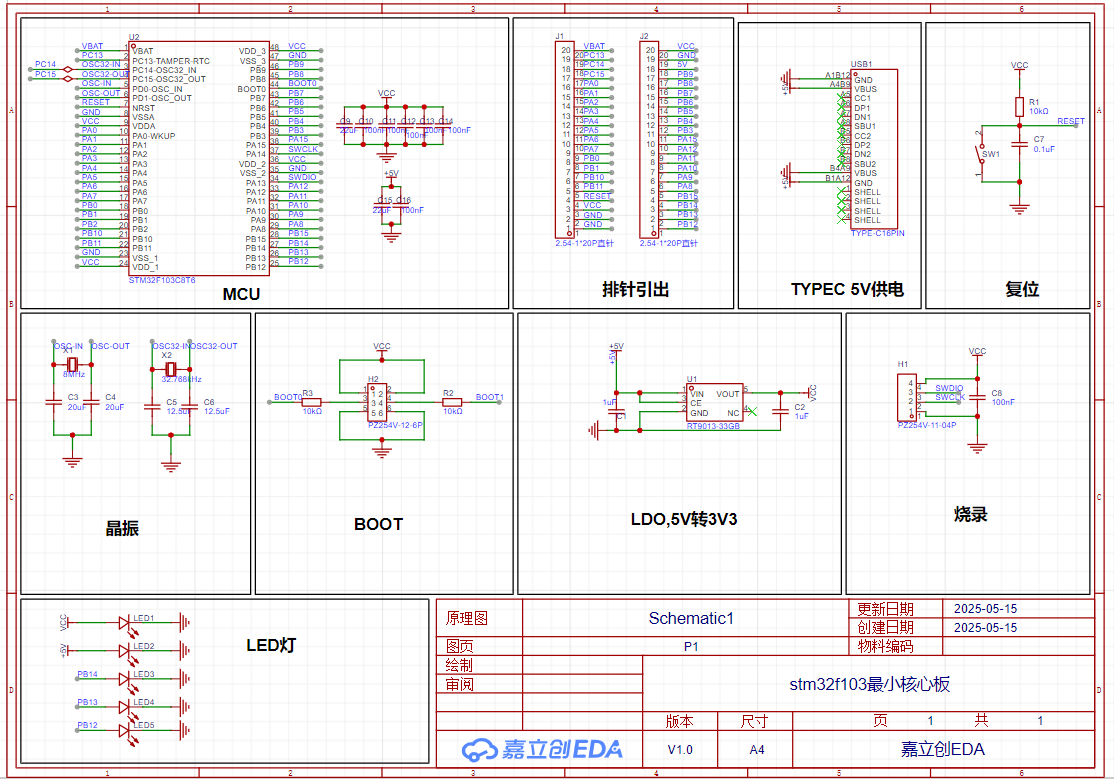

添加边框,提升整体美观度。

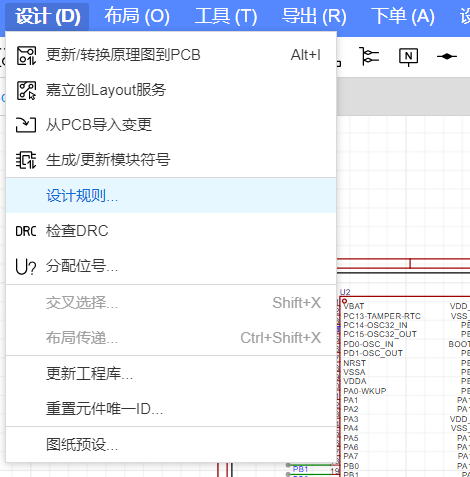

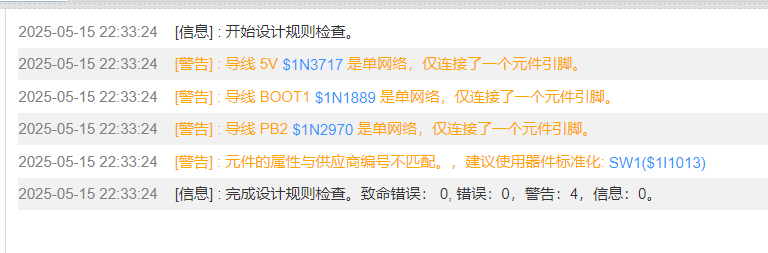

进行原理图检查:设计-设计规则-立即校验

检查发现错误,按照提示进行修复。

修复完成。同时删除了不常用的32.168kHz晶振。

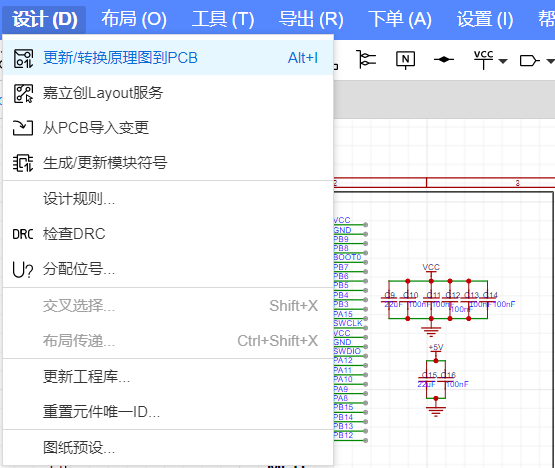

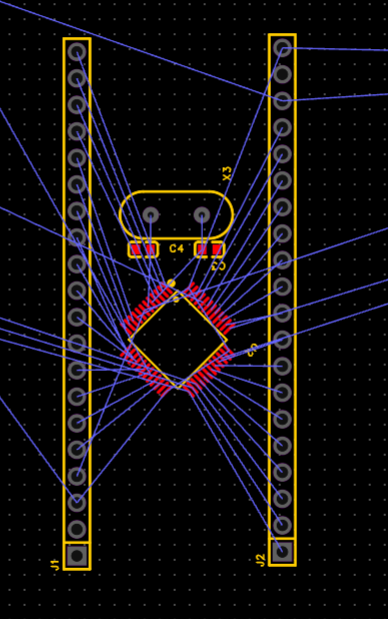

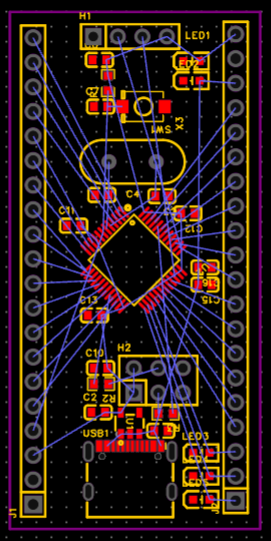

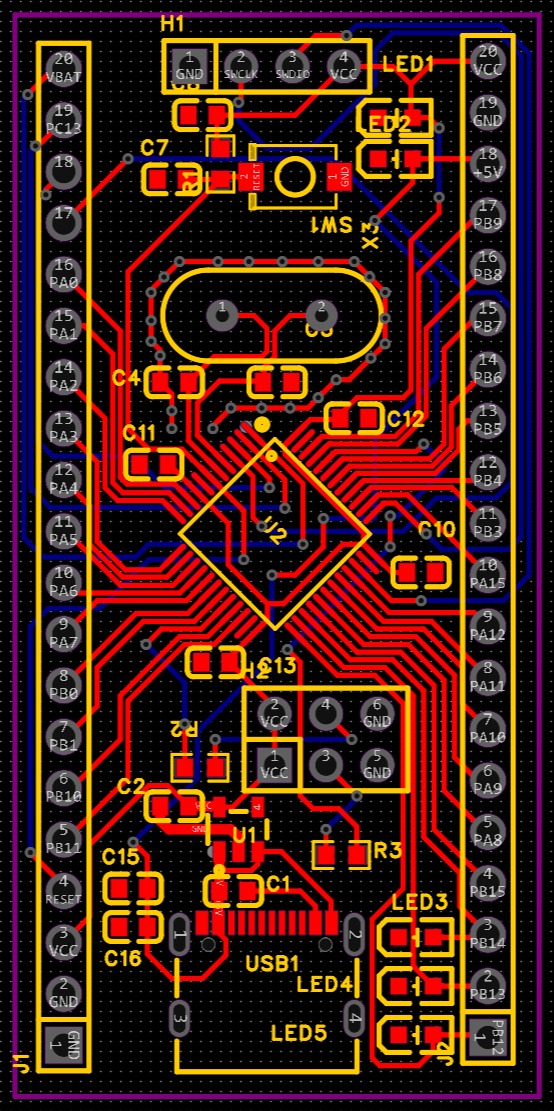

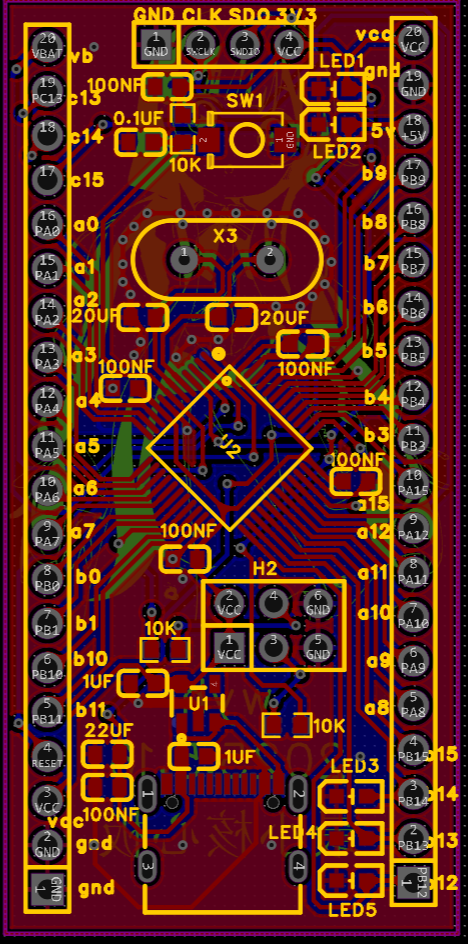

布局

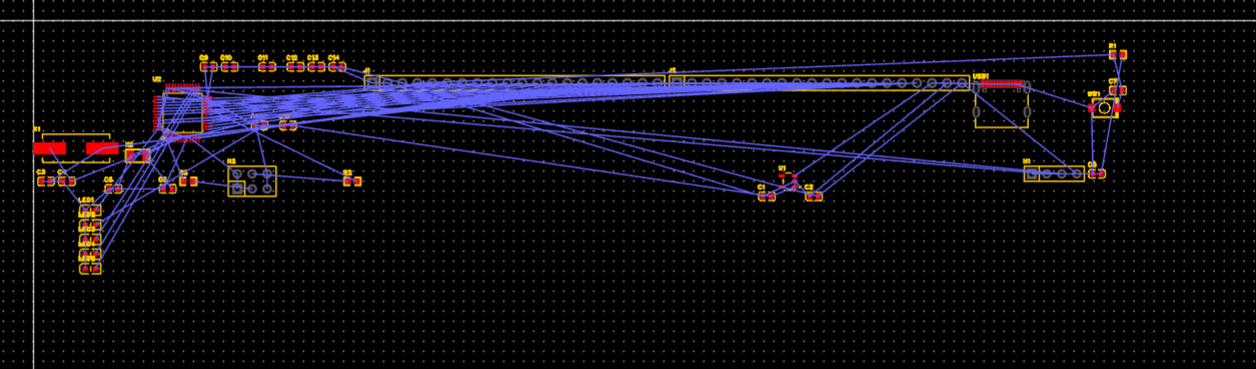

执行"设计-转换原理图到PCB"操作,初始状态下元器件分布较为混乱。首先需要合理布局元器件,为后续布线工作做好准备。

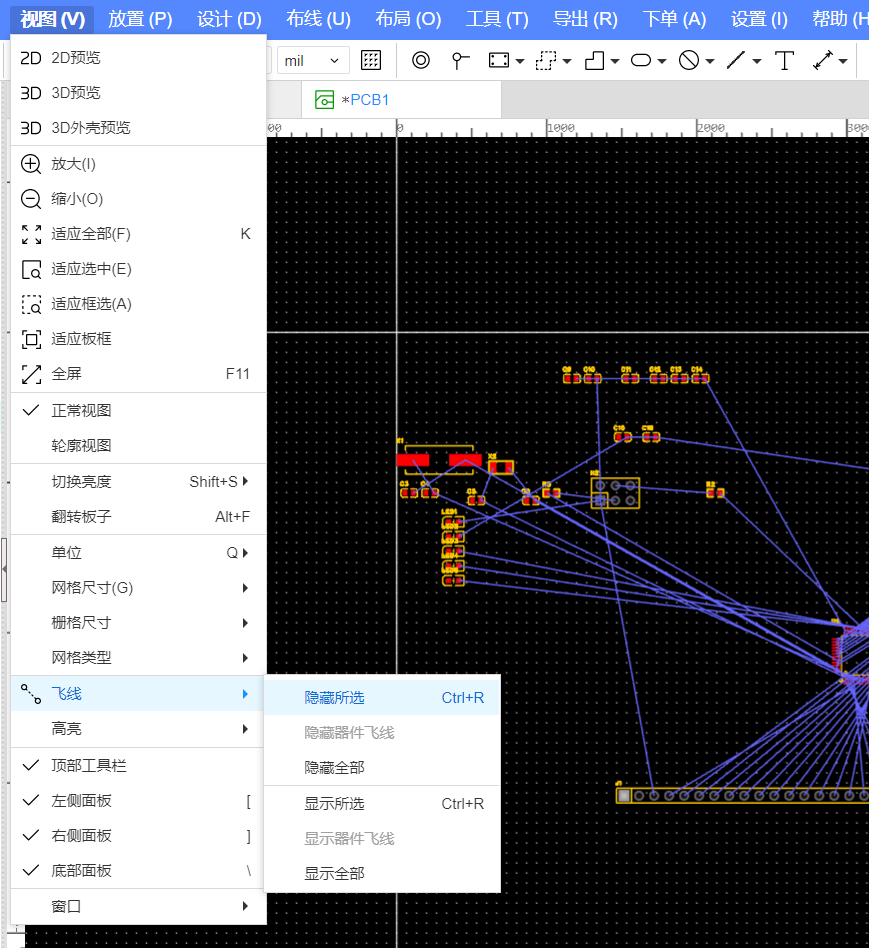

由于GND网络最终通过铺铜连接,为了简化视图,先将GND飞线隐藏:选择某个GND节点,执行"视图-飞线-隐藏所选"。

优先布置晶振位置。虽然理论上晶振布线应尽可能短,但受限于PCB尺寸,如果严格按照最短距离布置,晶振需要放在边缘位置,这会影响引脚引出(晶振下方不宜布线)。

暂时采用现有布局方案,虽然包地设计可能稍显复杂。

元器件布局完成

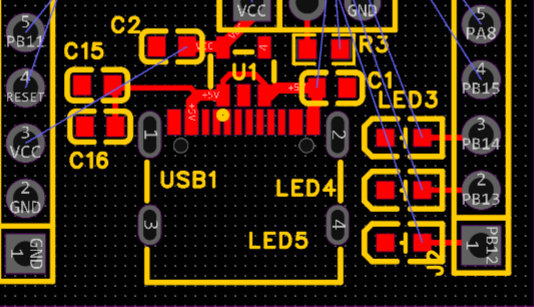

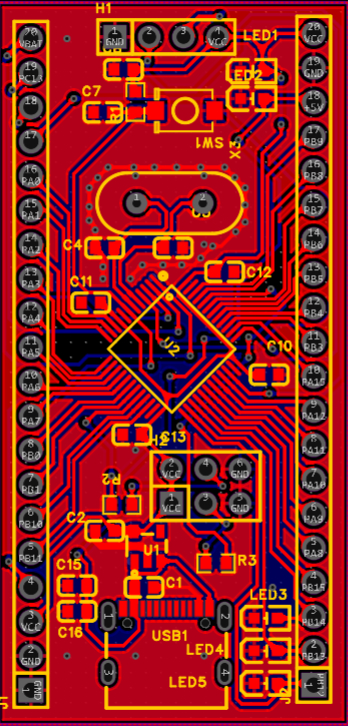

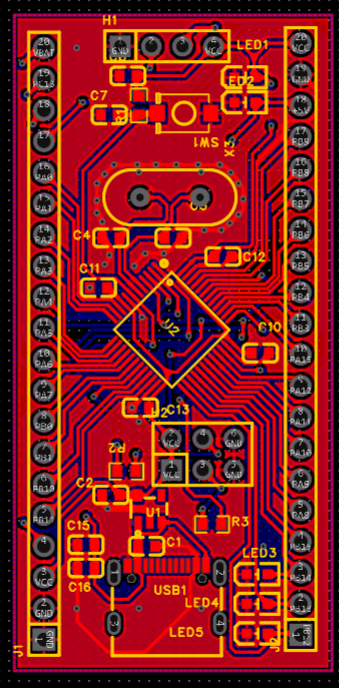

接线

电源线路采用较粗的走线,虽然实际电流不大,但为了保证稳定性。

为晶振设计包地处理

初次布线完成后,咨询同学意见,反馈如下:LDO布线存在问题,GND形成孤岛,且1号管脚为输出端,但我连接到了3号管脚。同时建议晶振的两根走线可以更加靠近。其他连接基本可以正常工作。

问题修改完成

执行后处理操作:泪滴、铺铜、钻孔

进行DRC检查,发现大量孤岛错误。在设计过程中由于隐藏了GND飞线而忽略了这一重要问题。今后一定要注意GND孤岛问题,绝不能因为隐藏显示就完全忽视!

修复孤岛问题。最终通过了所有DRC检查!

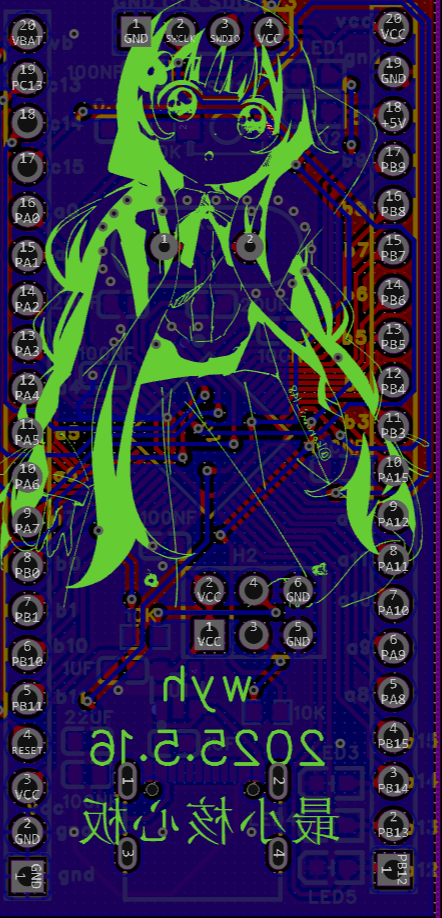

最后进行丝印设计

下单+买元器件

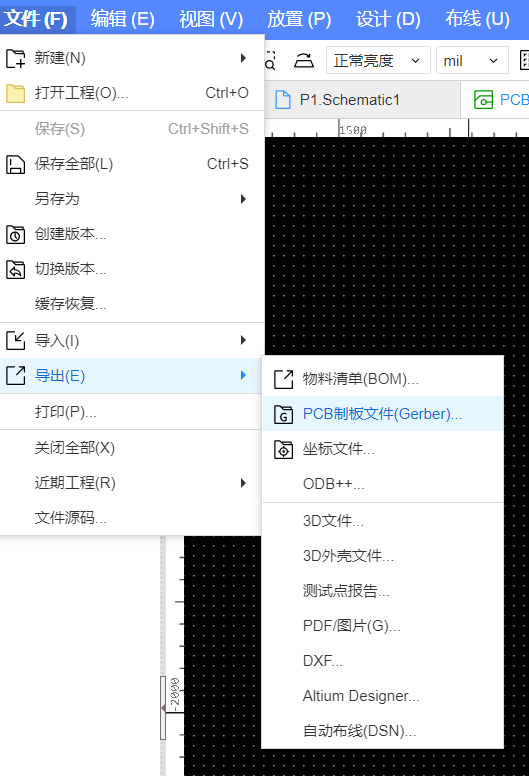

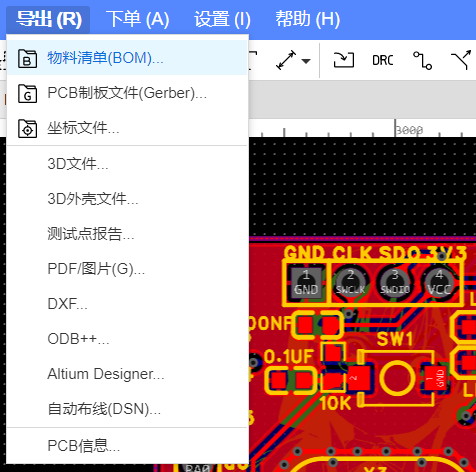

导出制版文件

嘉立创经典白嫖。

等待PCB制作完成。

同时准备物料清单:导出BOM表

|  |

|---|

通过淘宝采购所需元器件。等待快递送达。

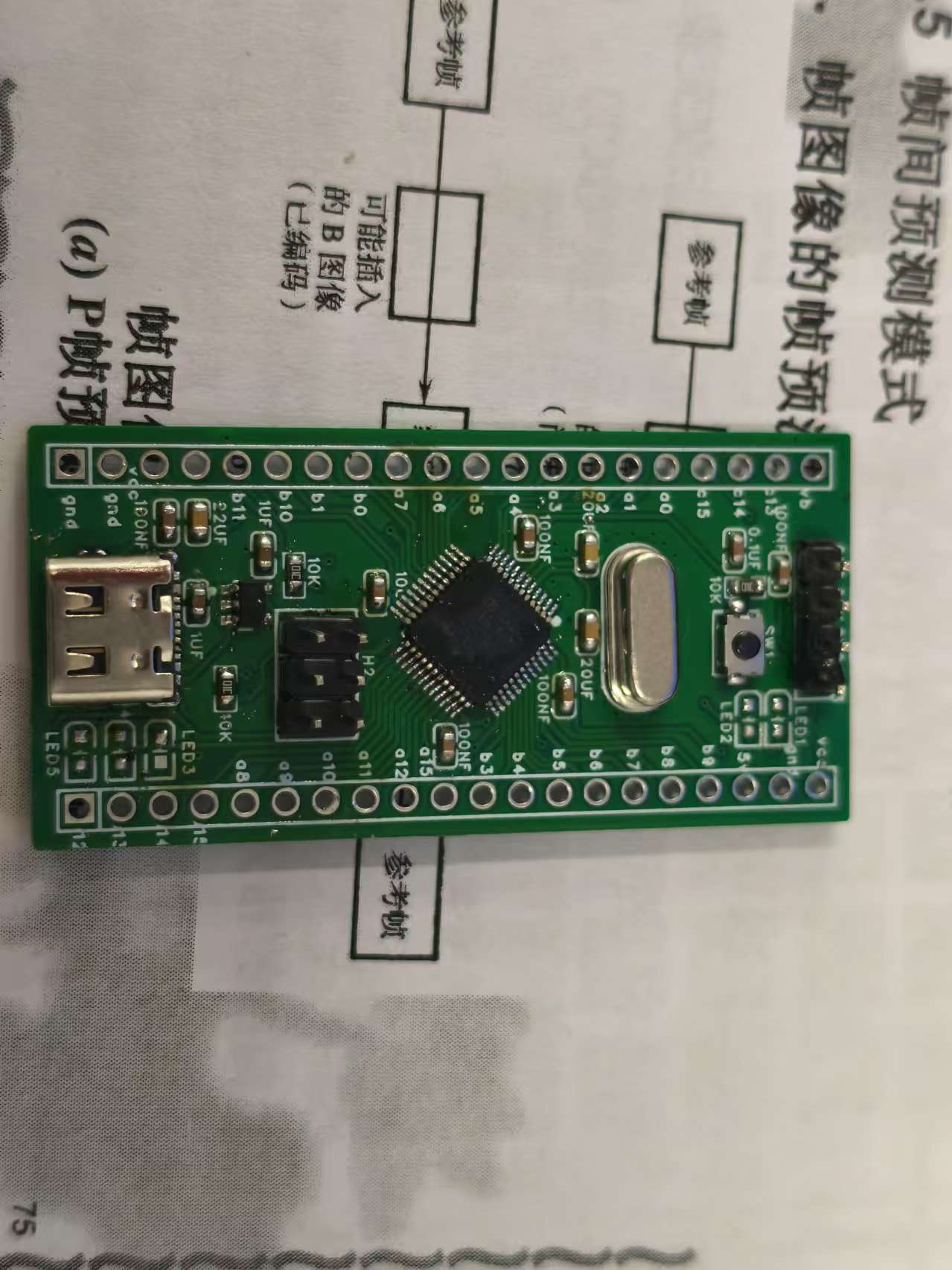

终于到货了!!

焊接与测试

焊接过程中发现5个主要问题:

- 尺寸问题:一位学长询问为何PCB尺寸与市面常见的STM32F103C8T6最小核心板不同,我回答是随意设计的,未考虑标准尺寸。经过交流了解到应尽量使用通用封装,这样在需要将自制板卡插接到其他电路板时,可以直接使用嘉立创现有封装,无需自己绘制,大大提高了通用性。

- LED限流电阻缺失:设计时忘记为LED添加限流电阻,这是一个低级错误,最终只能将已焊接的LED拆除。

- 晶振电容容值错误:晶振匹配电容容值错误,应该是pF级别,我误写成了μF,容值相差一百万倍。幸好及时发现,立即更换了正确的电容。

- 按键布局问题:复位按键极难按压,这是布局设计时完全没有考虑的人机工程学问题。

- Type-C接口问题:Type-C接口焊接难度很高,且未引出D+和D-信号线,导致了一些使用问题,应该采用传统的USB接口。这个选择确实不够明智。

焊接完成效果:

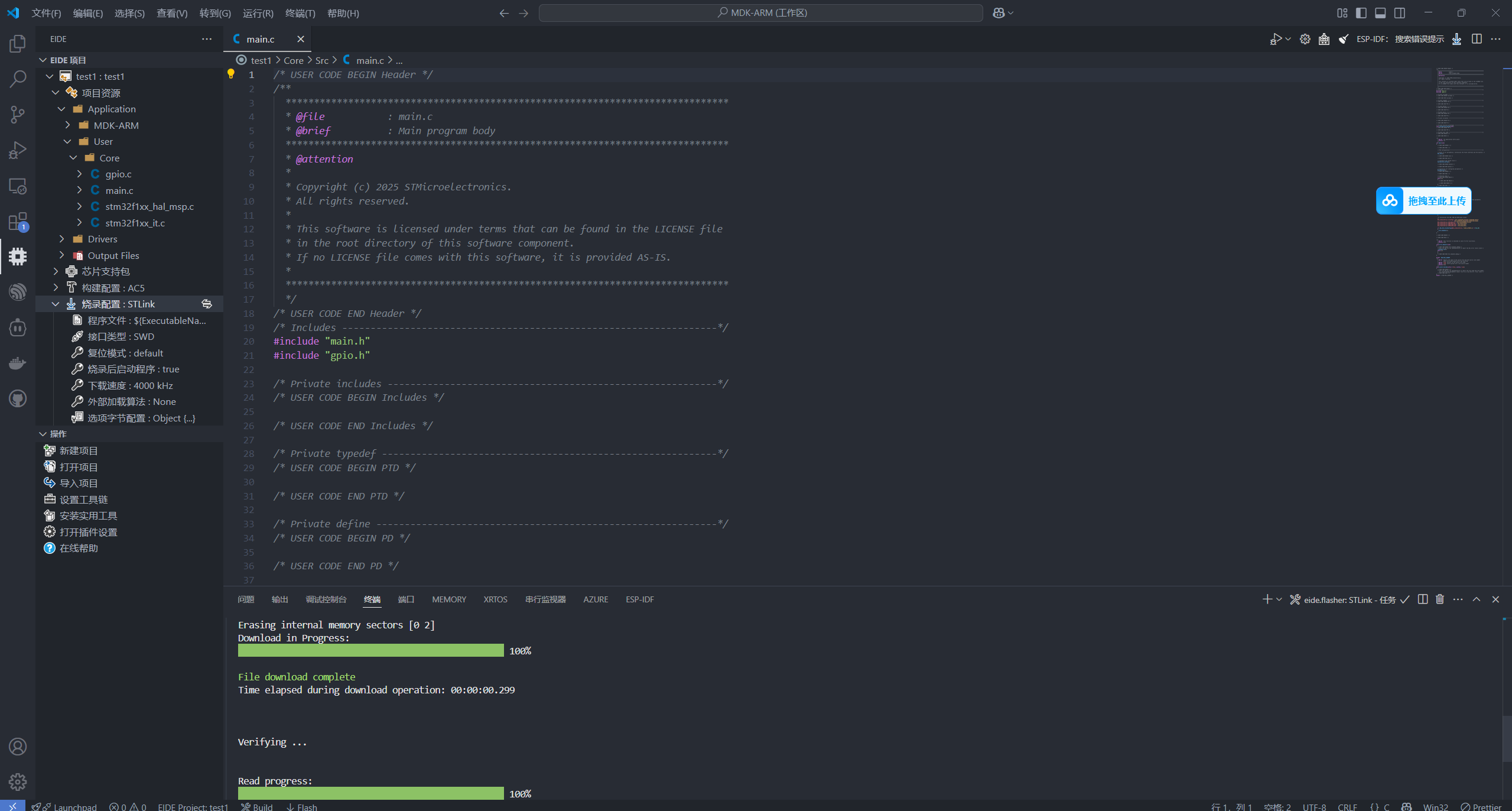

首先使用VSCode进行程序烧录测试

太好了!烧录成功

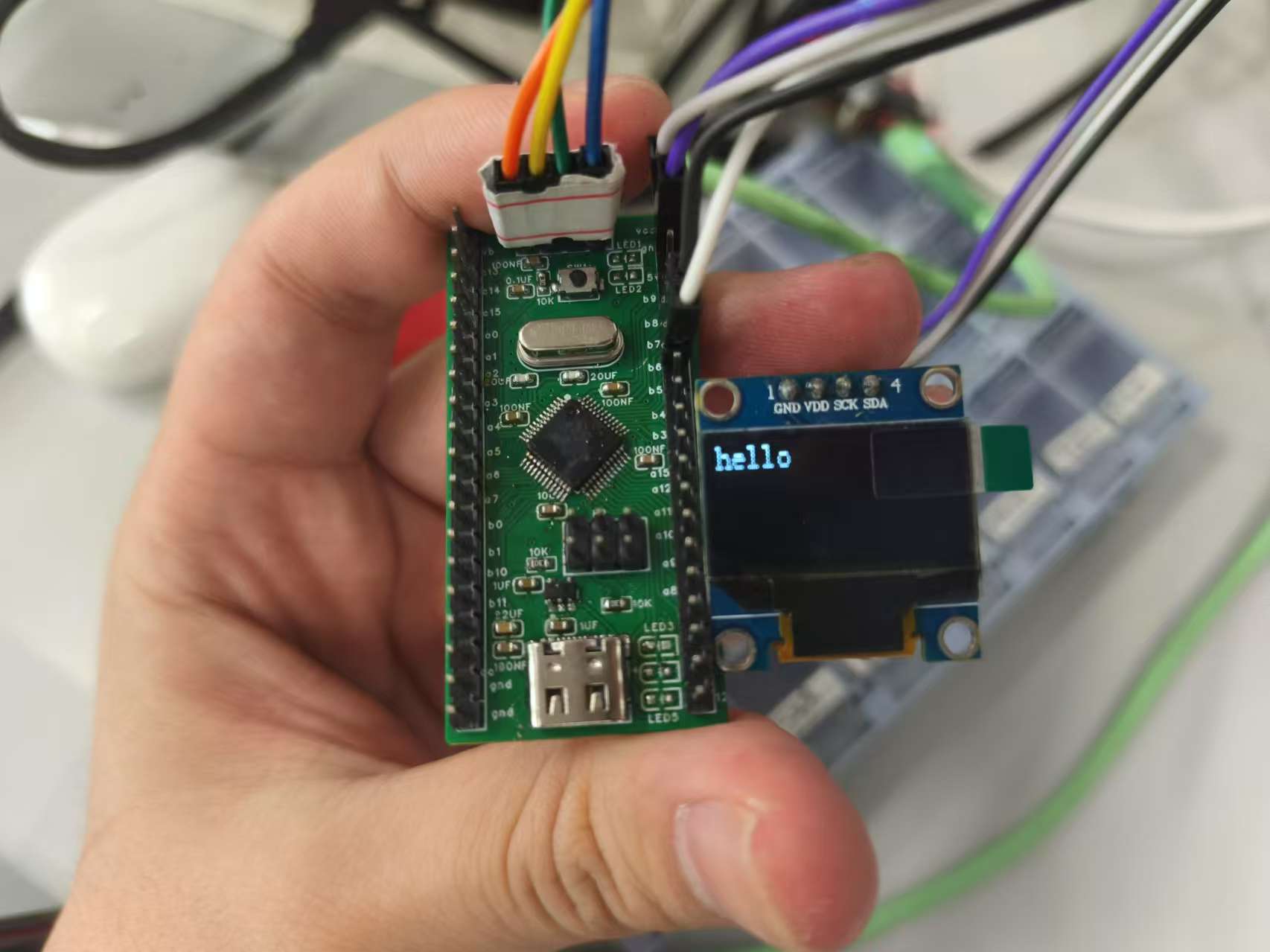

由于没有LED指示灯,改用OLED显示屏进行功能验证,编写简单的测试代码。

程序烧录运行。

显示功能正常!一板成,一次焊接通过,作为硬件设计的初次尝试,这个结果已经令人非常满意。唯一的遗憾是排针焊接方向搞反了。

总结与后续

本次硬件设计实践收获丰富,下一阶段将不再完全自主设计,而是学习优秀的开源方案。初学硬件设计时,参考成熟方案是更好的学习路径。

在嘉立创硬件开源平台发现了一个设计优秀的STM32最小核心板方案:

STM32F103CxT6开源方案

该方案集成了CH340串口芯片,便于串口调试;BOOT引脚采用按键设计,便于解决烧录异常问题;整体布局美观合理。计划基于此方案优化当前设计。