DC-DC电路的自举电容电路原理

在以往的电子产品设计中,我们经常会选型 DCDC 芯片,在选型过程中经常遇到有些DC-DC电路中需要用到自举电容,本文主要分析自举电容在DC-DC电路中的原理。

无论同步或者异步整流,经常会看到一个自举电容,常并联在DC-DC的LX和BS PIN脚之间,但是有也有无需自举电容的DC-DC。

这里以矽力杰的SY8113BADC和 SM8082A为例说明;

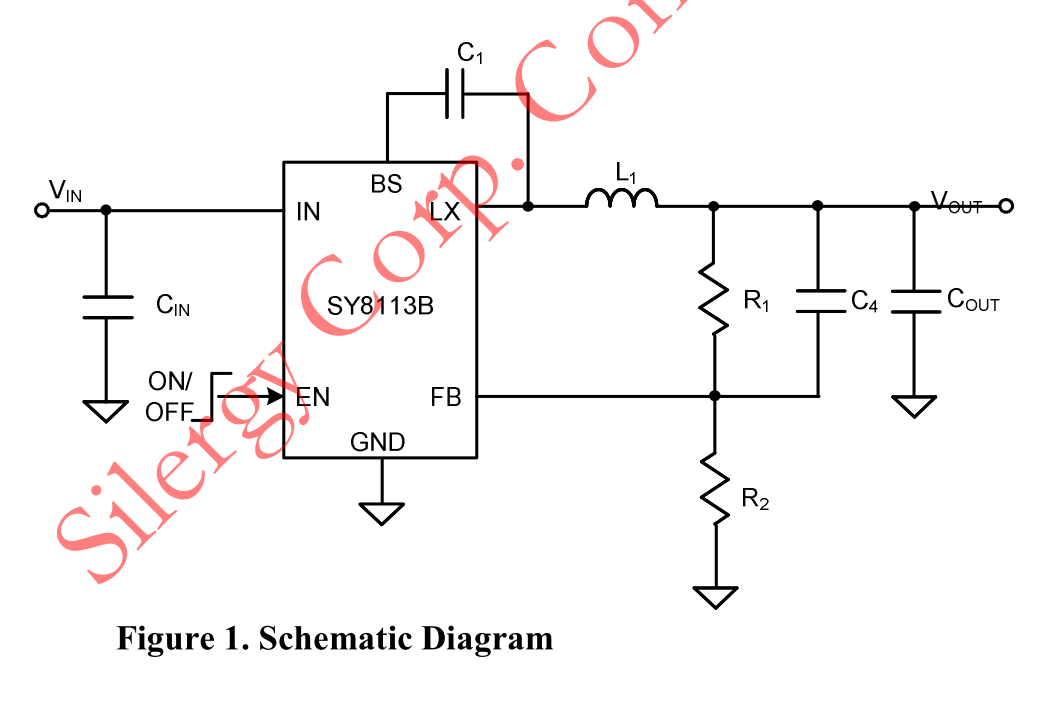

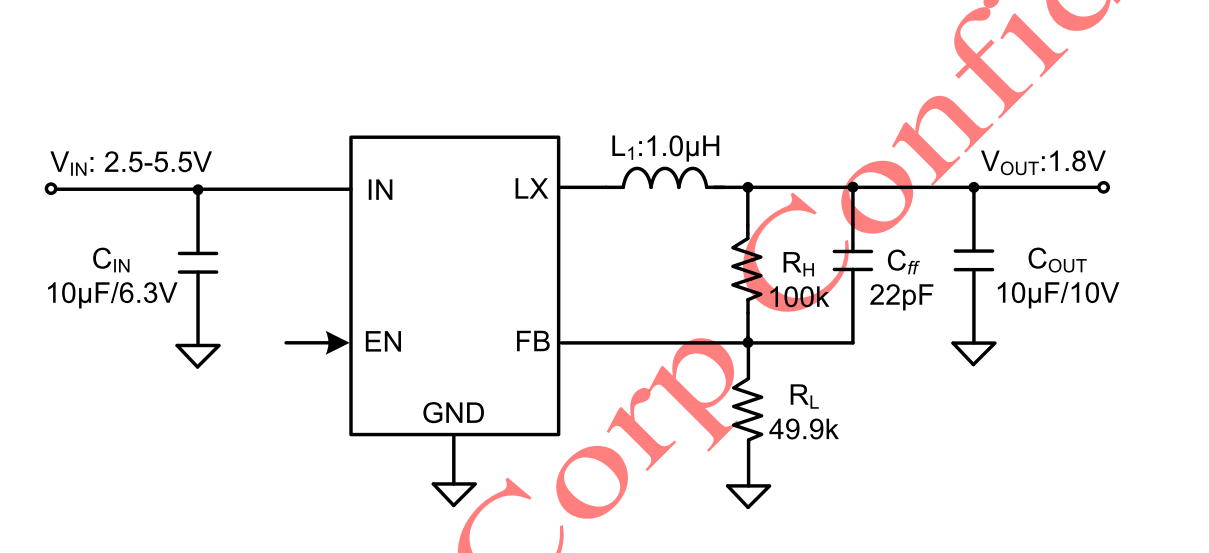

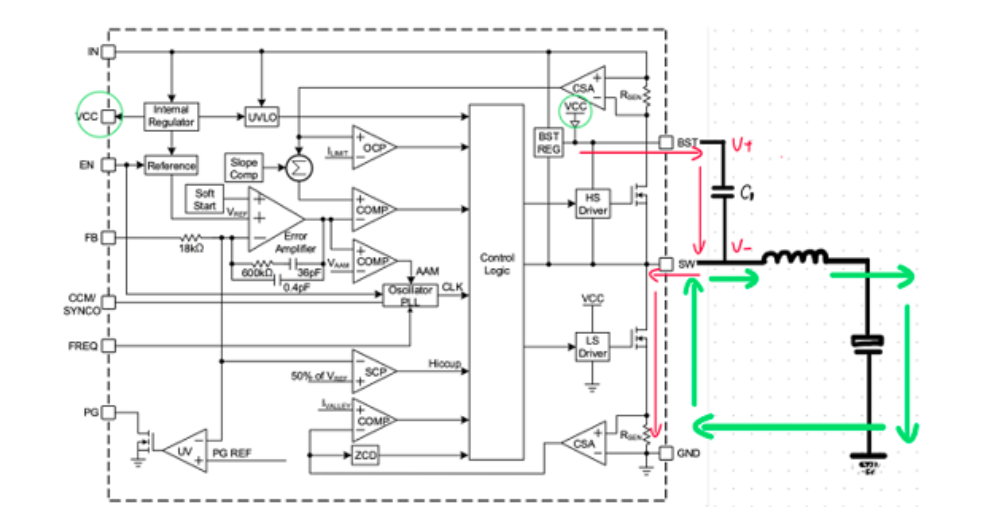

以SY8113BADC为基础的BUCK电路,需要自举电容,在BS和LX两个PIN脚之间并联的C1就是这个BUCK电路的自举电容

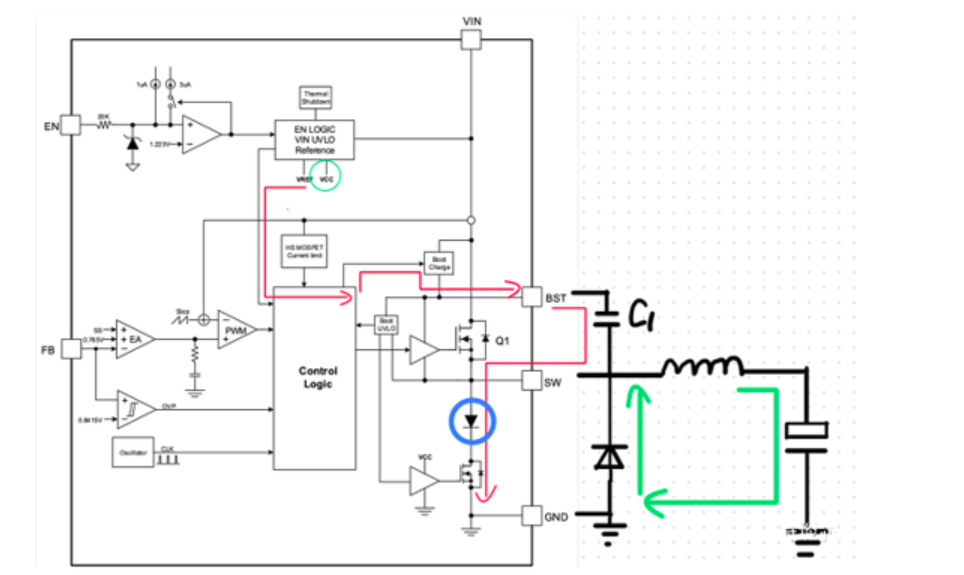

而SM8082A的BUCK电路中则没有用到自举电容;

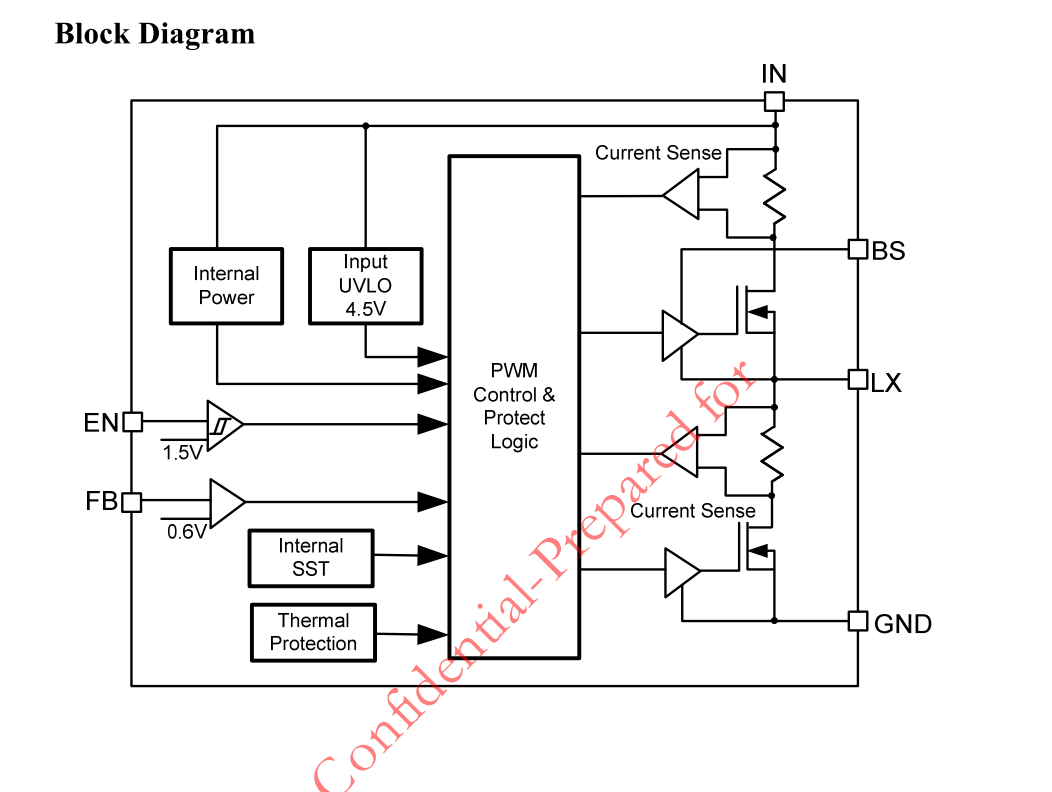

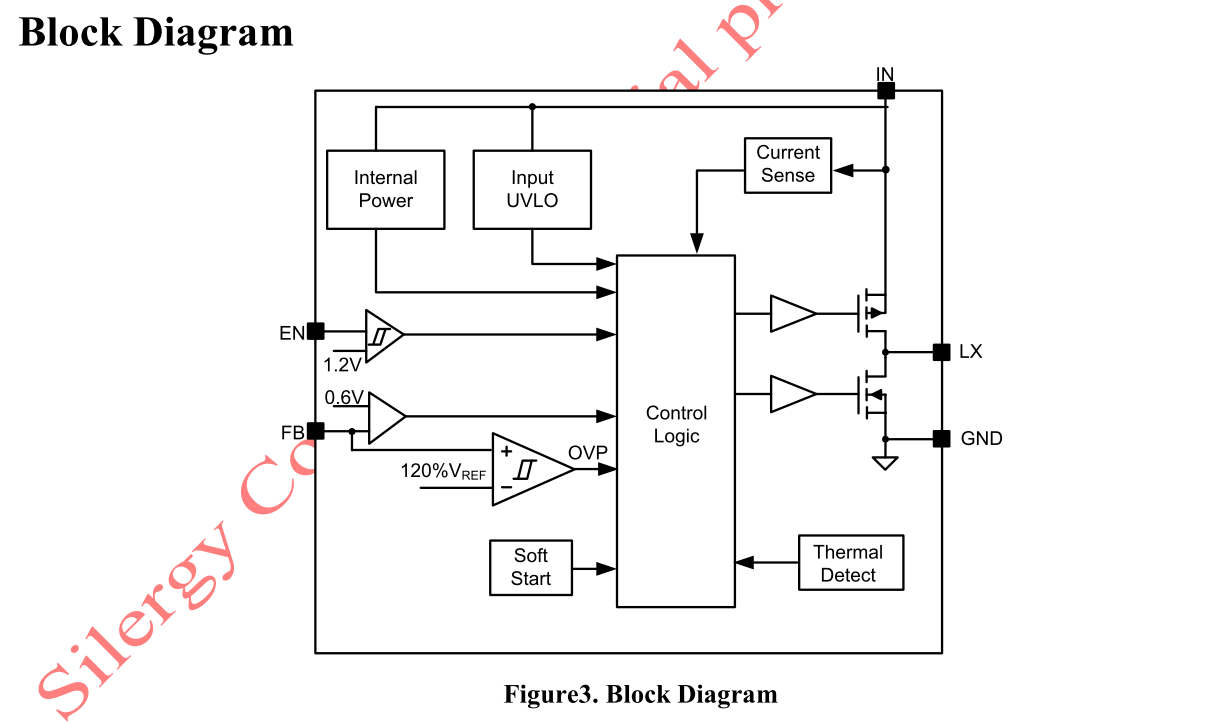

再比对一下二者的芯片内部框图:

SY8113内部的高边和低边MOS均是N沟通MOS管;

而SM8082A的内部高边MOS用的是P沟道MOS,低边用的是N沟通MOS;

相较发现:SY8113 内部高边MOS 为 NMOS,而 SM8082A的高边 MOS 为 PMOS

结论:自举电容的有无取决于芯片设计时采用的 MOS 管类型。

为什么有些用PMOS,有些用NMOS?

PMOS和NMOS由于其产品特性不同,各自的应用领域和使用方式也有所不同。

从器件本身来看:

PMOS的外延层是P型材料,多数载流子是空穴,

NMOS的外延层是N型材料,多数载流子是电子,

而电子的迁移率大概比空穴高2到3倍。因此在晶片面积相同的情况下,PMOS的导通电阻比NMOS高两到三倍。

具有相同导通电阻的PMOS晶片面积是NMOS的2到3倍,

这样PMOS的寄生参数如Qg等会比NMOS大,但是器件热阻比NMOS小。

此外,PMOS的跨导也比NMOS小,所以响应速度会更慢。

从 上述MOS 管的生产工艺我们知道,PMOS 的导通电流往往不会很大,而在同样的成本下,NMOS 的导通电流可以大很多,这意味着 Rdson 可以比较低。

因此很多DCDC的high-side mosfet都由PMOS换成了NMOS

同步DC-DC芯片内部的自举电路原理:

以下图的的同步DC-DC内部框图看一下自举电路;

框图中,两个绿色圆圈的 VCC 是 DC-DC 芯片内部稳压出来的一个既可以驱动 MOS 管开通的电压,同时也可以为芯片内部的其他逻辑电路供电。

Step1:

当低边 MOS 管被 LS Driver 导通后(这里因为是低边 NMOS,所以可以直接用 VCC 来驱动),VCC通过红色箭头所示的电路对自举电容进行充电,

并将自举电容两端的 V+、V-电压之间充电到 VCC 的电压。此时C1的上端V+是VCC,下端V-是GND,(忽略低边NMOS的内阻产生的压降)。

此时降压电路处于续流状态,因此绿色箭头表示电源输出与负载电路之间的续流回路。

Step2:

当导通完成后,低边 NMOS 将关闭,而高边 NMOS 将由 HS 驱动器打开,给后级电感充电;

此时高边MOS的S极是接在SW上,此时低边MOS也关断,这样就没了回路,

我们可以认为高边MOS的S极是悬浮在半空中。只是单纯的让G极输出高电平,并不能让高边MOS导通;

正是Cboot,将原本悬浮的HS Driver的两个电源端V+/V-(这里可以认为是NMOS的G极和S极)之间建立了(电位差)联系。这个电位差刚好是VCC

这里强调下:C1是并联在HS Driver的电源两端(V+/V-),并不是直接并联在高边MOS管的G和S两端。但HS Driver和MOS是共"参考点"。

此时可以认为高边MOS的Vgs=VCC。当Vgs>Vth此时,高边MOS导通。

高边MOS导通后,V-点电位突变为VCC,如果V+依旧保持VCC的电位,那Q1恐怕要被迫关闭了!

正是由于自举电容C1的存在,C1电容两端电压差不能突变V+点电位变为2VCC。

这样对C1而言,电压差依然是VCC。对HS Drvier而言,以SW点电位为参考,输出高电平时,Vgs依然是VCC,大于Vth,可以让高边MOS持续导通。

如果将 DC-DC 中的高边 NMOS 换成 PMOS,就不需要经过电容充电的麻烦,直接给出一个低于系统输入电压 VIN 的电压就可以使高端 PMOS 导通。

异步DC-DC的自举电路和同步相似,不同的是:由于异步 DCDC 没有低边 MOS 管,所以都是依靠外部设计一个肖特基二极管来续流所以芯片的内部设计还是有区别的。

我们可以看到异步 DC-DC 芯片在桥下侧设计了一个小 MOS 管,并且串联了一个二极管(蓝色圈出),之所以说这是一个小 MOS 管,是因为里面串联了一个二极管,在电流续流的过程中,大电流回路只会流过外部的肖特基二极管,而不会影响自举电容的充电回路。

红色箭头指向的电路是自举电容充电电路,这次我们了解一下,在异步 DC-DC 芯片中,工程师都是预置一个小 MOS 管来控制自举电容充电电路的。

因此在高端 MOS 采用 NMOS 的 DC-DC 芯片设计中,需要一个电路来起自举的作用,即产生一个高于系统输入电压的电压来导通高端 NMOS,而由于该电容尺寸较大,很难集成在 IC 中,所以大部分的 DC-DC 芯片都要求用户将自举电容放置在芯片的外部。

了解了自举电容的原理,其实对于自举电容的选择也能得心应手,手册上一般都会标注出来,对于内置功率MOS的DC-DC,它就是理论额定电压也就是 DCDC 芯片 VCC 的电压。

Reference list:

1.https://electronicspost.com/why-is-there-a-bootstrap-capacitor-in-all-dcdc-chip-designs/

2.https://blog.csdn.net/qq_21794157/article/details/123477257

3.https://blog.csdn.net/impossible1224/article/details/126606986