关于XILINX的XDC约束文件编写

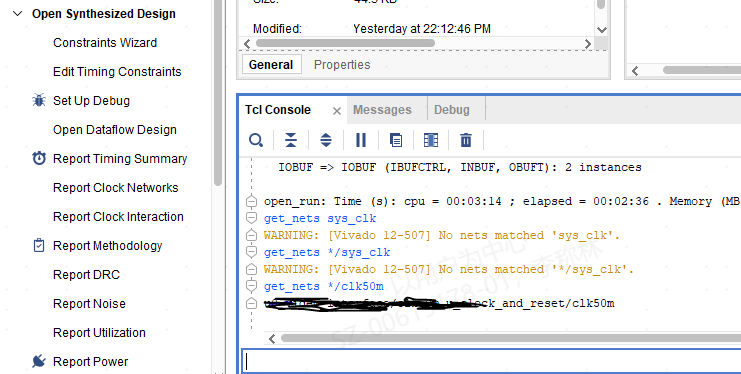

在vivado 打开对应的Open Synthesis 或者Open Implementation,在命令Tcl Console 输入对应的指令可以找到查找的结果内容。

在命令中,输入get_* pattern_name 找到对应的端口。

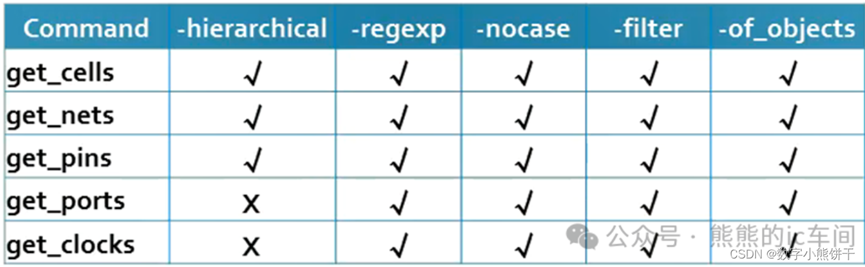

get_ports , 输入输出

get_cells 某个单元集合。

get_pins各类模块的引脚

get_pins pll_clk_inst/clinin

get_nets 网络线

get_clocks ,时钟约束一类的。 一下是后面的一些选型。

通过-hierarchical,可免于写具体的例化模块名称

-of_objects:用于在-of后面的结果中寻找匹配的对象

get_nets -of [get_cells a_reg]

-filter: 用于查找满足条件的对象

有如下选项:

可使用 directionin / directionout 选择端口输入输出不同方向的信号

还可以使用以下逻辑:

--等于 ==

--不等于 !=

--- 匹配 =~

--- 不匹配 !~

若有多个表达式,其返回值为bool类型时,支持逻辑操作:

---与 &&

---或 ||

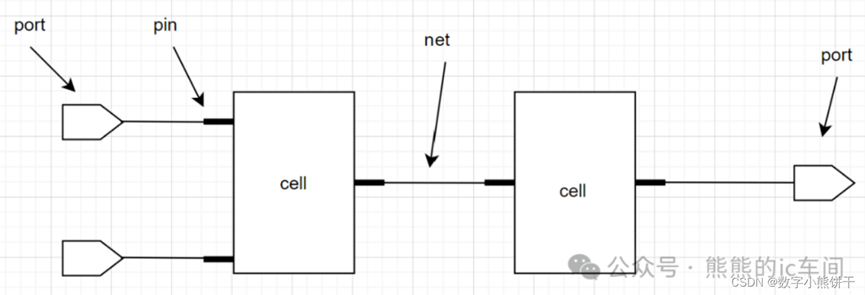

cell 是指的我们例化的模块,例如RAM、LUT、PLL、MMCM、还包括我们自己设计的模块和寄存器等等。

pin是指的每个cell的输入输出信号,比如模块的输入输出信号,寄存器的D端、C端和Q端,注意一下,如果是顶层模块的输入输出信号则不能使用pin定义。

port 顶层模块的输入输出信号,也是FPGA与外界通信的管脚。

net 是指pin与pin之间的连线。

clock当然就是指的我们所设置的时钟了。

操作如下图