PCB设计实践(十七)PCB设计时11个维度分析双层板和四层板该如何抉择

在PCB设计中,选择双层板(2层)还是四层板(4层)需综合考虑电路复杂度、性能需求、成本预算及生产周期等多方面因素。以下从11个维度进行深度对比分析,覆盖设计、性能、制造及实际应用场景。

一、基础结构对比

- 双层板结构

- 由顶层(Top Layer)和底层(Bottom Layer)两个信号层组成,中间为绝缘基材。

- 信号线通过通孔(Through Hole)实现层间连接,布线空间有限。

- 电源与地线需通过表层走线或大面积铺铜完成,易导致电源噪声和地弹问题。

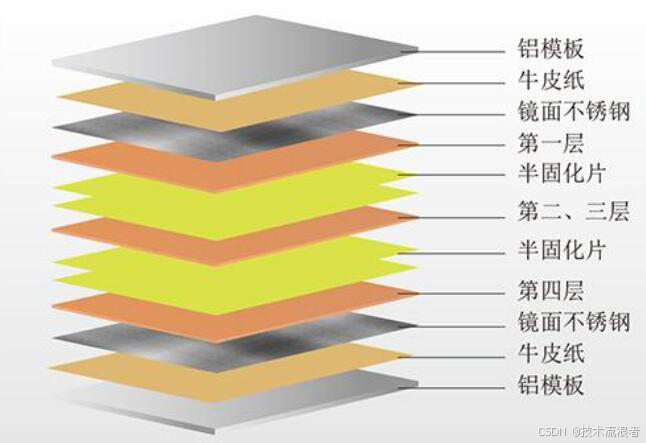

- 四层板结构

- 典型叠层为:顶层信号层(Top)、电源层(Power Plane)、地层(Ground Plane)、底层信号层(Bottom)。

- 通过埋孔(Buried Via)和盲孔(Blind Via)实现层间互联,布线空间提升3倍以上。

- 电源与地层采用完整铜面,形成低阻抗回路,显著提升电源稳定性。

二、信号完整性对比

- 双层板信号特性

- 信号线与电源/地线同层分布,易产生串扰(Crosstalk),尤其在高频(>100MHz)场景下噪声容限低。

- 回路阻抗较高,导致信号上升沿畸变,例如DDR3等高速接口难以满足时序要求。

- 典型案例:某消费级蓝牙耳机采用双层板,射频发射时误码率超标30%。

- 四层板信号优化

- 电源/地层作为参考平面,提供低阻抗回流路径,信号环路面积减少70%以上。

- 带状线(Stripline)布线占比提升,电磁辐射降低至双层板的1/5(实测数据)。

- 适用于PCIe Gen3、HDMI 2.0等高速协议,眼图张开度提升40%以上。

三、电磁兼容性(EMC)对比

- 双层板EMC挑战

- 无完整参考平面,信号线辐射超标风险高。FCC测试中常见30-300MHz频段超标。

- 电源噪声通过表层传导,导致整机传导发射(CE)测试失败率增加。

- 整改措施需增加磁珠、屏蔽罩等,单板成本上升15%-20%。

- 四层板EMC优势

- 电源/地层构成天然屏蔽层,辐射强度降低6-10dB(CISPR 25标准实测)。

- 地平面连续性保障共模噪声抑制,RE102测试通过率超95%。

- 汽车电子ECU模块采用四层板,EMC等级可达ISO 11452-2 Class 4。

四、电源完整性(PI)对比

- 双层板电源设计局限

- 电源网络依赖细线宽走线,动态负载下压降可达5%-8%。

- 去耦电容布局受限,高频去耦效果差,例如BGA封装CPU核心电压纹波超±5%。

- 典型案例:某工控主板因电源噪声导致DSP频繁复位。

- 四层板电源优化方案

- 独立电源层支持多电压域分割,压降控制在1%以内。

- 平面电容效应提供高频响应,0.1μF陶瓷电容数量减少50%仍满足纹波要求。

- 服务器主板通过四层板实现12V/5V/3.3V多级配电,转换效率提升至92%。

五、热管理能力对比

- 双层板散热瓶颈

- 发热元件(如MOSFET、PMIC)仅能通过表层铜箔散热,热阻高达60℃/W。

- 高功耗场景(>10W)需额外增加散热片,占用20%-30%布局空间。

- 工业级IGBT驱动板因散热不足导致MTBF降至5000小时。

- 四层板热传导增强

- 内层铜平面作为热扩散层,热阻降低至15-20℃/W。

- 埋铜技术(Embedded Copper)可将局部温度梯度缩小5℃-8℃。

- 5G基站AAU采用四层板,环境温度70℃时芯片结温控制在85℃以内。

六、布线密度与复杂度

- 双层板布线局限

- BGA封装器件(如FPGA)出线率不足60%,需采用盘中孔(Via in Pad)增加成本。

- 差分对长度匹配误差超±50mil,影响USB 3.0等接口信号质量。

- 某物联网网关因布线拥挤导致量产良率仅75%。

- 四层板布线灵活性

- 信号层与电源/地层分离,BGA出线率提升至90%以上。

- 内层支持蛇形线(Serpentine)等精密布线技术,延时匹配精度达±5ps。

- 高端显卡PCB实现16000+节点布线,良率维持98%以上。

七、成本构成分析

| 成本项 | 双层板 | 四层板 | 差异幅度 |

|---|---|---|---|

| 基板材料 | FR-4标准板($5/m²) | 高TG材料($8/m²) | +60% |

| 钻孔工艺 | 通孔($0.01/孔) | 盲埋孔($0.03/孔) | +200% |

| 压合次数 | 1次($10/㎡) | 2次($25/㎡) | +150% |

| 良率损失 | 8%-12% | 5%-8% | -35% |

八、典型应用场景

- 优先选择双层板的场景

- 消费电子:LED照明控制器、小家电控制板(成本敏感型)。

- 低频电路:温湿度传感器、继电器驱动电路(<10MHz)。

- 原型验证:硬件功能验证阶段快速迭代。

- 必须采用四层板的场景

- 高速数字电路:千兆以太网、DDR4内存接口(>1Gbps)。

- 射频模块:5G毫米波天线、Wi-Fi 6E射频前端。

- 高可靠性设备:医疗CT控制板、航天器导航模块。

九、设计工具差异

- 双层板设计要点

- 采用Altium Designer基础功能即可完成布线。

- 手动优化电源环路,推荐铺铜宽度≥40mil。

- 典型设计周期:3-5人日。

- 四层板设计进阶

- 需使用Cadence Allegro SI/PI模块进行叠层仿真。

- 电源完整性工具(如ANSYS SIwave)确保平面谐振频率>1GHz。

- 典型设计周期:10-15人日。

十、生产工艺对比

- 双层板工艺流程

〖开料→钻孔→沉铜→图形转移→蚀刻→阻焊→表面处理〗

- 关键控制点:蚀刻因子>3.0,确保线宽公差±10%。

- 四层板核心工艺

〖内层制作→层压→激光钻孔→填孔电镀→外层图形〗

- 难点:层间对准精度<25μm,介质层厚度均匀性±5%。

十一、未来趋势

- 消费电子:双层板仍占主流(2025年占比65%),但HDI技术推动四层板渗透率提升。

- 工业与汽车:四层板需求年增18%(Yole数据),新能源电控单元(ECU)成增长引擎。

总结

在满足功能需求的前提下,双层板凭借成本优势仍是简单电路的首选。但对于涉及高速信号、严苛EMC要求或高功率密度的设计,四层板在性能、可靠性和扩展性方面具有不可替代性。建议工程师在项目初期通过SI/PI仿真量化需求,结合量产规模制定最优方案。