运算放大器版图设计与后仿真实战指南

运算放大器版图和后仿

实验报告:反相放大器版图与后仿流程

实验目的

-

掌握运算放大器版图设计的基本操作,包括器件布局、金属连线、衬底连接及DRC检查。

-

理解寄生参数抽取(PEX)与后仿流程,分析寄生效应(如电阻、电容)对电路性能的影响。

-

学习如何通过版图设计优化电路性能,并验证仿真结果的准确性。

-

进行后防,要求其性能指标:

-

增益 > 60dB

-

GBW > 100MHz

-

相位裕度 > 60度

-

负载电容 10pF

实验内容

-

版图设计:基于运算放大器原理图,完成版图绘制,包括器件放置、金属连线、衬底连接及DRC检查。

-

寄生参数抽取与后仿:基于已完成的版图,提取寄生参数并进行后仿分析,对比前仿与后仿结果差异。

实验步骤与结果

一、版图设计步骤

-

打开版图界面

- 在原理图界面点击“Layout XL”,进入版图编辑环境。

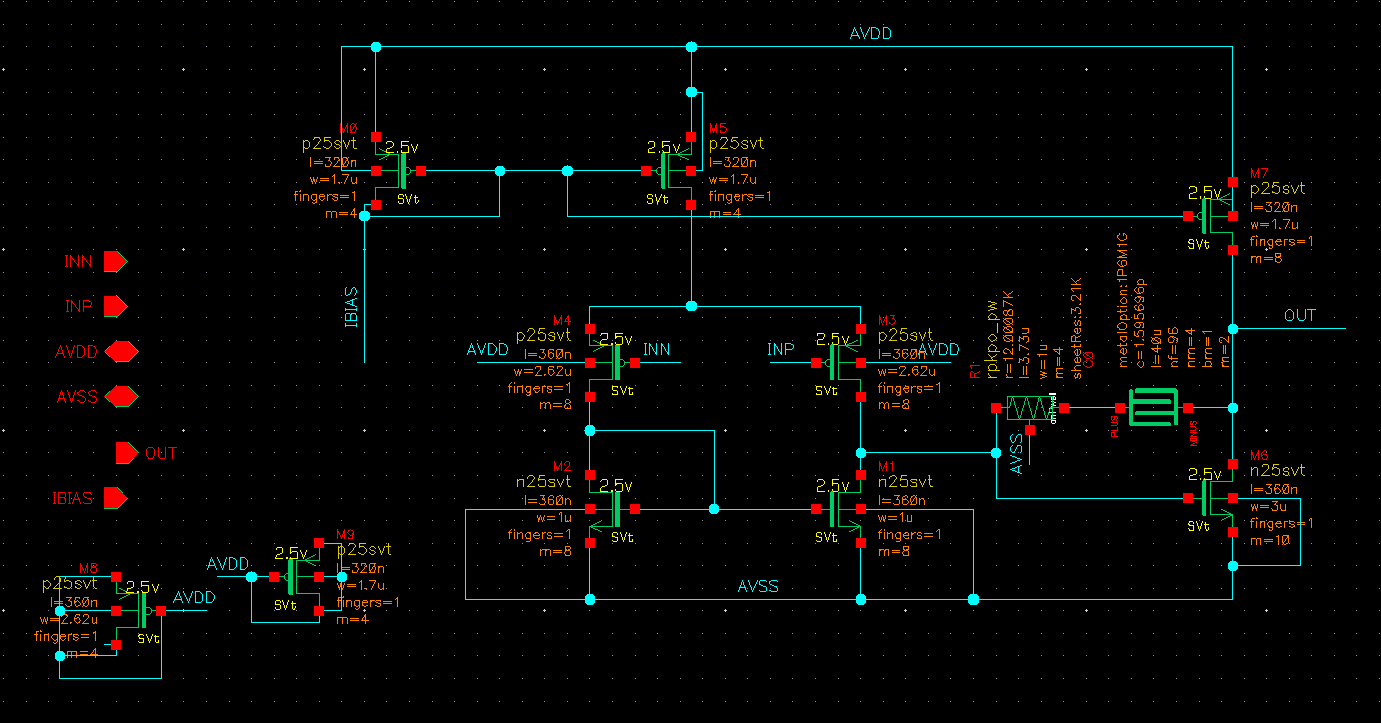

运算放大器原理图

使用器件

| 器件编号 | 器件类型 | 长(nm) | 宽(um) | 栅指数 | 乘积数 |

|---|---|---|---|---|---|

| M0 | p25svt | 320 | 1.7 | 1 | 4 |

| M1 | n25svt | 360 | 1 | 1 | 8 |

| M2 | n25svt | 360 | 1 | 1 | 8 |

| M3 | p25svt | 360 | 2.62 | 1 | 8 |

| M4 | p25svt | 360 | 2.62 | 1 | 8 |

| M5 | p25svt | 320 | 1.7 | 1 | 4 |

| M6 | n25svt | 360 | 3 | 1 | 10 |

| M7 | p25svt | 320 | 1.7 | 1 | 8 |

| M8 | p25svt | 360 | 2.62 | 1 | 4 |

| M9 | p25svt | 320 | 1.7 | 1 | 4 |

| 器件编号 | 器件类型 | 数值 | 乘积数 |

|---|---|---|---|

| R0 | rpkp0_pw | 12.379KΩ | 4 |

| C0 | cmomsy | 1.595pF | 2 |

-

使用快捷键

Shift + F显示全部图层,并通过快捷键e设置网格间距为 0.005(避免DRC报错)。 -

器件放置与连线

-

插入MOS管等器件(快捷键

i),调整位置后按需求连接。 -

金属连线规则:

-

输入/输出采用 laa 和 lab 金属层(避免短路),并通过通孔(快捷键

o)实现层间连接。 -

例如:

-

VIN用

laa连线,VOUT用lab连线,通过lab→laa的通孔连接。 -

NMOS衬底连接GND(

laa→P_well),PMOS衬底连接VDD(laa→N_well)。

-

-

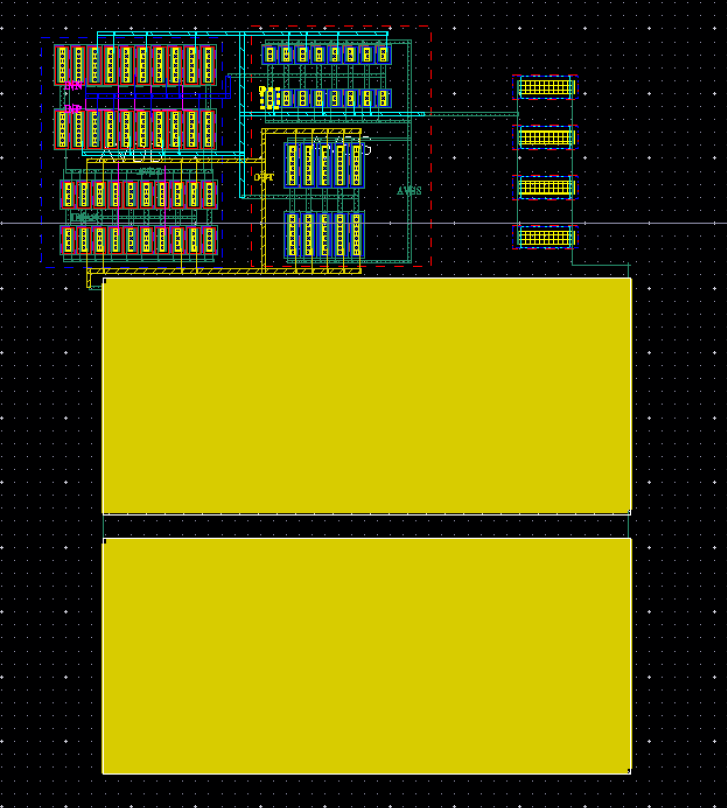

运算放大器版图的绘制

- DRC检查

- 使用 DRC工具 检查版图设计规则(如层间距、短路等)。

版图DRC检查

利用文档手册,逐步排查DRC报错,留下只剩den类型的报错即可和sg报错(一个是版图密度问题和版图面积问题)

-

注意:需调用独立的

drcrunset文件(路径示例:/home/用户名/PV/RUNSET/imcsdrcrunset),避免文件冲突。 -

保存与验证

-

完成版图后,确保无DRC错误,保存文件。

- LVS检查

-

使用LVS工具检查版图存在的问题

-

注意:需调用独立的

drcrunset文件,避免文件冲突。 -

保存与验证

-

完成版图后,确保无LVS错误,保存文件。

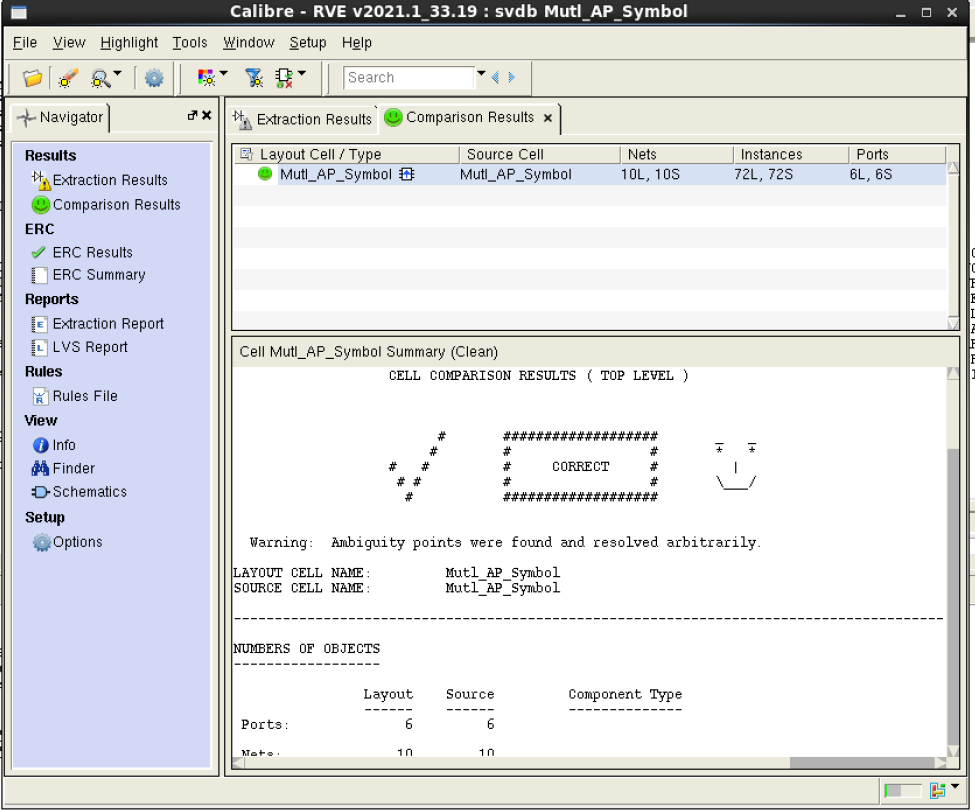

版图LVS检查

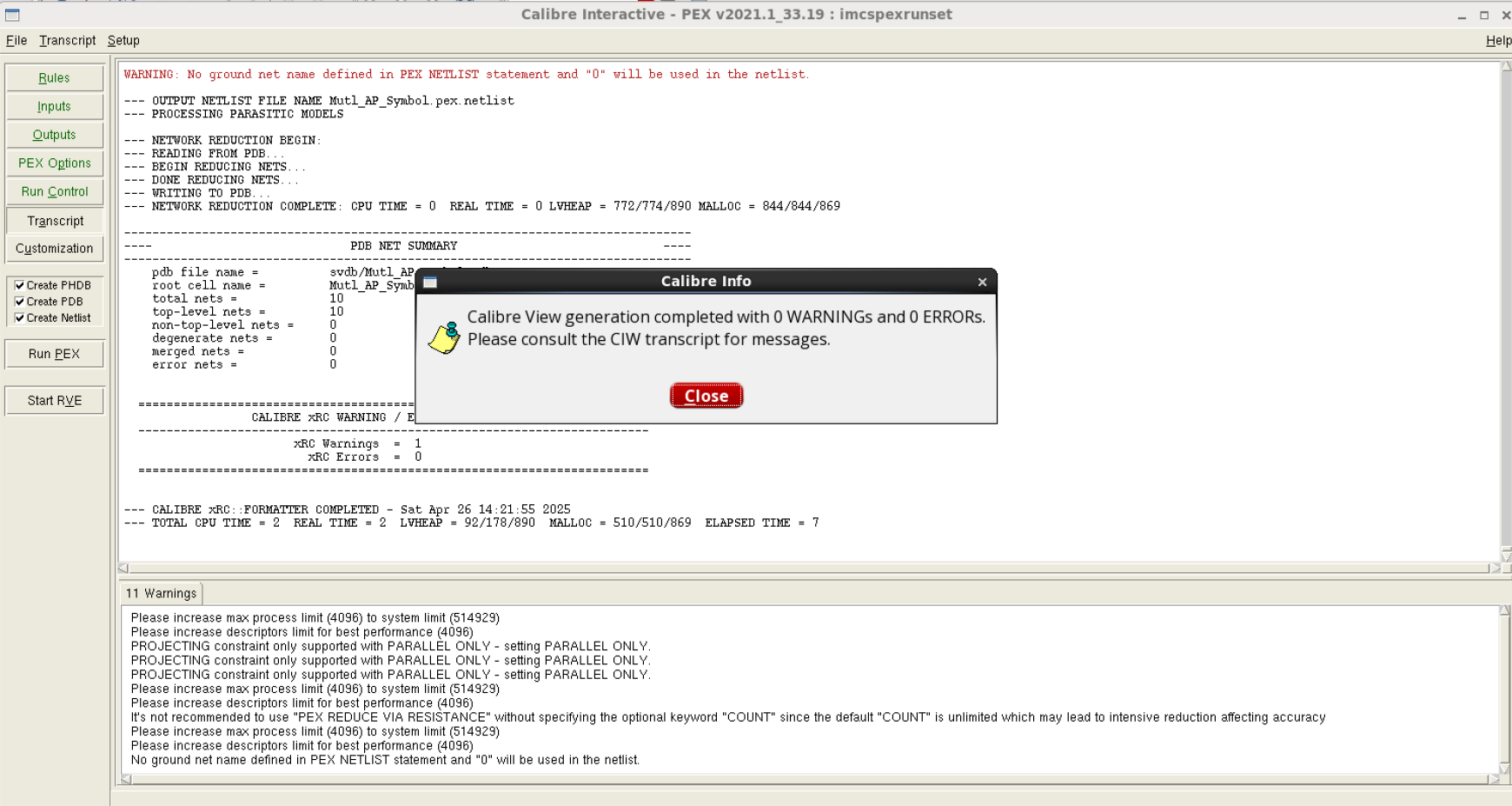

二、寄生参数抽取与后仿流程

- PEX抽取

-

打开原理图界面,点击 Run PEX 图标,设置路径与规则文件至个人文件夹。

-

选择 xrc工具,配置抽取参数(如cellmap文件路径、calibreview名称需唯一)。

PEX提取成功信息

-

关键步骤:

-

红框内需手动修改

cellmap文件路径和calibreview名称(避免覆盖)。- 蓝框参数保持默认,确保 LVS已通过(否则寄生参数错误)。

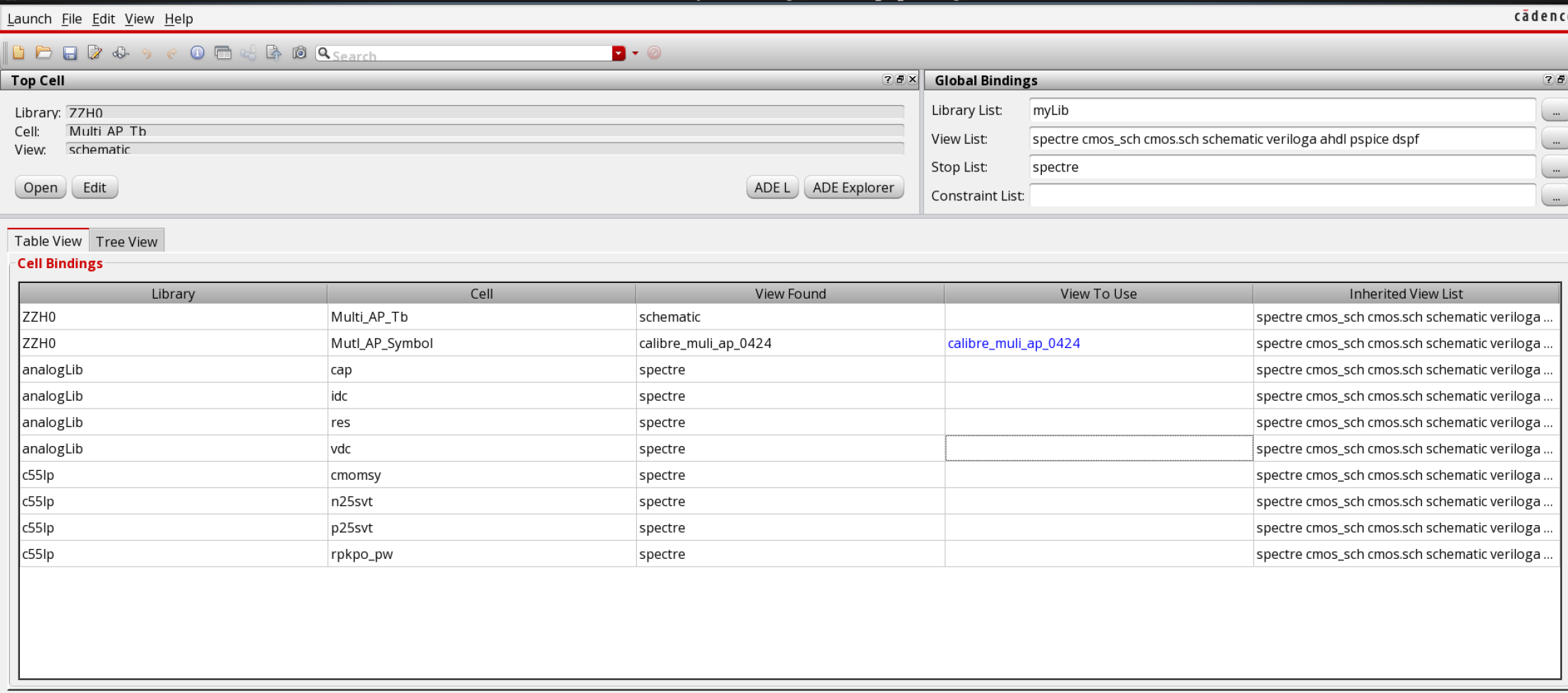

- 后仿配置

-

在TESTBENCH单元中新建 config 子单元,设置顶层单元(Top Cell)的视图为 schematic。

-

选择 spectre 仿真器,同步配置后进入原理图界面。

-

右键点击需仿真的单元,选择刚生成的 calibreview 文件。

后仿配置,导入寄生参数

- 运行仿真

-

确认配置无误后,执行

ade xl运行仿真。 -

结果对比:后仿结果可能因寄生参数(如互连线电容、接触电阻)与前仿存在差异,需分析具体原因(如版图布局不合理导致寄生过大)。

仿真点设置

| 信号 | 工作条件 |

|---|---|

| AVDD | 2.5V |

| AVSS | 0V |

| VDC | 1.25V |

| IBIAS | 190uA |

| AC | 1V |

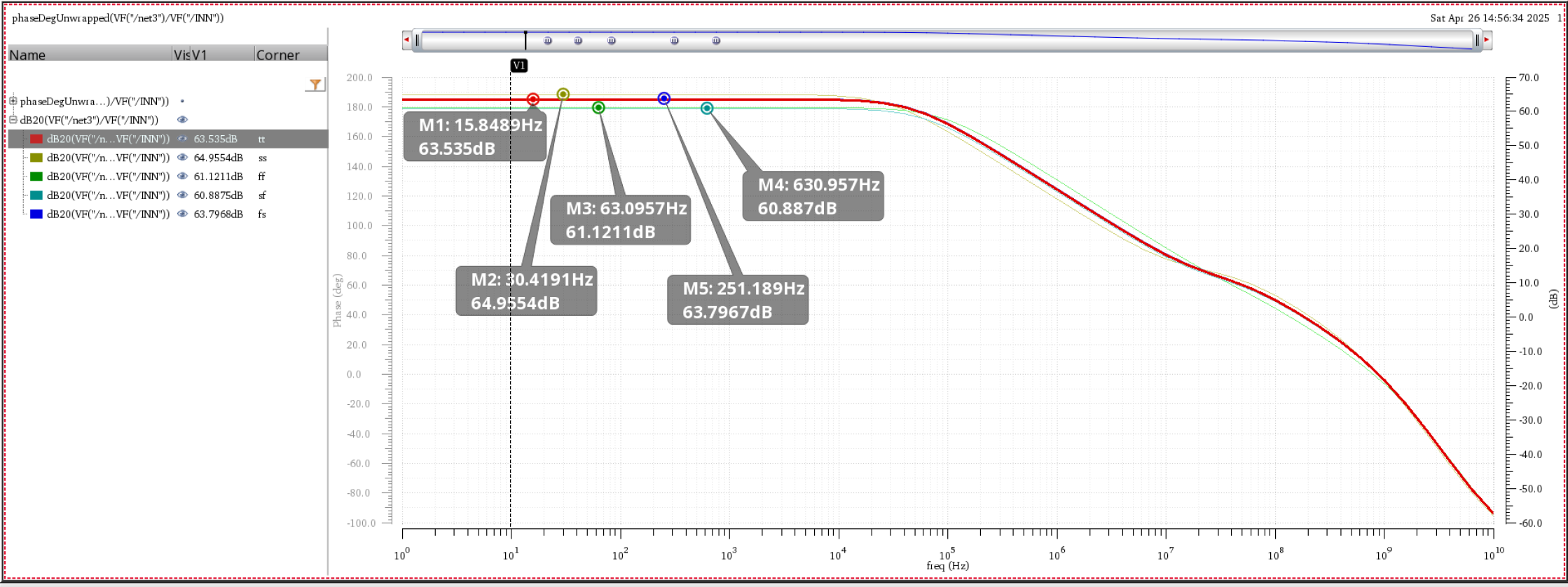

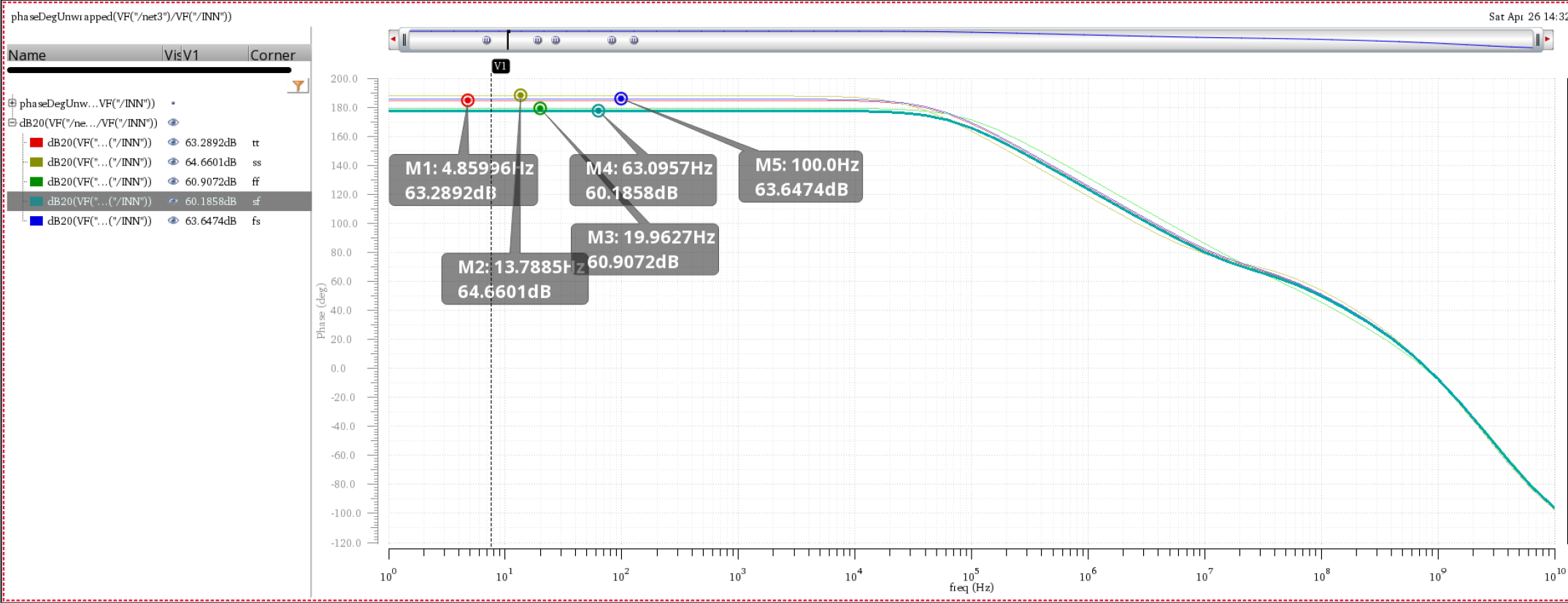

前仿不同工艺角下,AC低频增益曲线

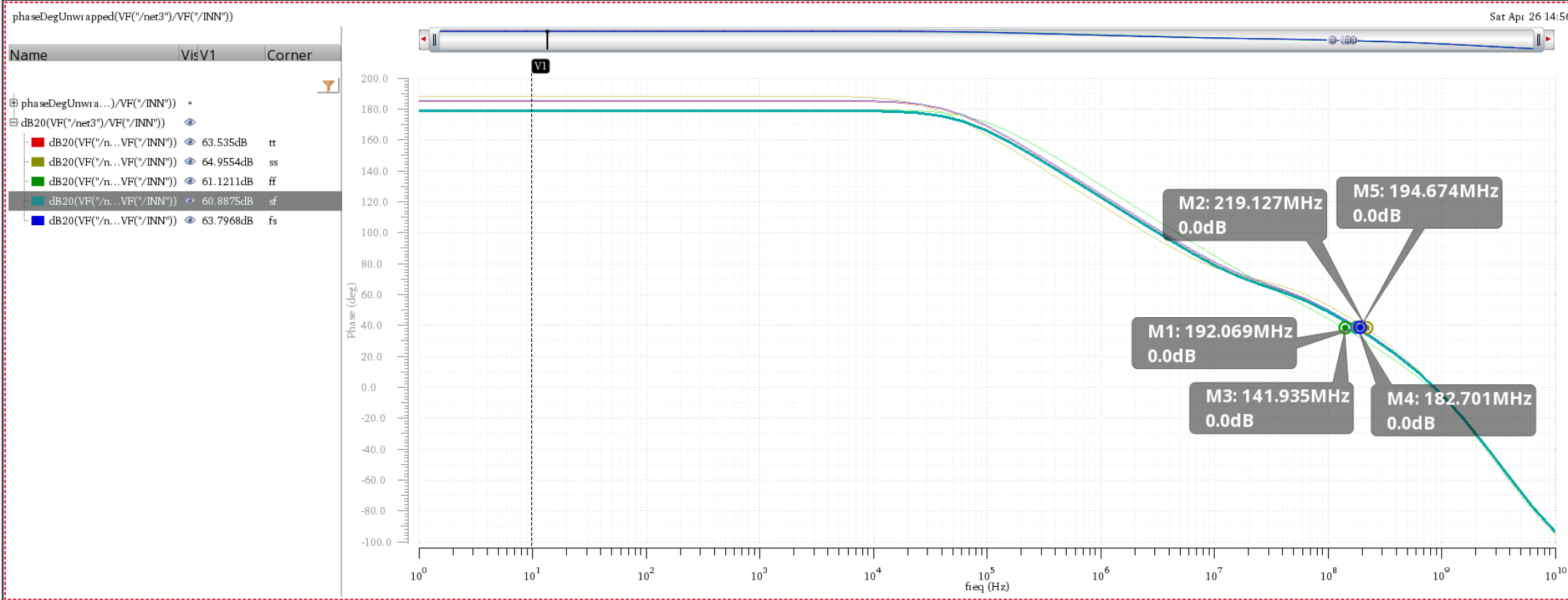

前仿不同工艺角下,AC单位带宽增益(GBW)

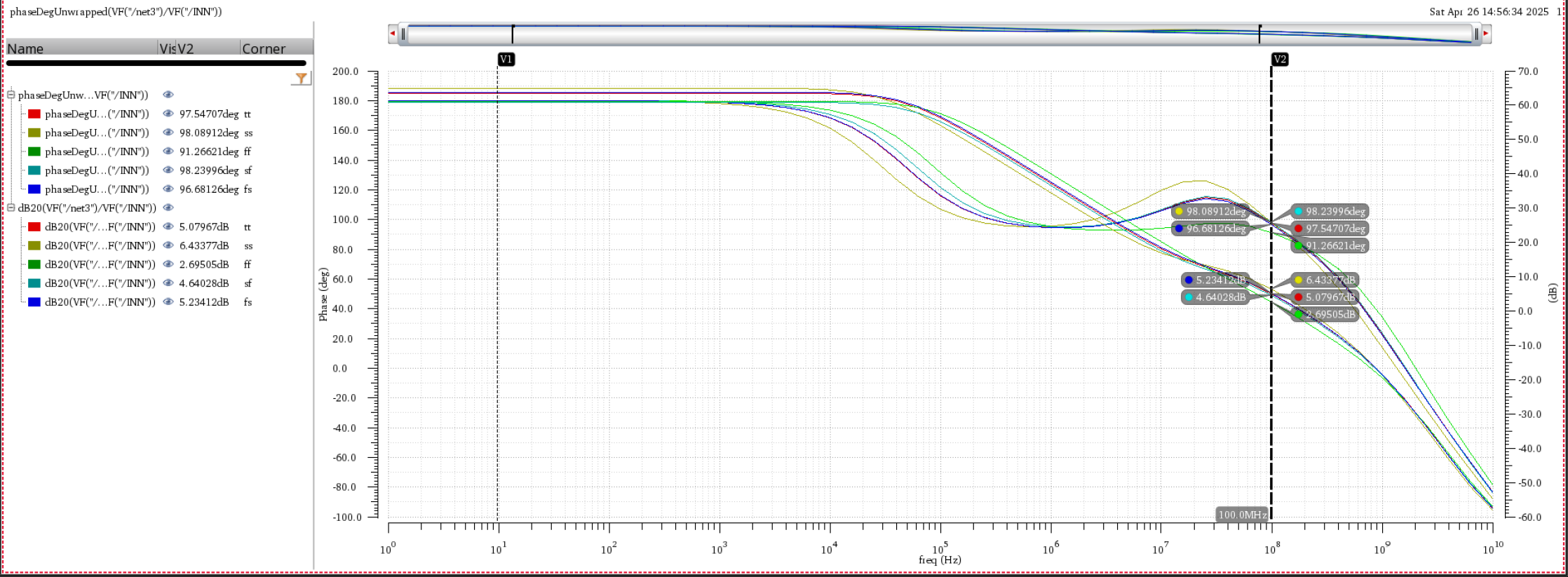

前仿不同工艺角下, 相位裕度

注:因为多张图片重叠在一起无法辨析,因而这里采用100MHz的相位偏移,而下表中采用相位裕度是根据不同工艺角下,相位在单位增益频率下的偏移

| 工艺角 | 低频增益(dB) | GBW(MHz) | 相位裕度(deg) |

|---|---|---|---|

| tt | 63.535 | 192.07 | 82.97 |

| ss | 64.955 | 219.13 | 75.87 |

| ff | 61.121 | 141.34 | 83.93 |

| fs | 60.8875 | 182.70 | 84.73 |

| sf | 63.797 | 194.67 | 81.93 |

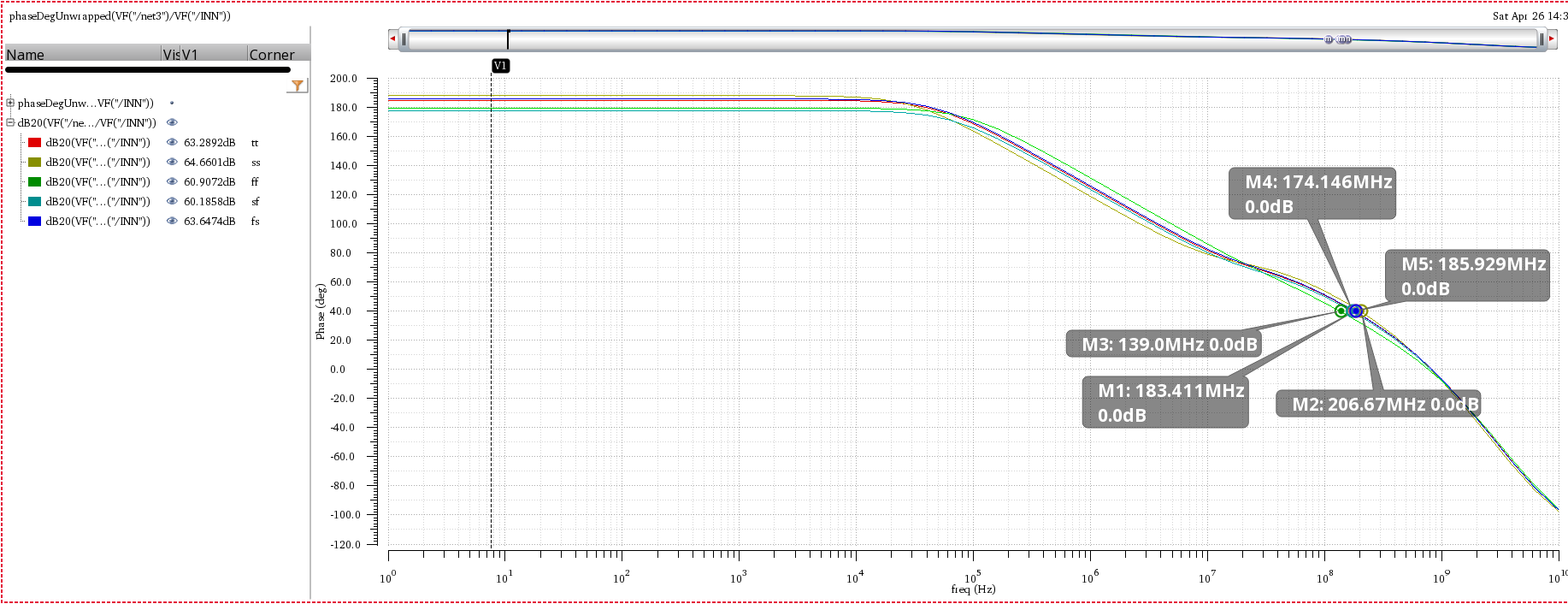

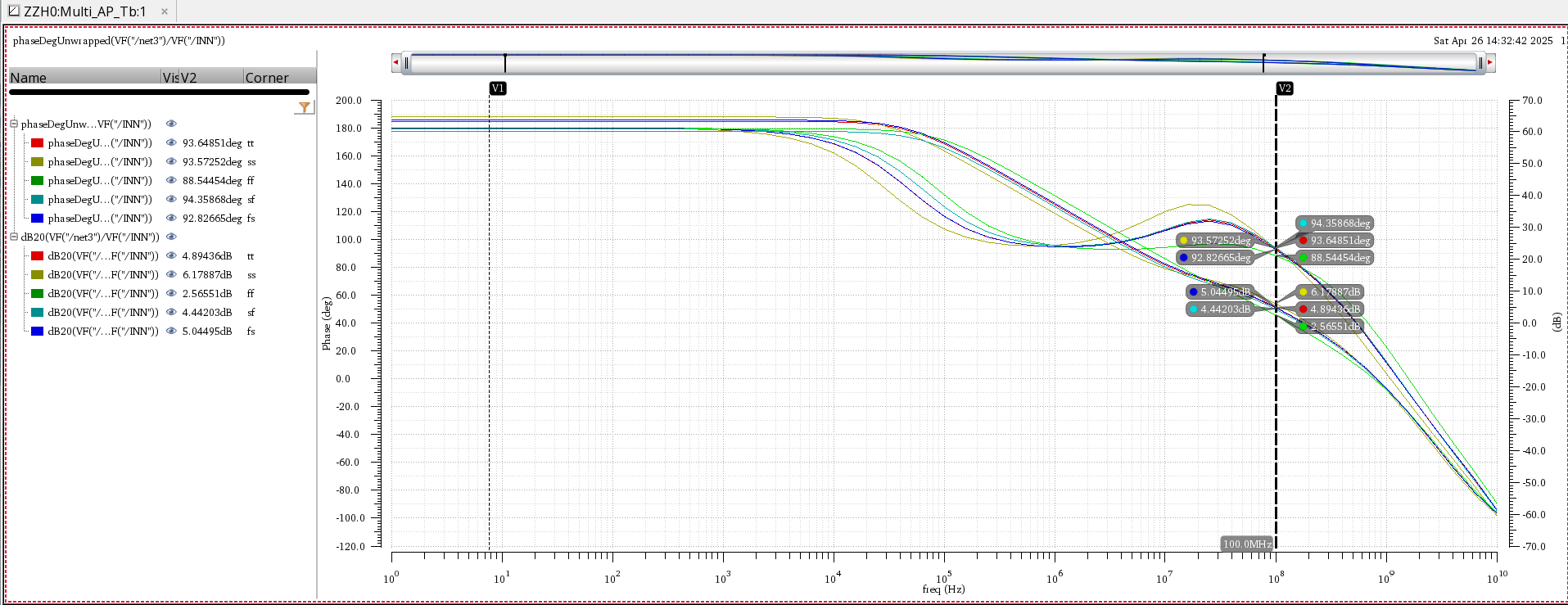

后仿不同工艺角下,AC低频增益曲线

后仿不同工艺角下,AC单位带宽增益(GBW)

后仿不同工艺角下, 相位裕度

注:同前仿一致

| 工艺角 | 低频增益(dB) | GBW(MHz) | 相位裕度(deg) |

|---|---|---|---|

| tt | 63.238 | 183.41 | 78.71 |

| ss | 64.660 | 206.67 | 71.53 |

| ff | 60.907 | 139.0 | 83.90 |

| fs | 60.185 | 174.15 | 80.62 |

| sf | 63.647 | 185.929 | 77.68 |

通过对比,可以看有下表 (后仿-前仿)

| 工艺角 | Δ低频增益(dB) | ΔGBW(MHz) | Δ相位裕度(deg) |

|---|---|---|---|

| tt | -0.297 | -8.66 | -4.26 |

| ss | -0.295 | -12.46 | -4.52 |

| ff | -0.214 | -2.34 | -0.03 |

| fs | -0.7025 | -8.55 | -4.11 |

| sf | -0.15 | -8.741 | -4.25 |

由于后仿考虑版图还有金属线的的寄生参数影响,增益均出现下降,而单位带宽增益和相位裕度均出现了增加,其中ff工艺角前后变化最小,具有较强的稳定性。

综合评价运算放大器性能

综合评价一个运算放大器的性能,需要:

- 核对关键指标: 检查增益、GBW、相位裕度等核心指标是否在目标负载和所有工艺角下都满足设计要求

开环增益 (Open-Loop Gain): 衡量放大器放大能力的核心指标。

实验目标**😗* > 60 dB

实验结果 (后仿): 在不同工艺角下,低频增益在 60.185 dB 到 64.660 dB 之间。

评价**😗* 所有工艺角下的后仿结果均满足 > 60 dB 的设计目标。ss角增益最高,fs角最低。

增益带宽积 (Gain-Bandwidth Product, GBW): 反映了放大器在高频下的性能,决定了在特定闭环增益下可获得的最大带宽。

实验目标**😗* > 100 MHz

实验结果 (后仿): 在不同工艺角下,GBW 在 139.0 MHz 到 206.67 MHz 之间。

评价**😗* 所有工艺角下的后仿结果均远超 > 100 MHz 的设计目标。ss角GBW最高,ff角最低。

相位裕度 (Phase Margin, PM): 衡量放大器稳定性的关键指标。相位裕度越大,系统瞬态响应越好,越不容易振荡。

实验目标**😗* > 60 度

实验结果 (后仿): 在不同工艺角下,相位裕度在 71.53 度 到 83.90 度 之间。

评价**😗* 所有工艺角下的后仿结果均满足 > 60 度的设计目标,表明该运算放大器在指定负载 (CL=10pF) 下具有良好的稳定性。ff角相位裕度最大,ss角最小(但仍远大于60度)。

负载能力: 在 CL=10pF 的负载条件下进行评估。评价性能时必须考虑此负载,因为负载会影响GBW和PM。实验结果表明在此负载下性能达标。

- 评估寄生效应: 通过对比前仿和后仿结果,量化版图寄生参数对性能(通常是负面影响,如降低增益、GBW、PM)的影响程度。

增益: 后仿增益普遍略低于前仿增益。这是因为寄生电阻(如金属线电阻、接触电阻)会产生额外的电压降,寄生电容(如线间电容、对地电容)可能改变电路的偏置点或轻微影响输出阻抗,导致增益下降。

GBW: 后仿GBW普遍低于前仿GBW。寄生电容(尤其是连接到高阻节点的电容)会增加电路的极点频率,特别是降低非主极点的频率,或者轻微影响主极点,通常导致GBW下降。

相位裕度: 后仿相位裕度普遍低于前仿相位裕度(寄生电容引入的额外极点会在高频处引入额外的相位滞后,从而在单位增益频率处降低相位裕度

评价:前后仿性能指标的变化幅度可以反映版图寄生效应的大小。ff角的性能变化最小,说明在该工艺角下,寄生效应相对影响较小,或者说前仿模型在该角下与包含寄生的后仿模型符合度更高。fs角增益变化最大。虽然所有指标在后仿中均有下降,但它们仍然满足设计要求,这表明的版图设计是成功的,寄生效应的影响在可接受范围内

- 考察稳健性: 分析在不同工艺角下性能的变化范围,确保最差情况仍满足指标要求。

实验结果分析: 实验覆盖了tt (typical-typical), ff, ss, fs, sf 五个主要工艺角。增益、GBW、PM在不同工艺角下有明显波动。例如,GBW在ff角最低(139 MHz),在ss角最高(206.67 MHz),相差近50%。

评价: 综合评价需要看最差情况(Worst Case)是否满足要求。在您的实验中,所有工艺角下的后仿结果都满足了增益、GBW和相位裕度的最低要求。这表明该运放设计具有较好的工艺稳健性

- 考虑其他应用相关指标: 根据具体应用场景,还需评估SR, CMRR, PSRR, Offset, 功耗, 输出摆幅, 噪声等其他重要性能。

压摆率 (Slew Rate, SR): 衡量放大器对大信号阶跃输入的响应速度。

共模抑制比 (Common-Mode Rejection Ratio, CMRR): 衡量放大器抑制共模信号的能力。

电源抑制比 (Power Supply Rejection Ratio, PSRR): 衡量放大器抑制电源电压波动的能力。

输入失调电压 (Input Offset Voltage): 衡量差分输入端需要加多大的电压才能使输出为零,影响DC精度。

功耗 (Power Consumption): 总的静态和动态功耗。

输出电压摆幅 (Output Voltage Swing): 输出电压能达到的最大和最小值。

噪声性能 (Noise): 输入参考噪声电压和电流

注意要点

- 版图设计对性能的影响:

-

金属层选择:不同层的电路需要用不同的金属连线

-

衬底连接:NMOS接P衬底,PMOS接N衬底。若未连接,器件可能失效或引入寄生路径。

- 寄生参数的作用:

-

寄生电阻

- 增益

寄生电阻(如晶体管源极/漏极接触电阻、金属连线电阻)会引入额外的压降,降低有效输出电压。对于放大 器,增益通常表示为_A__v_=_g__m_⋅_R_out,其中_R_out 是输出阻抗。若寄生电阻 _R_parasitic 与负载串联,总输出阻抗 _R_out 可能增加,但实际增益会因分压效应而降低。

- 带宽

寄生电阻与节点寄生电容结合,形成低通滤波器,增加时间常数 τ=R⋅C_τ_=R_⋅_C,从而降低带宽

-

寄生电容

- 延迟

信号延迟主要由充电/放电时间决定,即_t_delay∝_R_⋅_C_。寄生电容(如导线间耦合电容_C_coupling、栅极电容_C_gate)会增加总负载电容,延长信号跳变时间。

- 减小寄生参数的方法

-

减少寄生电容

-

缩短互连线长度:电容与导线长度成正比,缩短走线可显著降低电容。

-

避免平行长走线:平行导线间的耦合电容与重叠面积成正比,采用正交布线或增加间距以减少耦合。

-

使用低介电常数(low-k)介质层:先进工艺中采用低k介质隔离金属层,降低层间电容。

-

屏蔽技术:在敏感信号线两侧布置接地屏蔽线(guard ring),隔离耦合干扰。

-

-

降低寄生电阻

-

增加金属线宽度:电阻与线宽成反比,但需权衡与电容的增大。

-

使用高层金属层:高层金属通常更厚,电阻更低,适合全局布线。

-

多孔接触(Via阵列):在晶体管源/漏极接触区使用多个接触孔(contact/via),减小接触电阻。

-

-

优化器件布局

-

对称布局:在差分对或电流镜中采用对称结构,抵消寄生参数的失配影响。

-

多指晶体管(Finger Layout):将大尺寸晶体管拆分为多个并联的小晶体管(fingers),减少栅极电阻和寄生电容。

-

Dummy结构:在版图边缘添加虚拟器件(dummy devices),确保刻蚀均匀性,减小工艺波动导致的寄生差异。

-

-

仿真与迭代优化

-

寄生提取(Parasitic Extraction):使用EDA工具(如Calibre)提取版图寄生参数,结合后仿真验证性能。

-

迭代调整:根据仿真结果调整走线路径、器件间距或层分配。

-

总结

本次实验通过反相放大器的版图设计与后仿流程,系统掌握了从版图绘制到寄生参数分析的完整流程。关键要点包括:

-

版图设计需严格遵循DRC规则,合理规划金属层与通孔连接。

-

寄生参数抽取必须基于通过LVS验证的版图,否则结果不可靠。

-

后仿结果与前仿差异反映了版图布局对电路性能的实际影响,为后续优化提供了依据。

-

实验中文件路径与命名规范(如calibreview)需严格遵守,避免多人协作时的冲突。