嵌入式学习---(ARM)

1、什么是RISC、CISC;

CISC (Complex Instruction Set Computer - 复杂指令集计算机):通过硬件完成复杂功能。它的目标是用一条指令完成更多工作,从而减少程序所需的指令条数。指令系统庞大且复杂,指令长度可变,执行时间也长短不一。

RISC (Reduced Instruction Set Computer - 精简指令集计算机):通过精简指令优化执行速度。它的目标是让每条指令都非常简单、执行速度快(通常一个时钟周期),从而通过提高指令的执行效率来提升性能。指令系统小巧而精简。

2、冯.诺伊曼架构和哈佛架构有何区别?ARM内核属于哪一种?

冯·诺伊曼架构:共享一条总线用于传输指令和数据。指令和数据存放在同一个存储器中。

哈佛架构:使用分离的两条总线,一条专门用于传输指令,另一条专门用于传输数据。指令和数据通常存放在两个独立的存储器中。

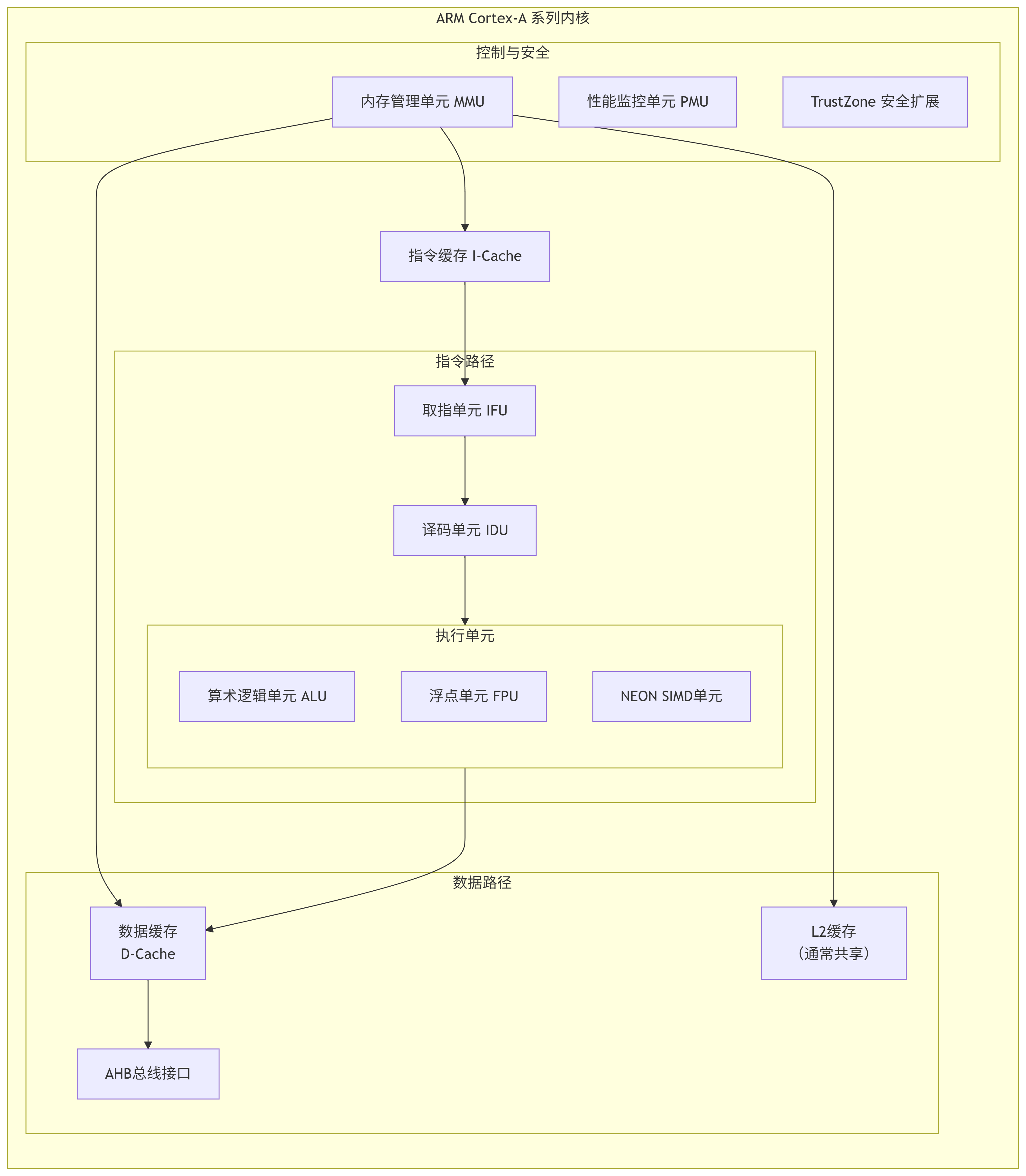

3、ARM内核中都有什么?

ARM内核是一个SoC(片上系统)中的计算核心

4、ARM有几种工作模式?

| 特性 | Cortex-A (应用处理器) | Cortex-M (微控制器) |

|---|---|---|

| 核心设计目标 | 运行复杂操作系统,支持虚拟内存 | 实时性,低功耗,确定性响应 |

| 模式划分依据 | 异常类型(中断、中止、未定义等) | 特权等级(特权级 vs. 非特权级) |

| 模式数量 | 7种 | 2种(线程模式、处理器模式) |

| 关键模式 | 用户模式(非特权)、管理模式(SVC,特权) | 特权级线程模式、非特权级线程模式 |

| 典型应用场景 | 智能手机、平板、服务器(Linux, Android) | 物联网设备、智能手表、电机控制(FreeRTOS, Zephyr) |

5、什么是异常向量表?

异常向量表(Exception Vector Table) 是一个预先定义在内存特定位置的查询表,其中存储了各种异常和中断处理程序的入口地址(指针)。当CPU遇到异常或中断时,会自动“查表”并跳转到对应的地址去执行处理代码。

lr(link register):链接寄存器

pc(program counter):程序寄存器:存放下一条要执行的指令的内存地址

一般会通过lr和pc共同协作来完成cpu的跳转,便于回到跳转前的地址以及过程中的一系列保护现场和恢复现场的功能