新手入门Makefile:FPGA项目实战教程(二)

新手入门 Makefile:FPGA 项目实战教程(二)

系列文章目录

1、VMware Workstation Pro安装指南:详细步骤与配置选项说明

2、VMware 下 Ubuntu 操作系统下载与安装指南

3、基于 Ubuntu 的 Linux 系统中 Vivado 2020.1 下载安装教程

4、利用 Makefile 高效启动 VIVADO 软件:深入解析与实践

5、新手入门 Makefile:FPGA 项目实战教程(一)

引言

在上一篇5、新手入门 Makefile:FPGA 项目实战教程(一)文章中,介绍了大概的项目结构和基础知识内容,接下来这一章我们将结合实际的工程。

文章目录

- 新手入门 Makefile:FPGA 项目实战教程(二)

- 系列文章目录

- 引言

- 四、Makefile 在 FPGA 项目中的基本应用

- 4.1 简单的 FPGA 项目 Makefile 示例

- 4.2 Tcl 脚本在 Vivado 中的作用

- 4.2.1 项目管理命令

- 4.2.2 文件管理命令

- 4.2.3 综合命令

- 4.2.4 实现命令

- 4.3 完整的 Tcl 脚本示例

- 4.3 执行 Makefile 命令

- 4.4 并行执行和性能优化

- 未完待续。。。。

四、Makefile 在 FPGA 项目中的基本应用

4.1 简单的 FPGA 项目 Makefile 示例

下面是一个简单的 Makefile 示例,用于编译一个 LED 闪烁的 FPGA 项目:

# 定义项目参数

PROJECT_NAME = led_blink

FPGA_PART = xc7a100tfgg484-2

SRC_DIR = ./src/rtl

CONSTRAINTS_DIR = ./src/constraints

TCL_SCRIPT = ./scripts/build_project.tcl

OUTPUT_DIR = ./output# 默认目标,执行所有步骤

all: create_project add_files synth impl bitstream# 创建Vivado项目

create_project:@echo "Creating project..."vivado $(VIVADO_OPTS) -source $(TCL_SCRIPT) -tclargs create_project $(PROJECT_NAME) $(FPGA_PART)# 添加源文件和约束文件

add_files:@echo "Adding files..."vivado $(VIVADO_OPTS) -source $(TCL_SCRIPT) -tclargs add_files $(SRC_DIR) $(CONSTRAINTS_DIR)# 综合设计

synth:@echo "Synthesizing design..."vivado $(VIVADO_OPTS) -source $(TCL_SCRIPT) -tclargs synth# 实现设计

impl:@echo "Implementing design..."vivado $(VIVADO_OPTS) -source $(TCL_SCRIPT) -tclargs impl# 生成比特流

bitstream:@echo "Generating bitstream..."vivado $(VIVADO_OPTS) -source $(TCL_SCRIPT) -tclargs bitstream# 清理生成的文件

clean:@echo "Cleaning project..."rm -rf $(PROJECT_NAME).xprrm -rf $(OUTPUT_DIR)rm -rf reports

这个 Makefile 定义了几个基本目标:

-

all:执行所有步骤,从创建项目到生成比特流 -

create_project:创建新的 Vivado 项目 -

add_files:向项目中添加源文件和约束文件 -

synth:综合设计 -

impl:实现设计(包括布局布线) -

bitstream:生成比特流文件 -

clean:清理生成的文件和目录

这个 Makefile 定义了从项目创建到比特流生成的完整流程,每个步骤都对应一个独立的目标,你可以单独执行其中的任何一个步骤。

4.2 Tcl 脚本在 Vivado 中的作用

Tcl(Tool Command Language)是 Vivado 中使用的脚本语言,用于自动化各种设计流程。通过编写 Tcl 脚本,可以实现从项目创建到比特流生成的全流程自动化(58)。

Vivado 提供了两种执行 Tcl 脚本的方式:

-

交互式模式:在 Vivado GUI 的 Tcl 控制台中逐行输入命令。

-

批处理模式:通过命令行执行完整的 Tcl 脚本。

在 Makefile 中,我们主要使用批处理模式来执行 Tcl 脚本,以实现完全自动化的构建过程(59)。

以下是一些常用的 Vivado Tcl 命令,用于自动化设计流程:

4.2.1 项目管理命令

# 创建新项目

create_project -force $project_name $project_dir -part $part# 打开现有项目

open_project $project_path/$project_name.xpr# 保存项目

save_project# 关闭项目

close_project

4.2.2 文件管理命令

# 添加单个Verilog源文件

add_files -fileset sources_1 [list $src_file]# 递归添加目录下的所有文件

add_files -fileset sources_1 -recursive $src_dir# 添加约束文件

add_files -fileset constrs_1 $xdc_file# 设置顶层模块

set_property top $top_module [current_fileset]

4.2.3 综合命令

\# 综合设计synth\_design -top \$top\_module -part \$part\# 查看综合结果open\_run synth\_1report\_utilization -hierarchy -file \$report\_dir/utilization\_report.rpt

4.2.4 实现命令

# 优化设计

opt_design# 布局

place_design# 布线

route_design# 生成比特流

write_bitstream -file $output_dir/$project_name.bit

4.3 完整的 Tcl 脚本示例

下面是一个完整的 Tcl 脚本示例,用于实现从项目创建到比特流生成的全流程:

# 解析命令行参数

set args [argv]

set command [lindex $args 0]

set project_path [lindex $args 1]

set part [lindex $args 2]

set src_dir [lindex $args 3]

set constraints_dir [lindex $args 4]

set ip_dir [lindex $args 5]switch -- $command {"create_project" {# 创建项目create_project -force my_project $project_path -part $partset_property target_language Verilog [current_project]}"add_files" {# 添加源文件add_files -fileset sources_1 -recursive $src_diradd_files -fileset constrs_1 -recursive $constraints_diradd_files -fileset sources_1 -recursive $ip_dir# 设置顶层模块set_property top top_module [current_fileset]}"synth" {# 综合设计synth_design -top top_module -part $partreport_utilization -file $project_path/reports/utilization.rpt}"impl" {# 实现设计opt_designplace_designroute_designreport_timing_summary -file $project_path/reports/timing.rpt}"bitstream" {# 生成比特流write_bitstream -file $project_path/output/my_project.bit}default {puts "Unknown command: $command"exit 1}

}# 保存项目

save_project

这个脚本可以通过命令行参数接受不同的命令,实现灵活的流程控制(58)。

4.3 执行 Makefile 命令

要执行 Makefile 中的不同目标,可以使用以下命令:

# 执行所有步骤(从项目创建到生成比特流)

make all# 仅创建项目

make create_project# 仅添加文件

make add_files# 仅综合设计

make synth# 仅实现设计

make impl# 仅生成比特流

make bitstream# 清理项目

make clean

-

仅创建项目

make create_project

-

仅综合设计

make synth

-

仅实现设计

make impl

-

综合过程中资源的使用

-

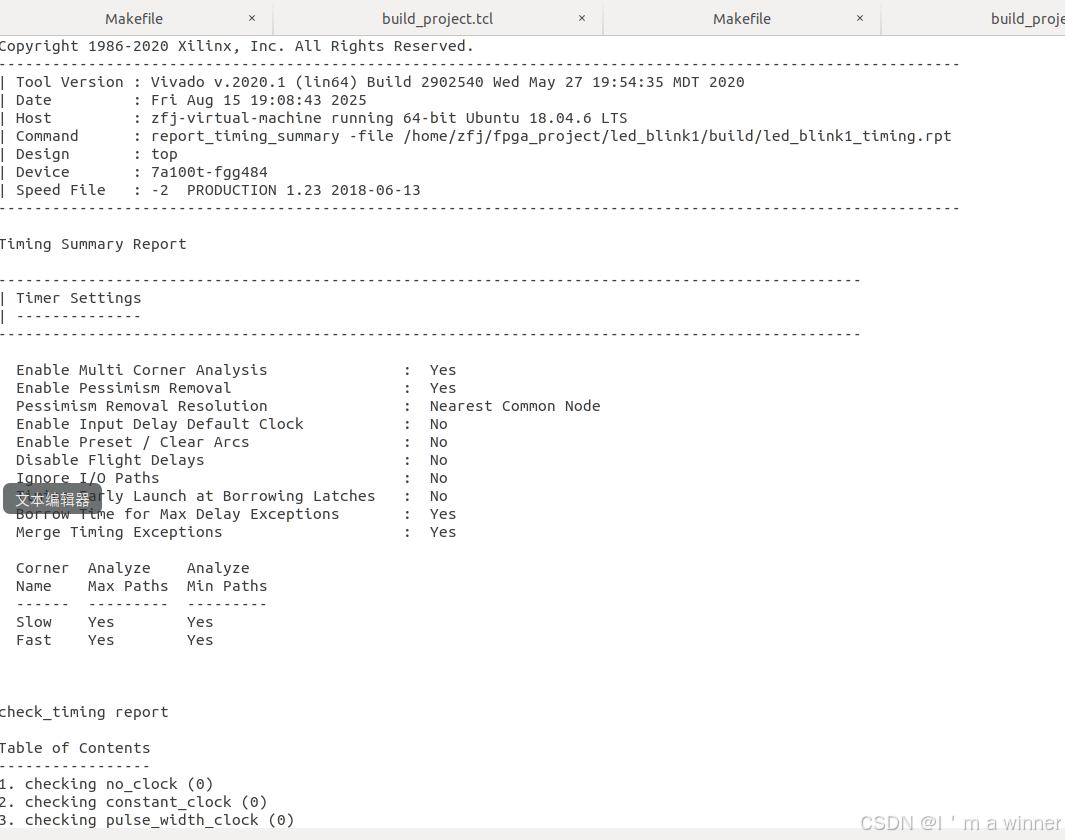

运行过程中生成的日志报告:

-

时序报告:

-

资源占用率报告:

这些命令将自动调用相应的 Tcl 脚本,实现全流程自动化。

4.4 并行执行和性能优化

为了加快综合和实现过程,可以使用 Vivado 的并行处理功能。在 Makefile 中,可以通过设置-jobs选项来指定使用的并行任务数:

# 综合设计(使用4个并行任务)

synth:@echo "Synthesizing design..."$(VIVADO) -mode batch -source $(TCL_SCRIPT) synth -jobs 4# 实现设计(使用8个并行任务)

impl:@echo "Implementing design..."$(VIVADO) -mode batch -source $(TCL_SCRIPT) impl -jobs 8

根据你的系统配置,可以适当调整并行任务数,以获得最佳性能(58)。

未完待续。。。。