关于时钟门控ICG的一切(与门及或门门控)

关于时钟门控ICG的一切(与门及或门门控)

- 0、前言

- 一、与门门控

- (1)一个与门

- (2)寄存器门控

- (3)锁存器门控

- 二、或门门控

- (1)一个或门

- (2)锁存器门控

- 三、为什么与门或门的使用和触发沿有关

- 四、门控的RTL实现及门控后电路变化

- (1)RTL写法

- (2)门控后电路变化

- 参考

时钟门控属于低功耗的范畴,是其中经常被问到的部分,甚至被面试官问过或门能不能做门控,怎么做。不过当时知识没有学到很深入,也没抽出时间再搜这个问题。

每次画门控的电路图基本都在死记硬背了,这次整理了门控的三种形式以及与门和或门的实现,它们分别对应于不同时钟沿的情况。

0、前言

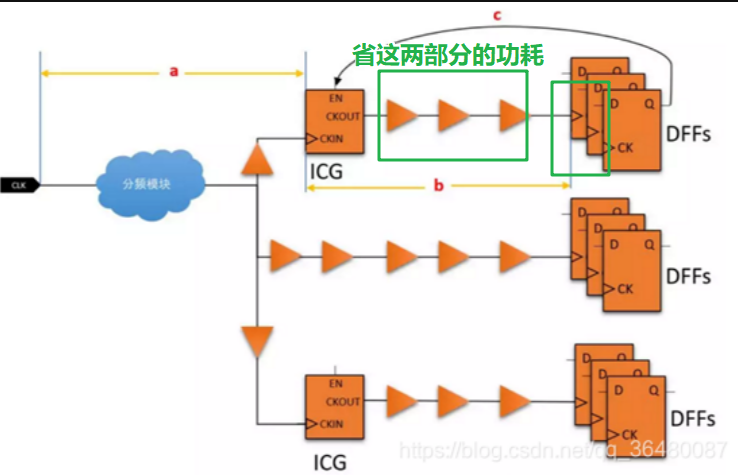

时钟门控(Clock Gating):通过在数据无效时关闭寄存器的时钟来实现有效减少动态功耗,最主要降低的是寄存器的动态功耗(时钟翻转的功耗)和时钟树功耗。(注意FF的数据本身就是不变了才能做门控,所以没有数据变化的不同)

对于与门和或门门控有这样一个规则:

| 对clk上升沿触发的FF,使用与门进行门控,信号只在时钟的低电平区变化(也就是用~clk接锁存器)。 clk下降沿触发的FF,使用或门进行门控,信号只在时钟的高电平区变化。 |

|---|

原因后续会讨论,先来看常说的与门门控。

一、与门门控

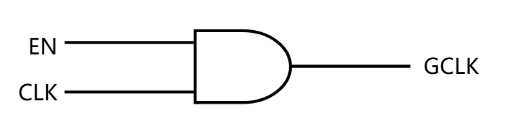

(1)一个与门

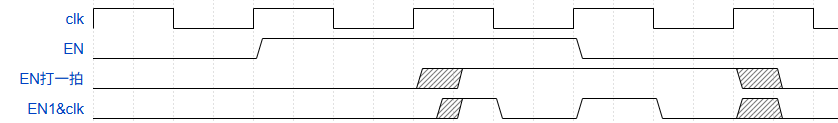

最简单的就是与门实现,EN=0就不输出时钟,1就输出。

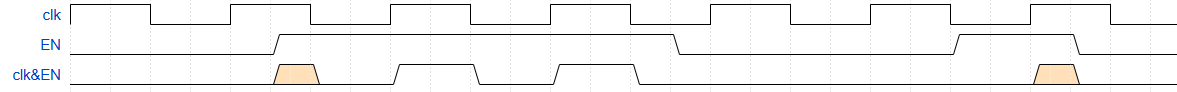

这里问题很明显,就是没法保证EN对齐时钟,会有毛刺:

(2)寄存器门控

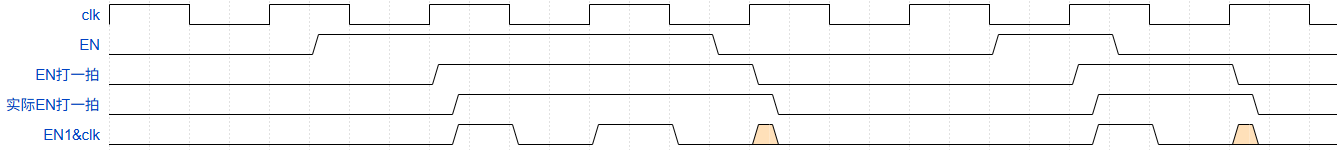

针对上面的问题,我直接能想到的解决方式就是把EN打拍,打一拍不就能够对齐时钟沿了嘛!

直接看图好像没啥问题,但是这里有两个问题没考虑:1是采样到EN边沿造成亚稳态的情况,2是与门两个输入的延迟不一样,一个输入直接是clk,延迟很小,另一个是EN采样后的输出,延迟相对大。

1、采样到亚稳态时:

亚稳态会直接影响到输出

2、clk2q有实际延迟

延迟的部分会和下一级的时钟正半周期相与,导致出现毛刺。

所以用寄存器直接打拍会有问题。

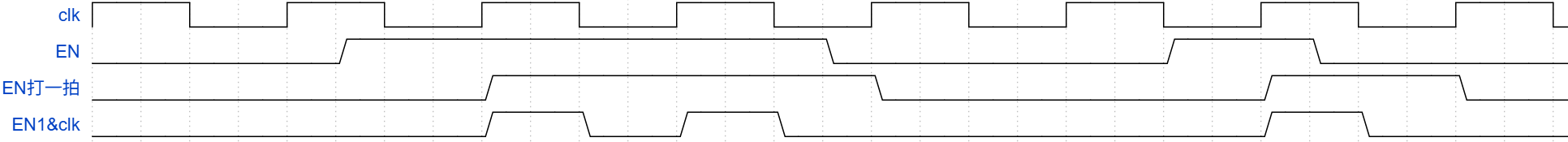

可以发现问题都是出现在clk的正半周期,而实际的延迟和亚稳态的持续时间都很短,如果错位半个周期那么做与运算的就不是clk=1而是clk=0的时候了,也就没有上述问题。

用下降沿采样就可以实现,也就是实际寄存器门控的实现方式:

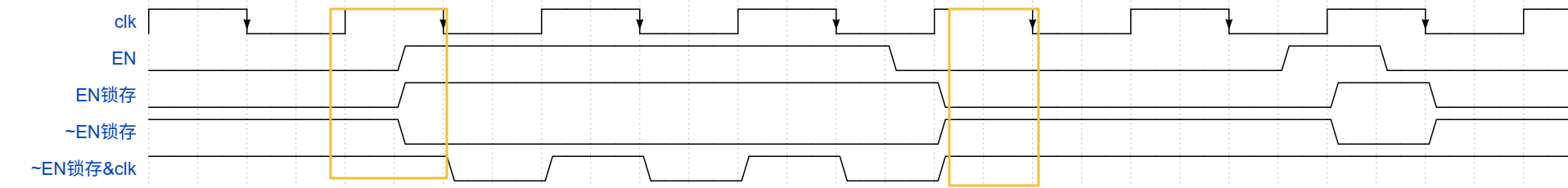

波形图如下:

因为采样前后均对应clk=0,所以即使有延迟或一点亚稳态也不会影响最终结果。

(注意:1、clk2q的延迟问题触发器可以完全解决,因为EN被clk下降沿打一拍之后变化一定在clk的下降沿,实际延迟后也一定位于clk=0的部分,但是后面锁存器门控不能完全解决。

2、对于亚稳态问题,两者不能完全保证解决。毕竟单bit信号CDC要打两拍,这里EN可以打两拍之后再传过来)

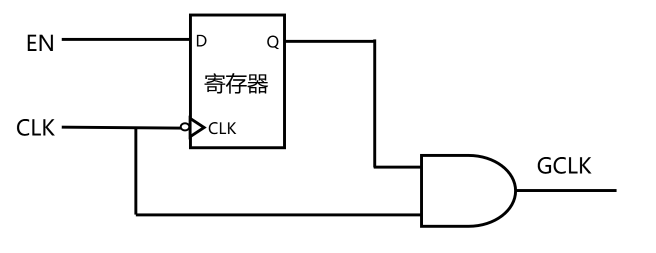

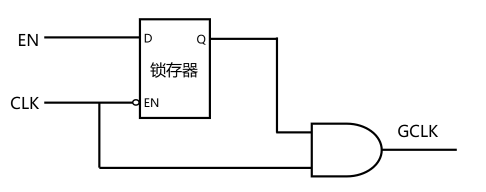

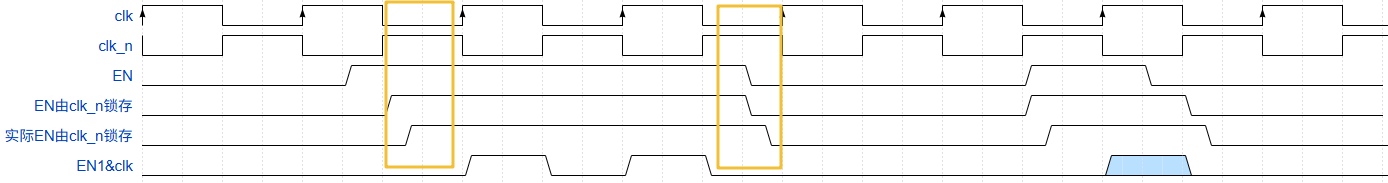

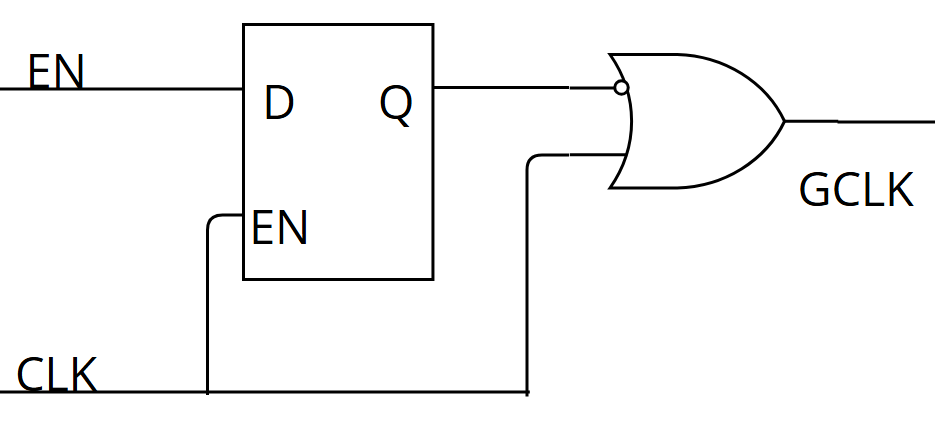

(3)锁存器门控

实际用的最多的是锁存器门控,因为寄存器由两个锁存器组成,面积更大。一般在公司锁存器门控都封装好可以直接调用。

具体设计其实就是把上面的FF换成latch:

波形图:

锁存器本身是电平触发,1的时候输出随输入变化,0的时候不变。

锁存器本身是电平触发,1的时候输出随输入变化,0的时候不变。

因为加了反相器,所以锁存器在clk=0的时候会输出变化的EN,1的时候保证状态不会变化,缓解了上面提到的两个问题。(对于clk2q的延迟问题,如果EN上升沿在clk=0的末端,经过延迟之后EN仍然有可能出现第一个clk周期不足或者毛刺。但因为会做成标准单元,对延迟进行控制,这个问题就不需要我们考虑了)

| 之前画门控的时候经常搞不清楚与门和latch的关系,其实只要明白是因为EN不对齐时钟沿所以需要对其打拍/锁存即可(注意用下降沿),锁存后的输出再和clk相与。 |

|---|

那上面的方式用做下降沿触发的FF的clk门控不行吗?我认为可以,毕竟就看锁存器的与门实现,里面只涉及时钟的高电平和低电平,和触发沿无关。

为什么下降沿或或门这里先按下不表,先看或门门控的实现。

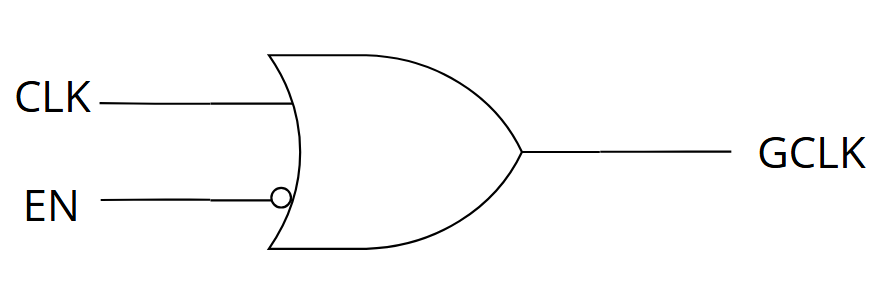

二、或门门控

(1)一个或门

既然用或门做控制,那输入1的时候输出就恒为1,输入0输出才是clk,但常规的说法都是EN=1的时候传输时钟,所以给EN取反了:

很明显的问题也是有毛刺。

和与门明显的不同是或门的门控在时钟不导通的时候始终为高电平,所以第一个沿是下降沿。

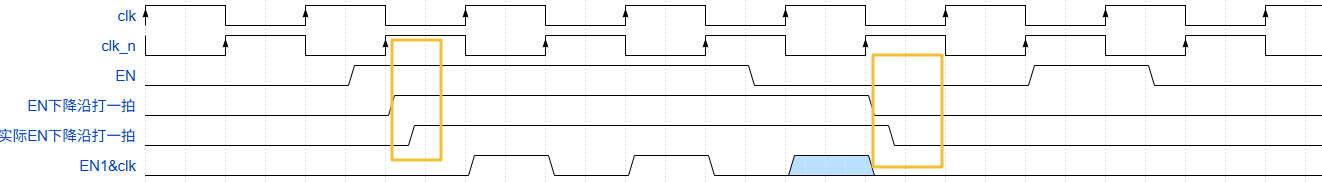

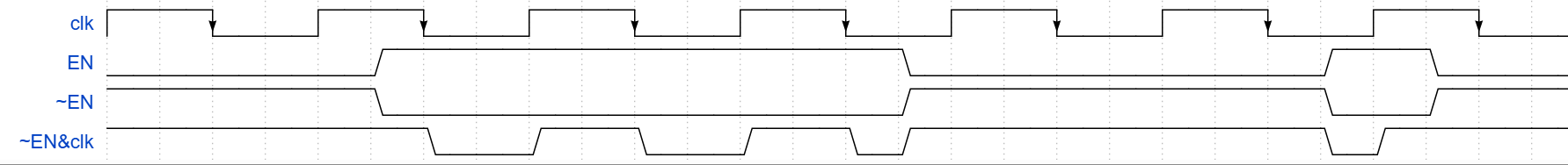

(2)锁存器门控

触发器类似,这里直接说锁存器。

锁存器是clk=1的时候透明,所以clk=1的时候锁存到亚稳态或者有延迟都没关系,因为和clk=1或完之后都是1。锁存完的输出记得取反。

类似的原理,两边虽然都有亚稳态和延迟问题,但都比较安全。

三、为什么与门或门的使用和触发沿有关

这个问题我目前没有找到官方回答。

我认为其实可以混用,只是用对应了会更有效率,更好。

可以看到与门门控在关闭的时候输出一直为0,打开后的第一个沿为上升沿;或门门控在关闭的时候输出一直为1,打开后的第一个沿为下降沿。问题就在这第一个沿上。

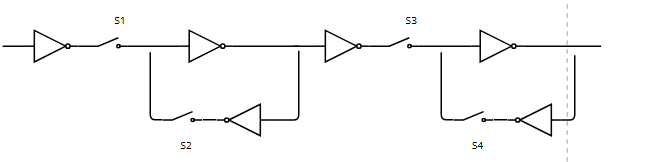

这里涉及到触发器的内部结构和采样原理,以上升沿触发的FF为例,采样过程如下:

clk=0时 s1 s4关闭,s2 s3打开,从锁存器维持原本状态,新状态进到主锁存器中;

clk=1时 s2 s3关闭,s1 s4打开,新状态在主锁存器中维持并输出;

如此循环…

对于上升沿触发的FF,clk=0时主锁存器的的s1关闭,信号可以直接进入主锁存器,当clk=1时遇到上升沿就直接采样到新状态然后输出了。如果采用或门门控的形式,则门控过程中clk一直为1,主锁存器一直维持着一个从前的状态,然后clk=0,新状态才进入主锁存器,比起第一个沿是上升沿的与门门控浪费了时间。(浪费多少应该和变化沿有关)

看起来这点延迟很少,但可能工具自动插了很多门控。

四、门控的RTL实现及门控后电路变化

门控可以在代码直接调用标准单元,或者让综合工具自动插入。

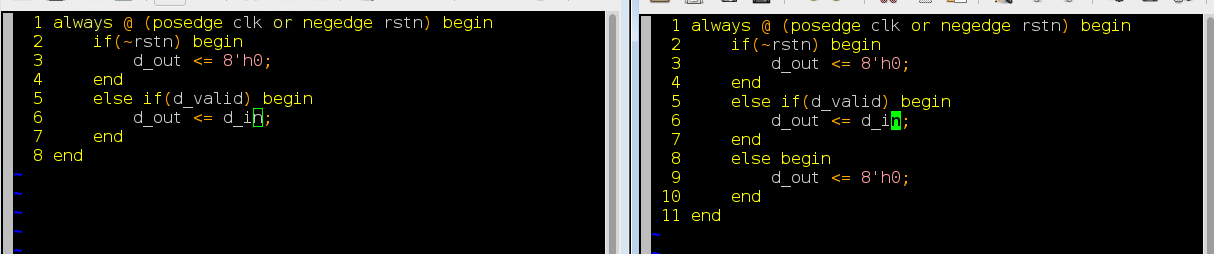

(1)RTL写法

但不是所有的写法都能插入门控,比如下面代码左边可以插入门控,右边就不行。因为门控是把时钟关了,需要保持数据不变,只有A<=A这种才能用门控。所以把数据设成0并不能减少功耗,要保持不变减少toggle才能降低功耗。

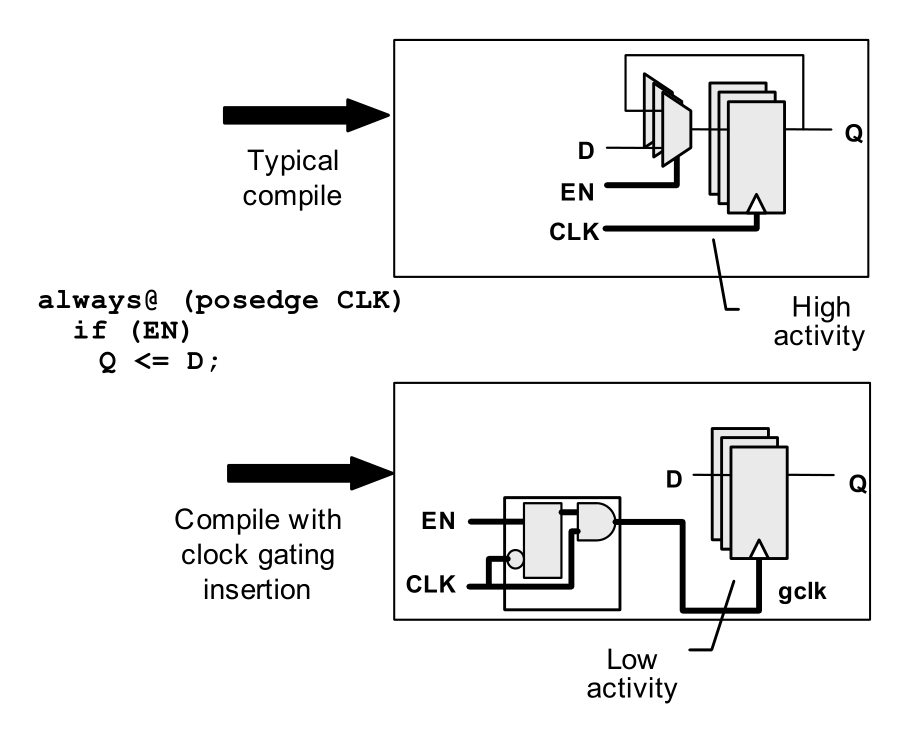

(2)门控后电路变化

插入后不再需要MUX(很多个),所以面积有可能减小。

如果D是单bit信号,节省的功耗就比较少,可能插入的CG面积还比原来的MUX大很多,而bit数越多就越划算。

那么这个临界值是多少呢?不同的工艺可能不一样,但是DC给的默认值是3。如果D的位宽超过了3bit,那么DC就会默认插入CG。

参考

数字设计–门控时钟与时钟切换

门控时钟

上升沿与下降沿的门控时钟设计

intel推荐的时钟门控方法

画图网站:wavedrom